学习笔记:Altium Designer 23 STM32F407核心板四层PCB设计-第二篇

因为PCB的知识点相对零碎,在这里整理一下最近学习F4核心板四层PCB设计的一些基础知识点。以下内容纯粹是个人学习B站视频的学习记录。

因为PCB的知识点相对零碎,在这里整理一下最近学习F4核心板四层PCB设计的一些基础知识点。请注意,以下内容纯粹是个人学习B站视频的学习记录,本人也并非专业做硬件方向的,如有错误还请批评指正。

视频链接:https://www.bilibili.com/video/BV1uc411N7Ux?p=7&spm_id_from=pageDriver&vd_source=2f5b9dae8fd3f8218856aa94fdf59b4e,up主是PCB吉迷哥,在此鸣谢作者。

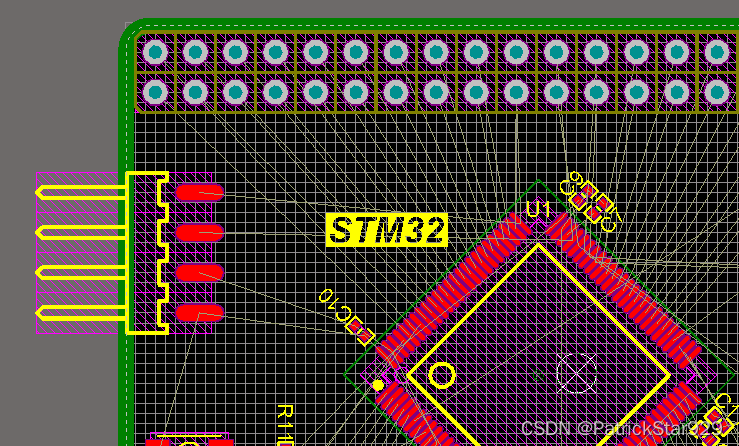

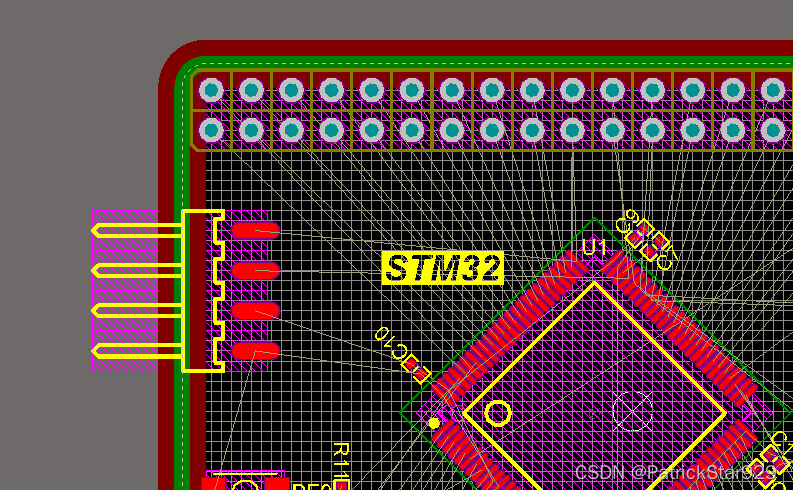

本贴的主要内容是四层板叠层设置、阻抗计算和规则设置(包括设置线宽线距规则和差分规则设置)。笔记接上回:

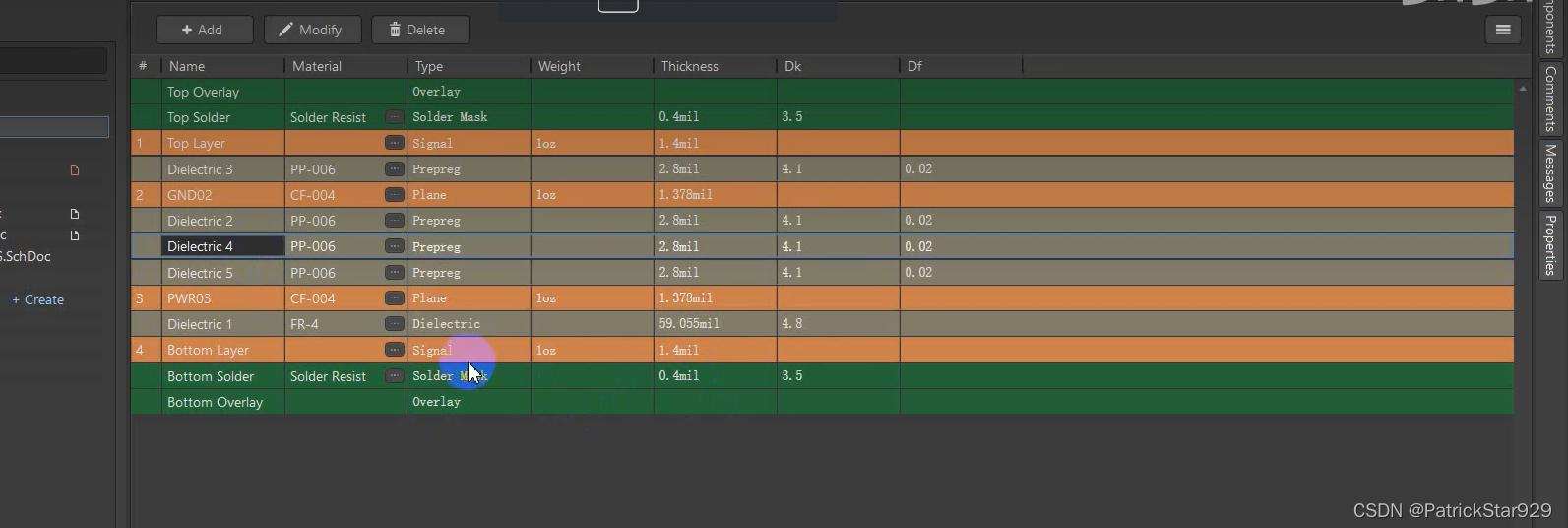

6.四层板层叠设置:video11

a.打开层叠设置的方法:设计–>层叠管理器;

b.按照PCB内层是否走信号线添加正片层或负片层:正片层又称信号层(signal),若多层PCB内层需走信号线请选择添加正片层(实际上,PCB的顶层和底层也都是正片层);负片层又称平面层(Plane),若多层PCB内层仅仅是电源和地层则选负片层。关于PCB正片和负片的区别可以参考PCB正片和负片的区别与使用。

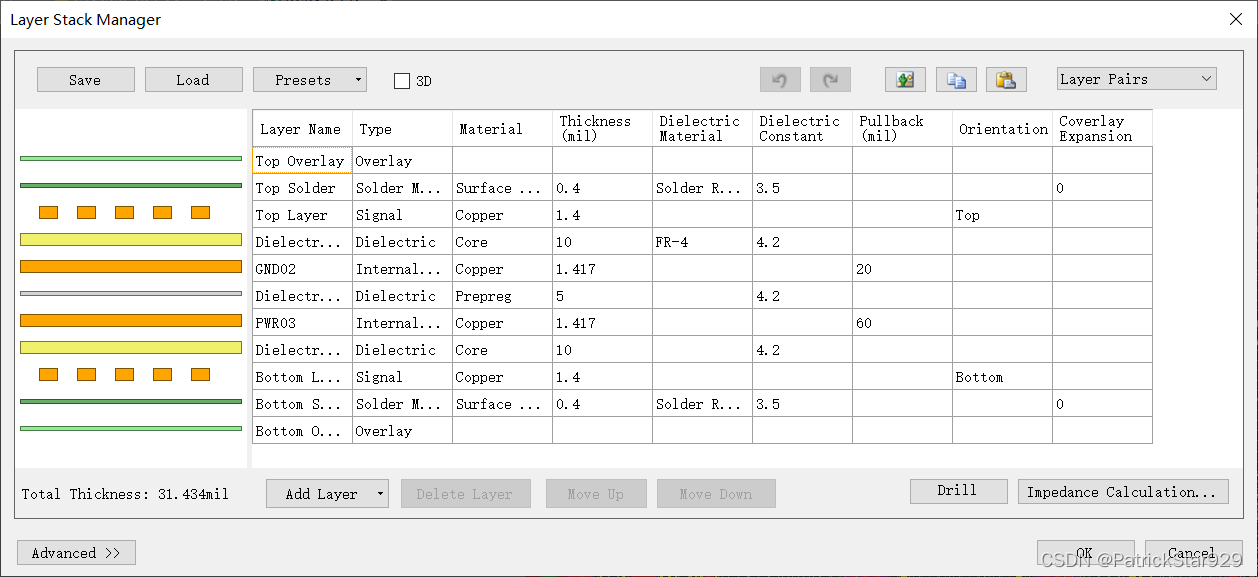

c.添加电源层和地层:在顶层(Top Layer)之下右键添加平面层,改名为GND02即地层。up主原话是因为顶层连接主芯片因此下面一层需要地层(或许是为了防干扰和便于接地?);在底层(Bottom Layer)之上添加平面层,改名为PWR03即电源层。如果需要仿真的话,则需按实际电路尺寸修改中间Dielectric介电层的层数、材料、厚度、介电系数等,不需仿真则可以不改。

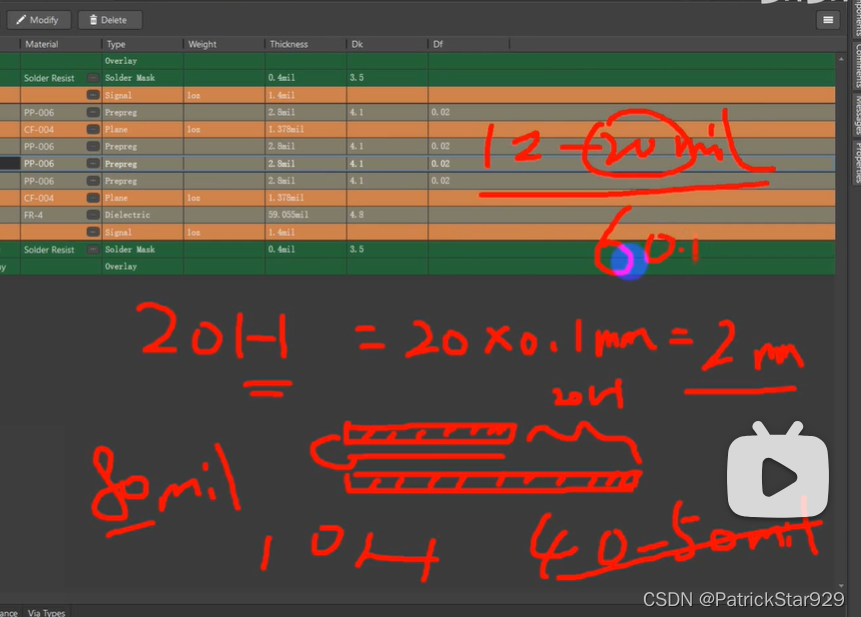

d.设置内缩满足20H的EMC规则:

一般而言,为使得设计满足EMC(Electro Magnetic Compatibility,电磁兼容)要求,四层PCB的两个平面层间(即电源层和地层间)的介电材料最低厚度H=0.1mm,且电源层需比地层内缩20H(即20×0.1mm = 2mm,约为80mil)。实际设计中取值为40~50mil即可。另外,地层需比板框内缩12 ~20mil。一个典型的设计是设置地层比板框内缩20mil,电源层比板框内缩60mil(即比地层内缩40mil)。课程视频截图如下:

设置内缩:

对于AD16.0,直接修改Pullback(mil)中的值即可。GND02层设置为20mil,PWR03层设置为60mil。

对于AD20,检查Properties属性框是具有Pullback distance选项。如果没有的话需先调出隐藏的Pullback distance选项(在顶部属性名称那一栏,右键 - Select columns,将 Pullback distance 改为可见。OK。),再在单击地层或电源层,调出Properties属性框进行设置,需注意设置内缩距离后要把Stack symmetry选项取消勾选,防止AD默认将负片层内缩设置值设置得一样。详细设置方式参考:Altium AD20的四层板叠层管理、平面层20H内缩

内缩前:

内缩后:

7.阻抗计算:video12

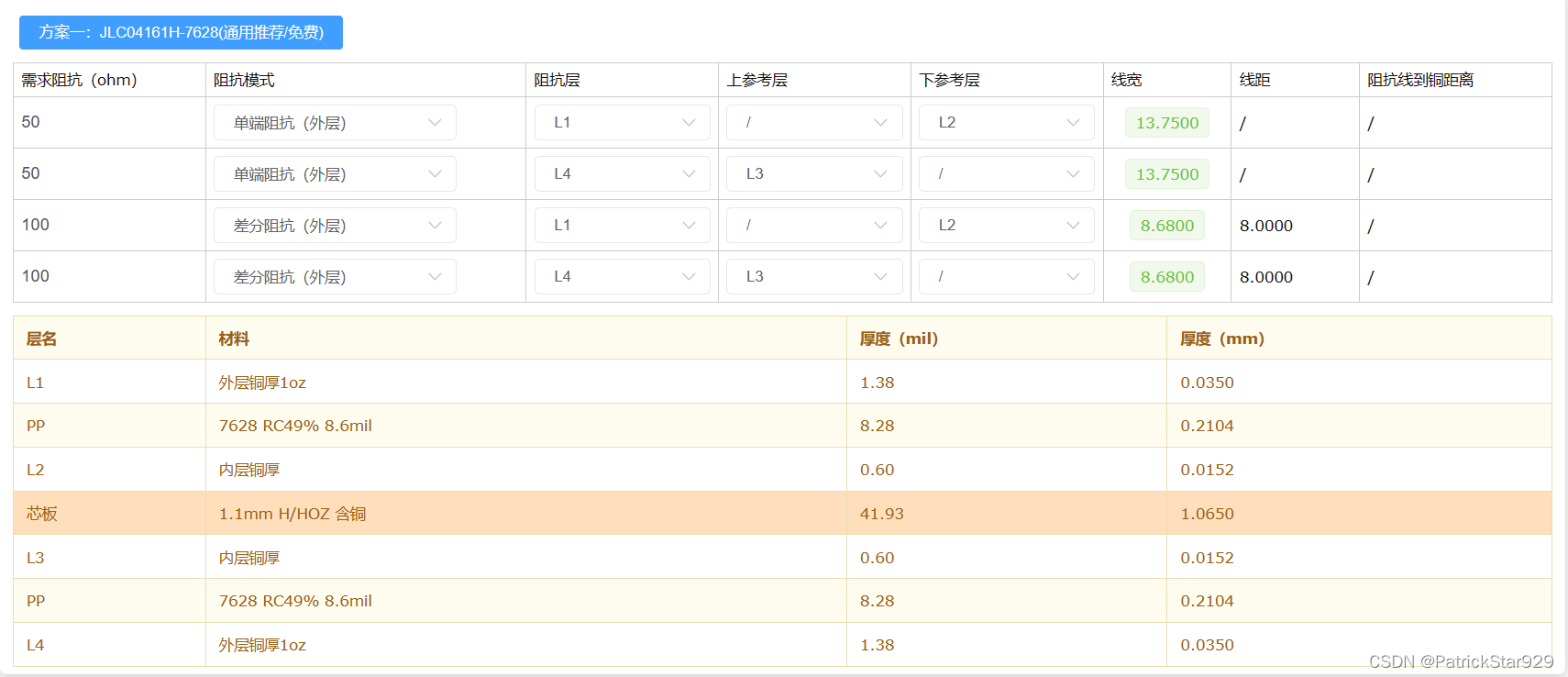

在设计多层板、高速板的时候需考虑阻抗匹配,以防止信号在驱动端、信号线、负载端之间的反射。一般单端线的特性阻抗为50Ohm,差分线为100Ohm,USB差分线为90Ohm。阻抗计算推荐使用嘉立创阻抗计算神器。

设置板子层数为=4,成品厚度=1.6,内层铜厚0.5oz,外层铜厚1oz,计算单位mil(全部按默认即可),分别设置L1和L4层的单端阻抗、差分阻抗分别为50和100Ohm,点击计算。

注意阻抗模式有四个选项,四层板阻抗设计选择单端阻抗和差分阻抗,双层板阻抗设计选择共面单端和共面差分阻抗。双层板阻抗设计参考:两层板如何做阻抗控制呢

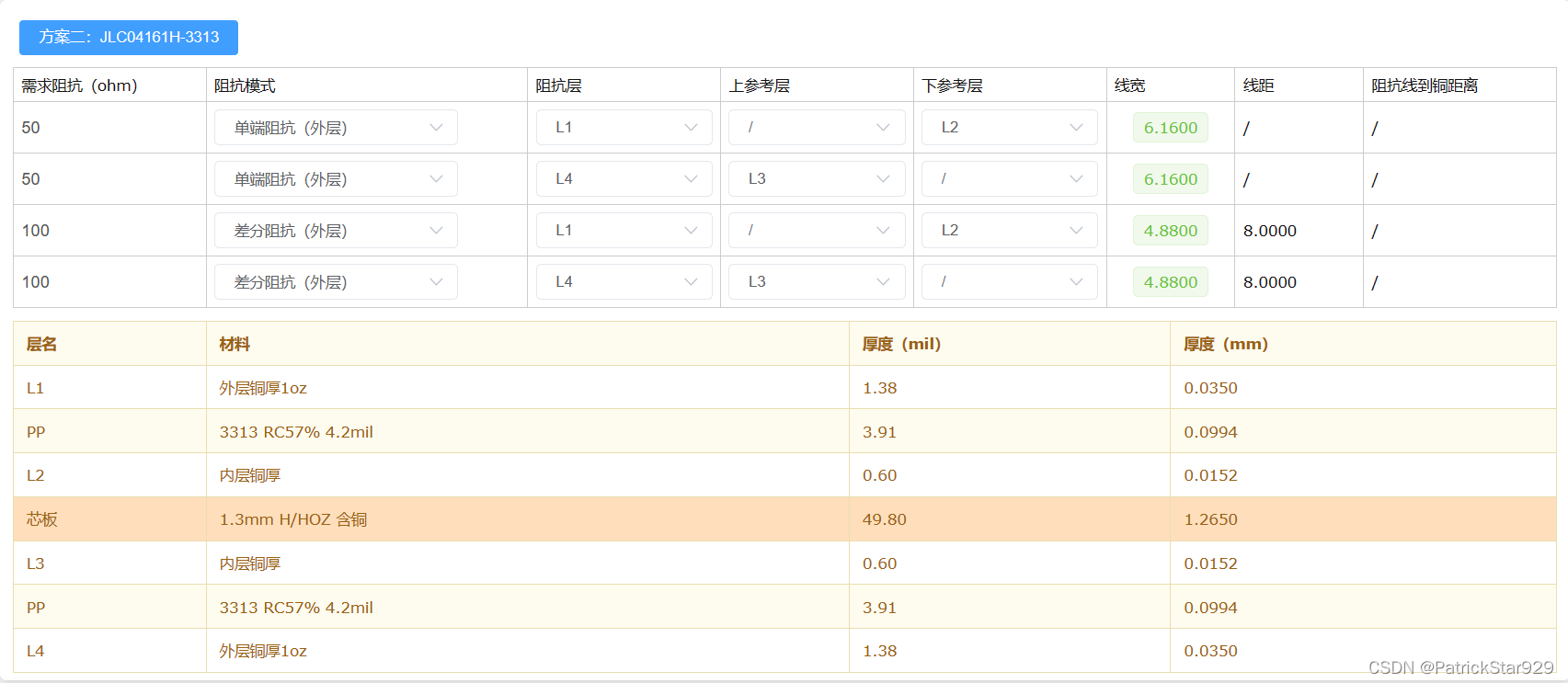

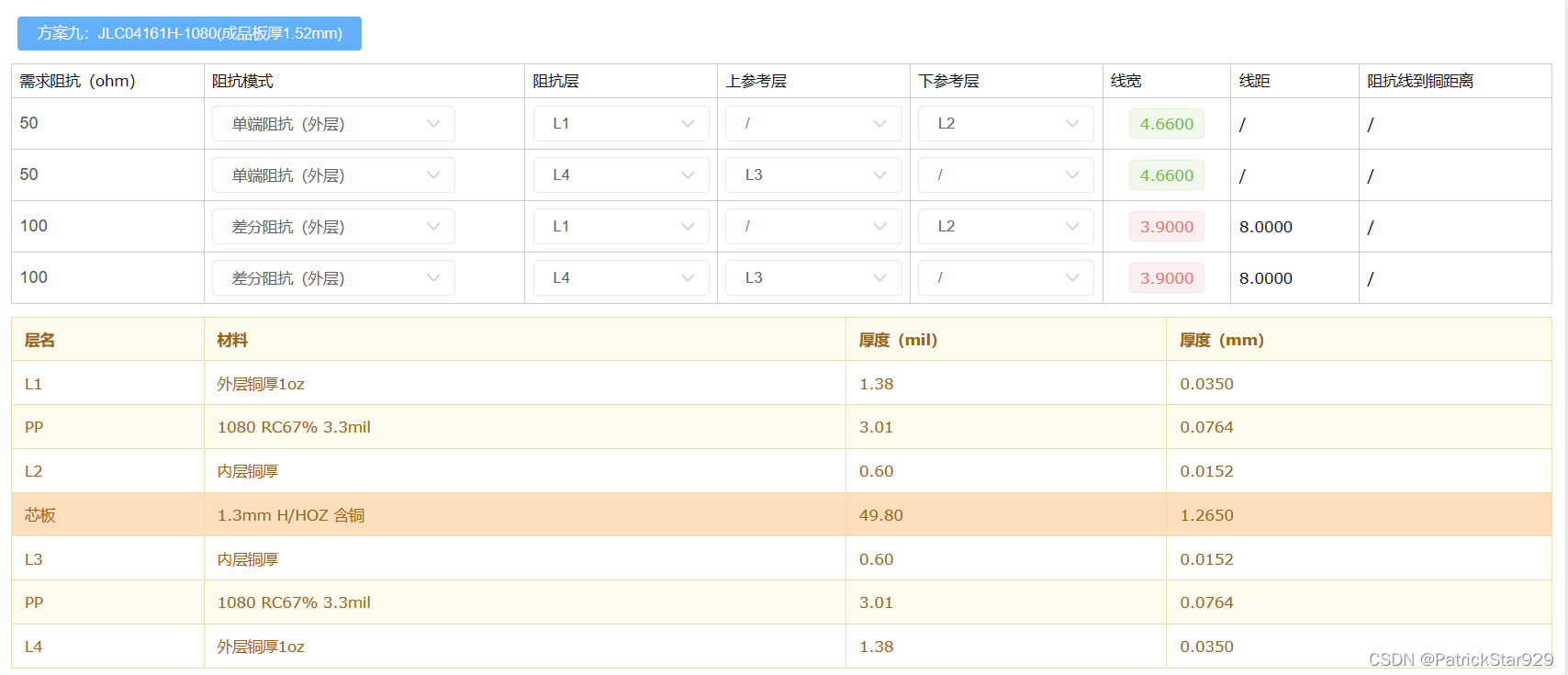

计算结果给出若干个参考方案,选择最小线宽>4mil的方案(保证工艺能制作得出来),最大线宽尽量不要太大,信号线线宽一般为8~12mil(为了走线方便点)。PCB常用走线宽度参考:PCB常用走线宽度,选择方案时还需考虑信号线的电流负载能力等。

例如,方案一嘉立创工艺可以做出来,并且是通用方案(尽管单端13.75线宽显得有一点大)

方案二线宽更合适

方案九最低线宽窄于嘉立创的工艺极限,无法制作。

选择某一合理的阻抗方案,修改AD软件叠层设计器重的各正片、负片层铜厚以及Core层、PrepregPP材料型号及厚度。

例如根据方案一的设置如图所示:(这个图以后再补,用的AD16没有太多材料的选项,建议使用视频中的AD20或立创EDA)

8.规则设置:video13 video14

8.1 设置线宽线距规则:

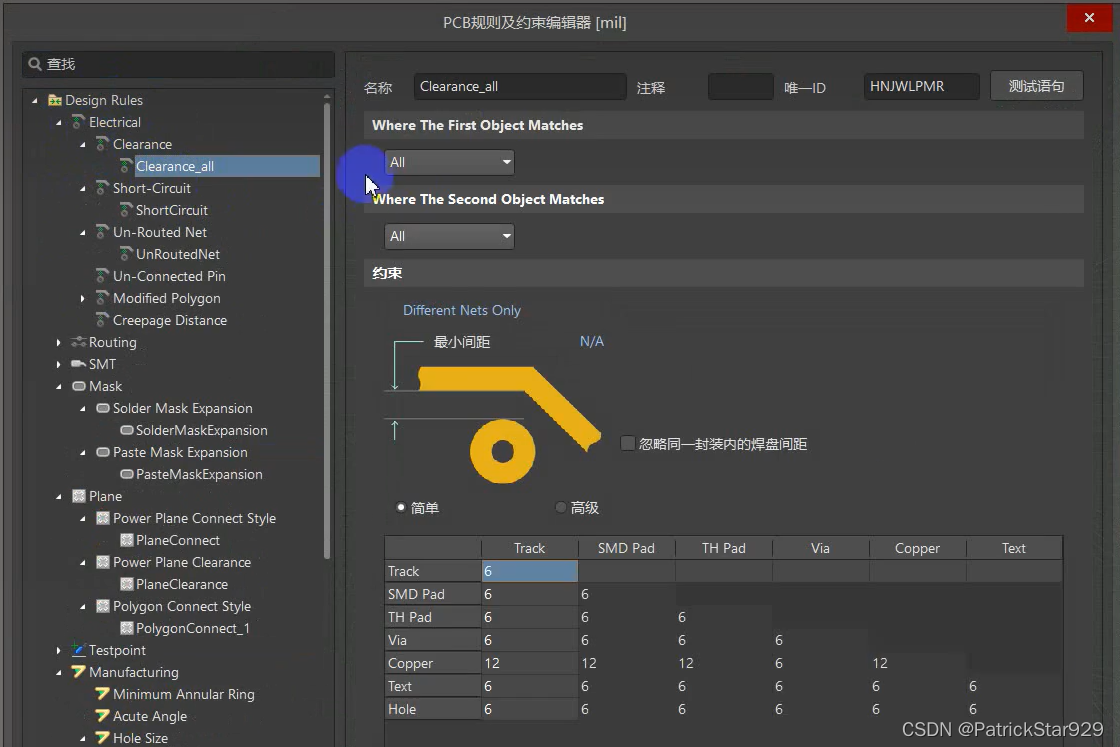

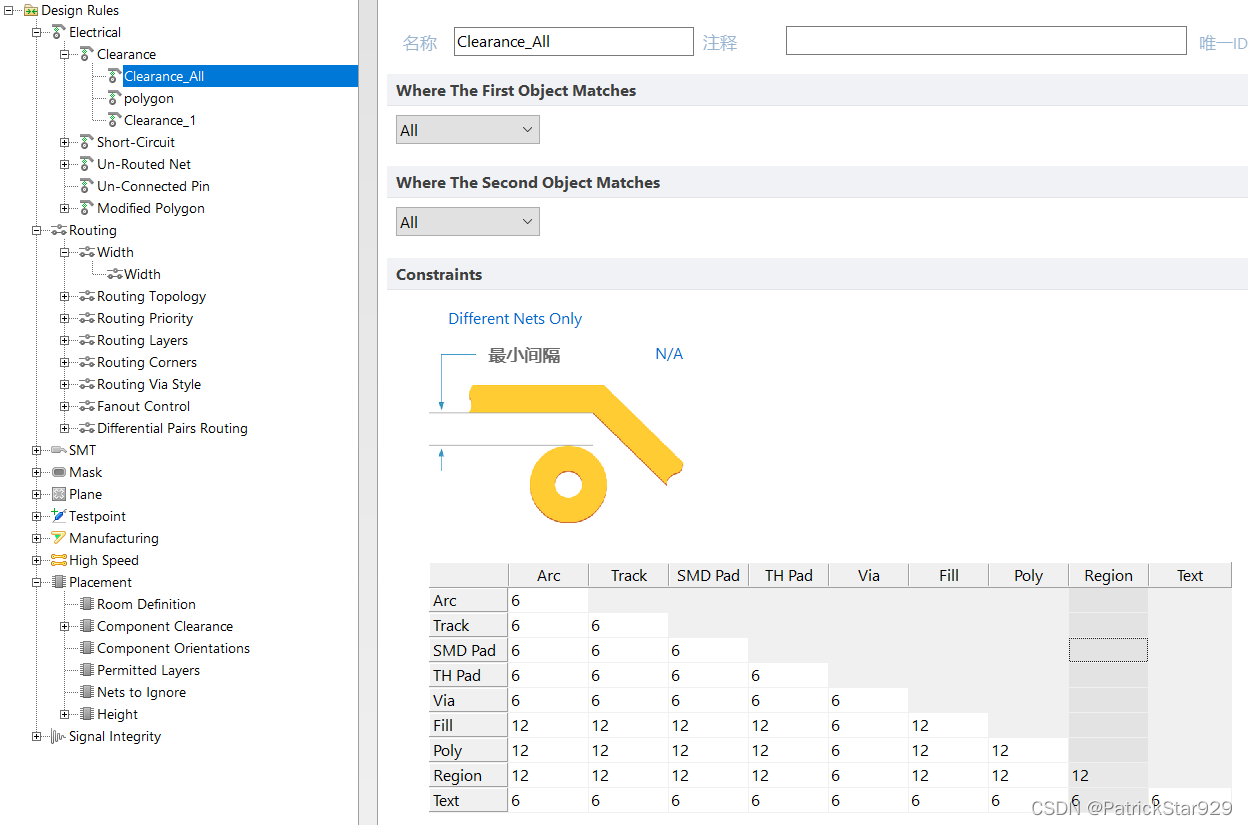

a.电气规则设置——安全间距: 设计—>规则—>Electrical(电气规则)—>Clearance(安全间距),选择一个安全间距规则或添加一个新的规则。

在AD20中可进行简单设置。按照up主的说法,没有BGA封装的板可以整板选择6mil,灌铜选择12mil,过孔选择6mil。先单击下方表格的左上角空位处全选并改成6mil,再单击Copper行标题将那一行改成12mil,最后单击Copper和Via的交叉处修改成6mil。最终设置结果如下所示:

在AD16中不能进行简单设置,其界面和设置结果如下(参考up主的参数,将涉及铜皮的部分都对应改了,不知是否正确):

相当于AD20中的选择高级时的选项。这里解释一下各个选项的含义:

Arc:圆弧 Track:走线 SMD Pad:表贴焊盘 TH Pad:通孔焊盘 Via:过孔 Fill:填充区块 Poly:覆铜

Region:区域 Text:文本 Copper:铜皮 Hole: 孔

其中Fill、Poly、Region都是铜皮,但用法不同,可以参考:Altium中填充fill、覆铜Polygon Pour、实心区域solid region的区别

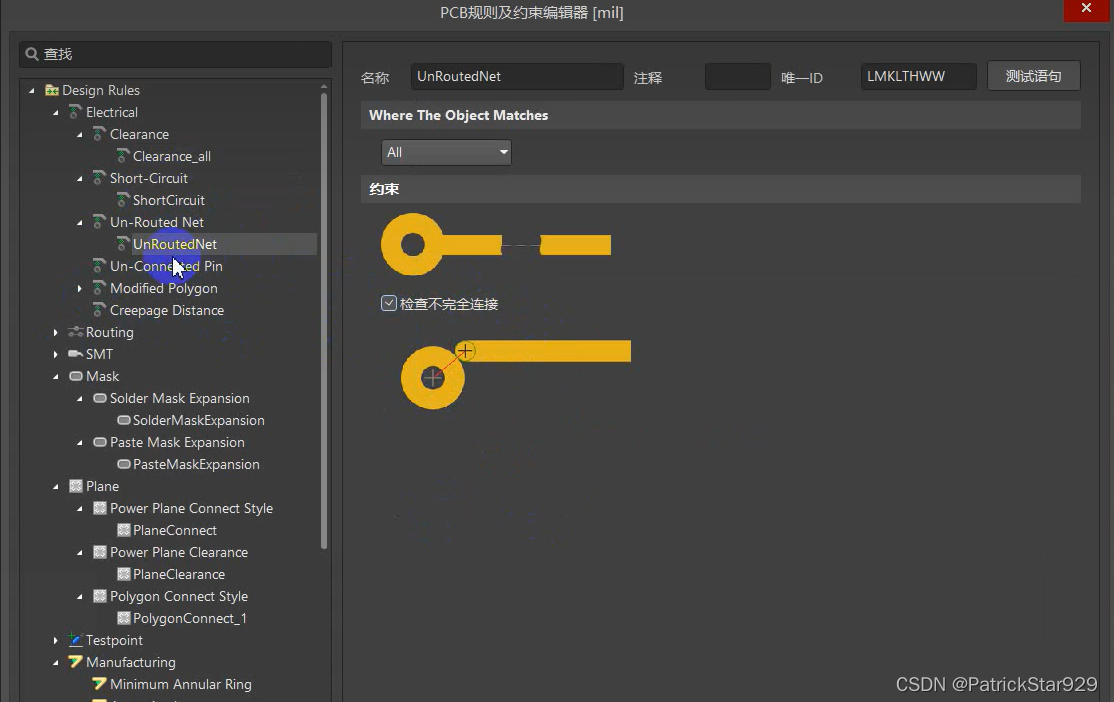

b.电气规则设置——检查不完全连接: 设计–>规则–>Electrical–>Un-routed Net,勾选检查不完全连接

c.走线规则设置——线宽

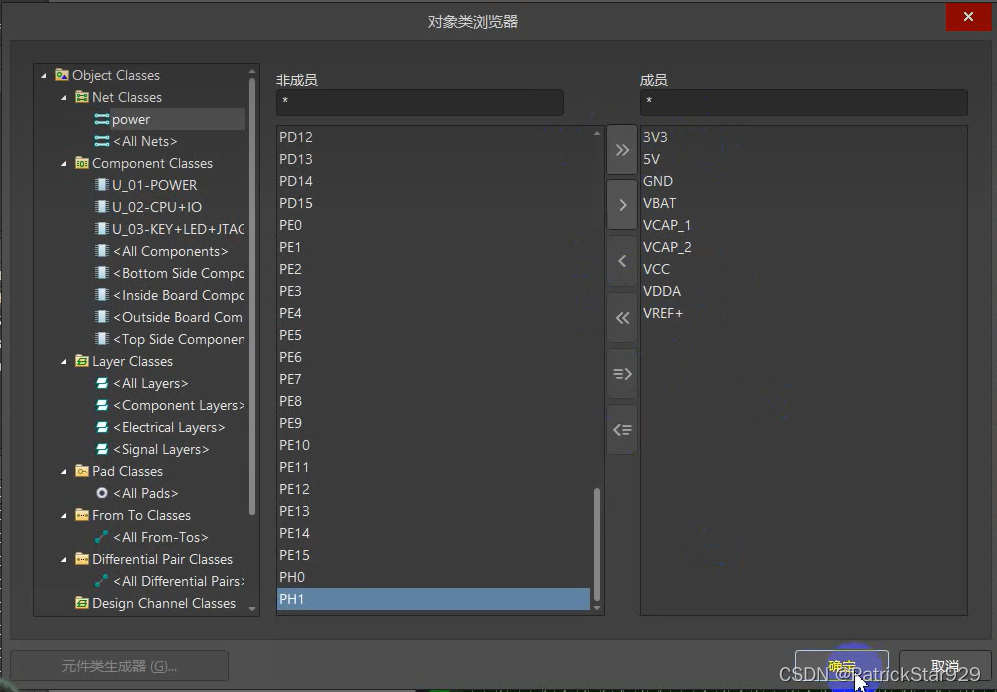

由于信号线和电源需要不同宽度的走线,因此在添加线宽规则前需先创建两个网络类(默认的类)和power类(电源网络),分别对不同类设置相应规则。步骤:设计–>类–>Net Classes,原先只有一个类表示所有网络,此时增加一个power类,把所有电源网络都添加进来,如下图所示将3V3、5V…VREF+这些都添加进来。

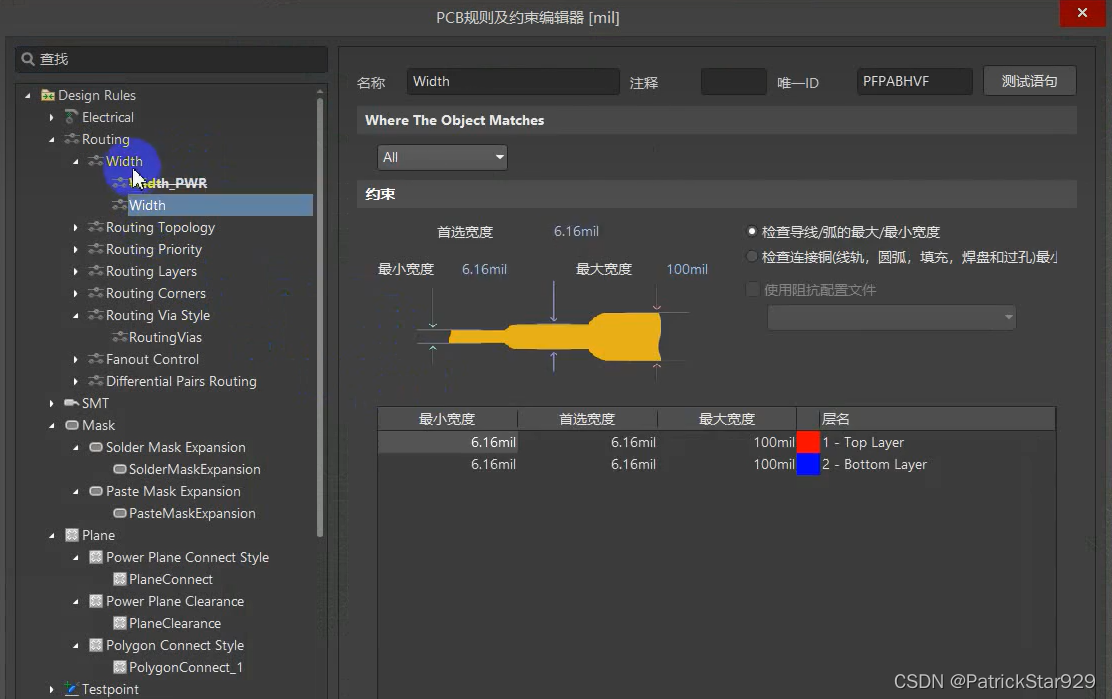

回到规则设置中,选择第一个规则,Where The Object Matches选择All。

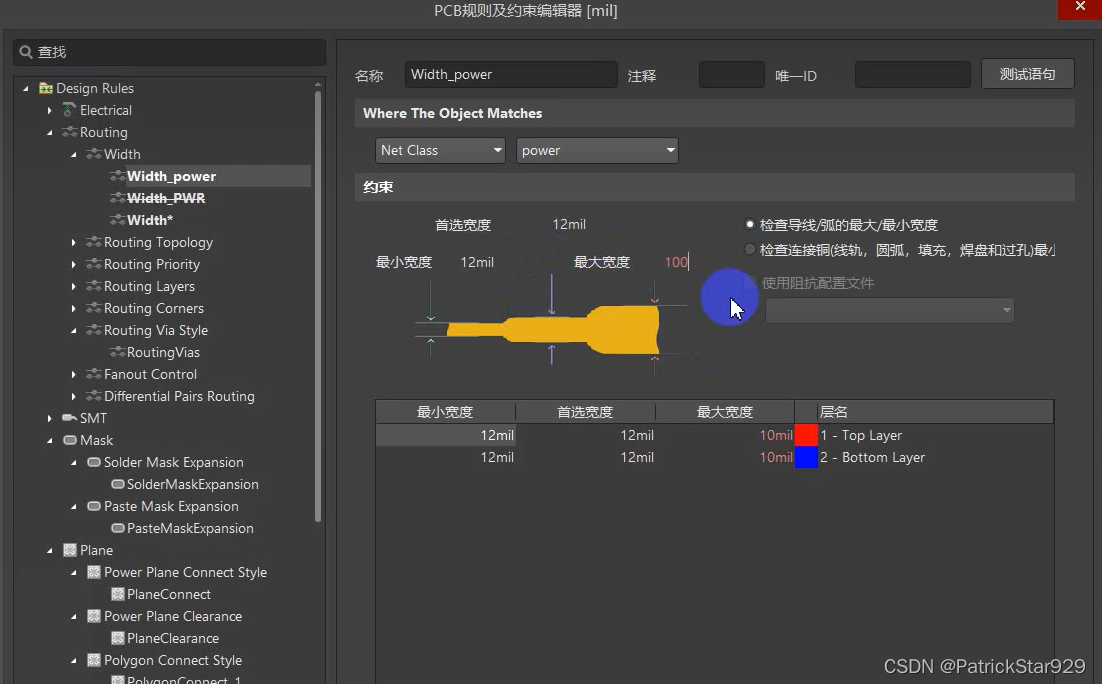

选择电源对应的规则Width_power,Where The Object Matches选择Net Class(将规则应用于某个网络类)和power。

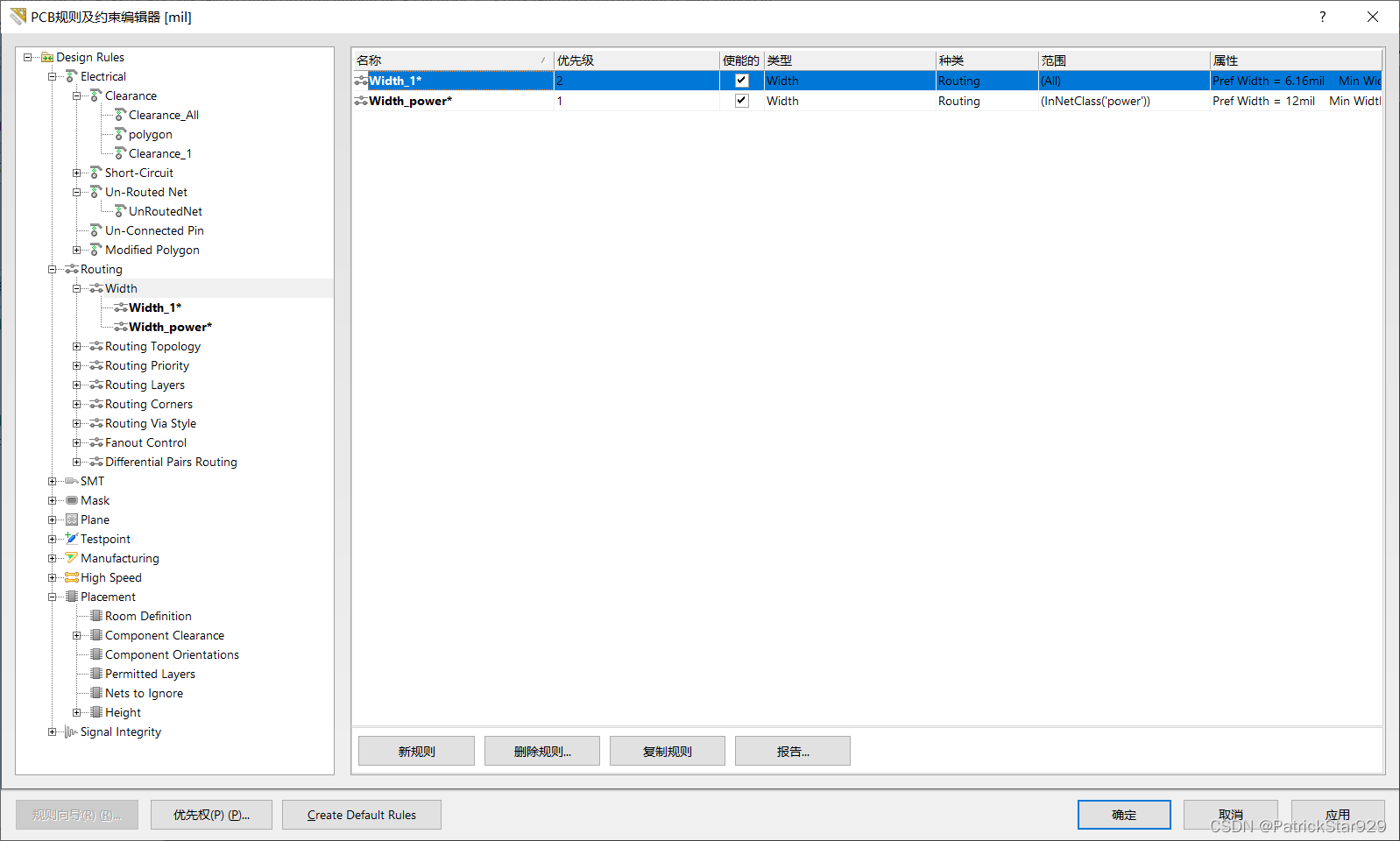

注——规则优先级:AD设计规则里面同一条目可建多条规则,比如间距,可建立多条规则。可是很多时候多条规则中包含了同一内容的设置,这时候以哪个为准呢?每条设置都有优先级,当有多条规则设置同一内容时,使用优先级最高哪一条规则。在这里,Width和Width_power都包含关于电源网络的规则,所以应该把Width_power优先级调成高于Width规则的优先级。左下角单击优先权按键,上下拖动两个规则即可调整优先级。

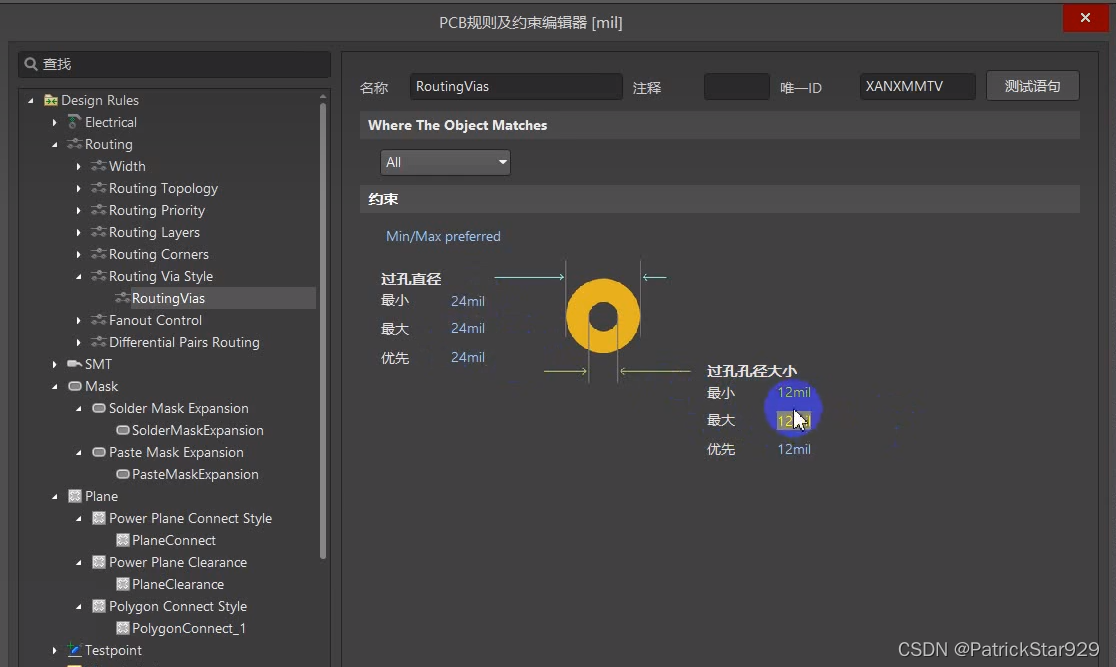

d.走线规则设置——过孔:

对于没有BGA芯片的板子,内径12mil外径24mil即可。

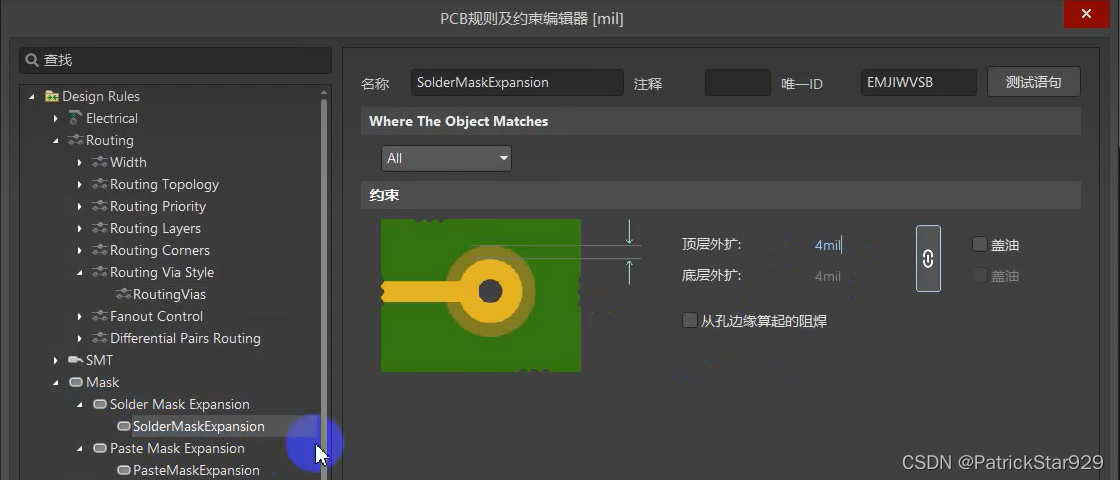

d.Mask设置——阻焊和锡膏补偿:

阻焊补偿按默认的4mil

锡膏补偿按默认的0mil

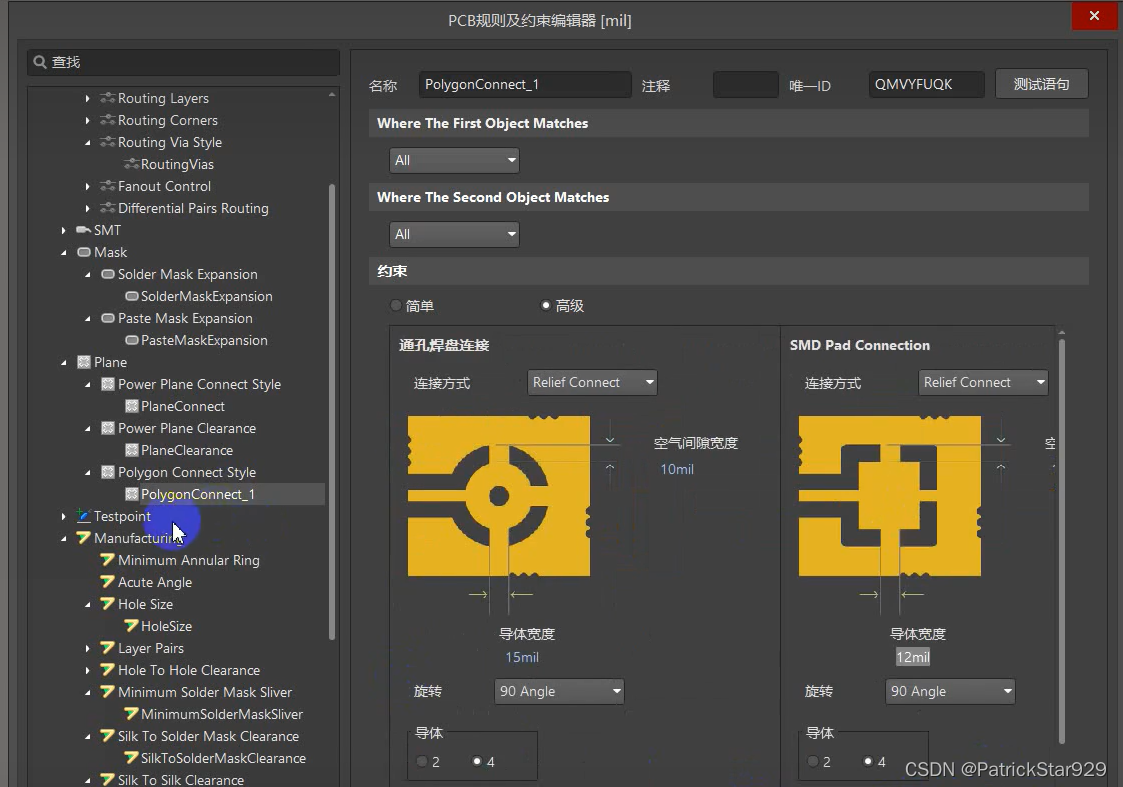

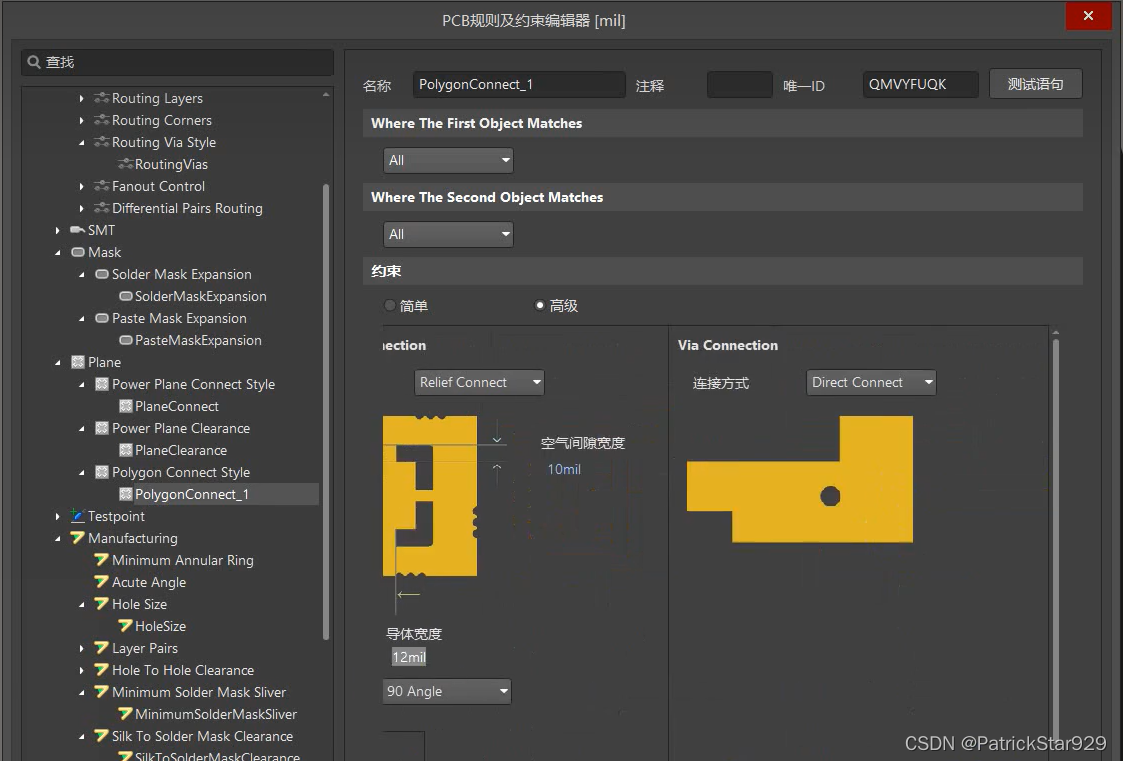

e.Plane设置——正片层铺铜连接方式:

设计–>规则–>Plane–>Polygon Connect Style,选择高级。通孔焊盘连接选择Relief Connect,导体宽度15mil,空气间隙宽度按默认10mil;表贴焊盘连接选择Relief Connect,导体宽度12mil,空气间隙宽度按默认10mil。

过孔连接选择Direct Connect

至于为什么铺铜和通孔焊盘、表贴焊盘及过孔的连接方式不同,以及AD16中如何操作,参考这篇文章【电路设计】AD多样覆铜连接方式共存。基本原因是如果采用手工焊接,焊盘若直接连接铺铜的话容易因为与大面积的铜皮连接导致焊接时散热过快,不好焊接,因此采用十字连接的方式(Relief Connect);过孔则采用直接连接(Direct Connect),降低线阻抗且美观一些。

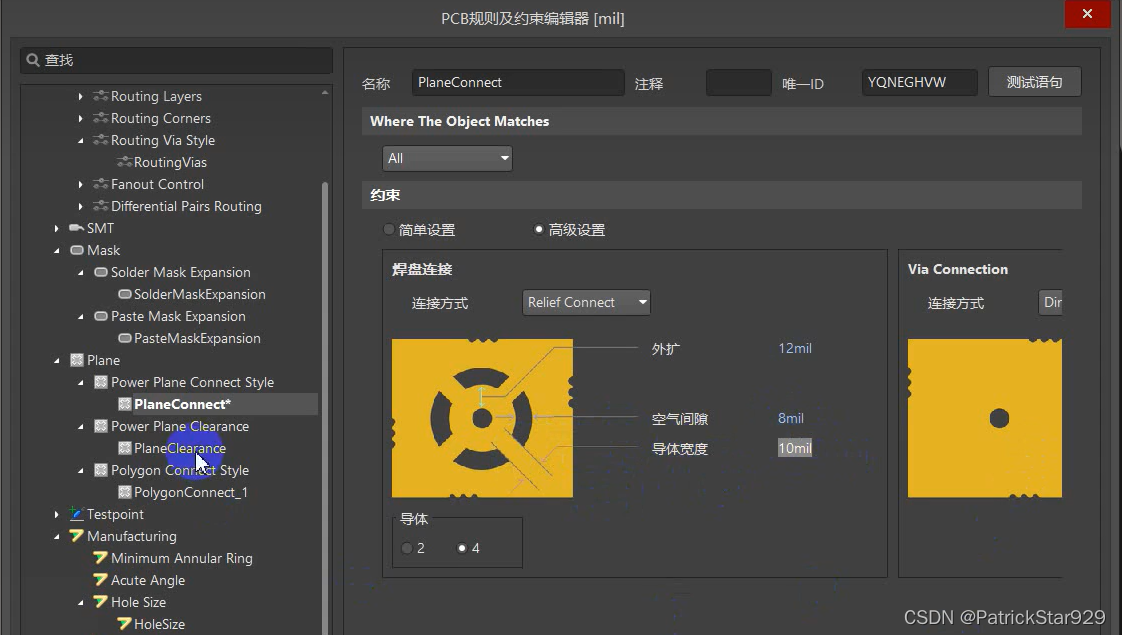

f.Plane设置——负片层铺铜连接方式:

设计–>规则–>Plane–>Power Plane Connect Style,选择高级(选择高级依然是为了区分焊盘和过孔)。焊盘选择Relief Connect,参数如下图设置;过孔选择Direct Connect。

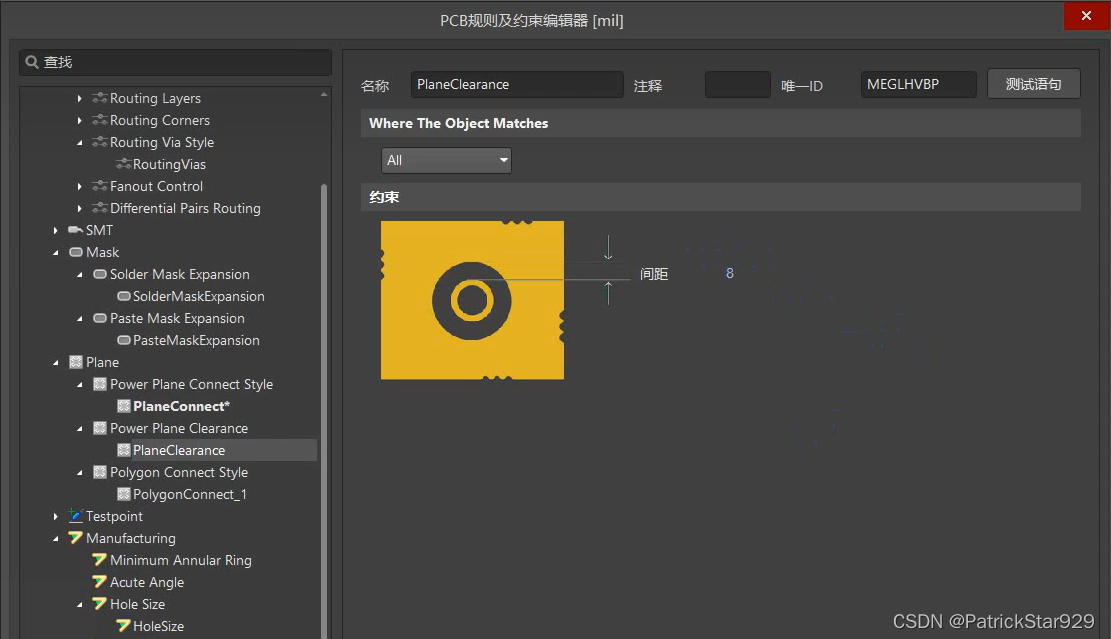

g.Plane设置——负片层间距:

改成8mil即可。

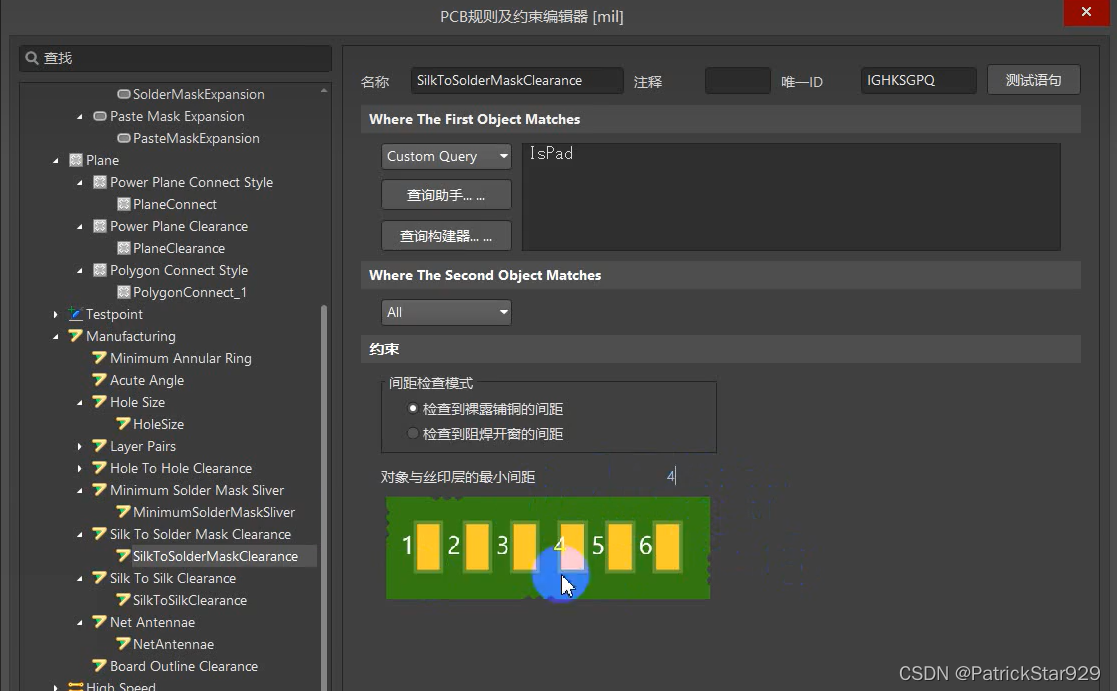

h.Manufacturing设置——丝印和阻焊间距:

为了防止丝印覆盖焊盘,设置SilkToSolderMaskClearance,约束–>检查到裸露铺铜的间距–>4mil;

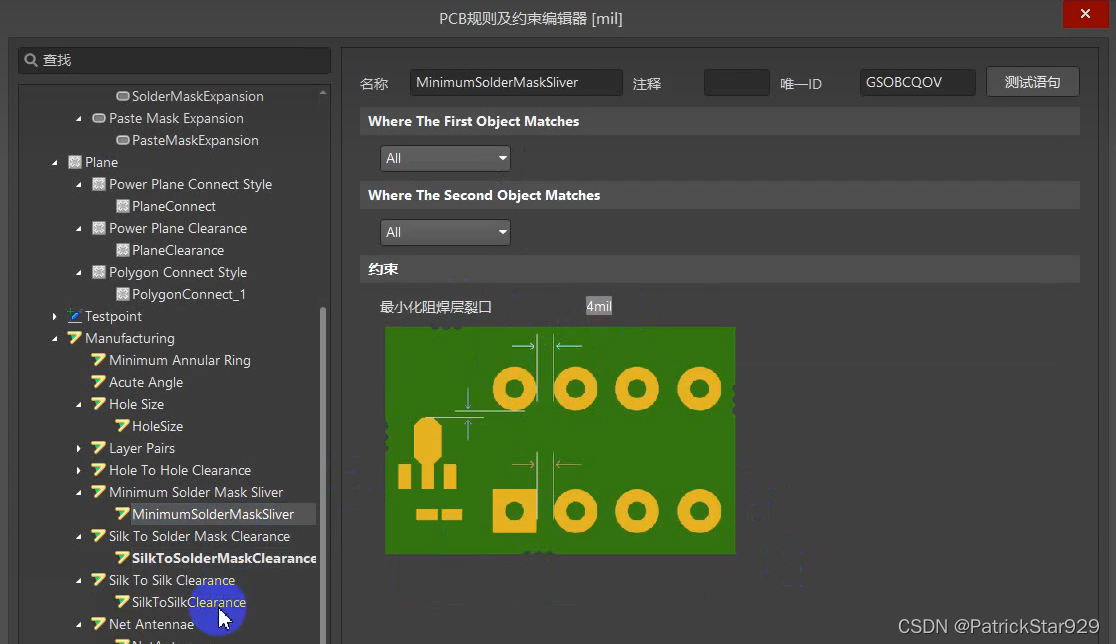

h.Manufacturing设置——最小的阻焊桥:

MinimumSolderMaskSilver–>约束–>4mil;

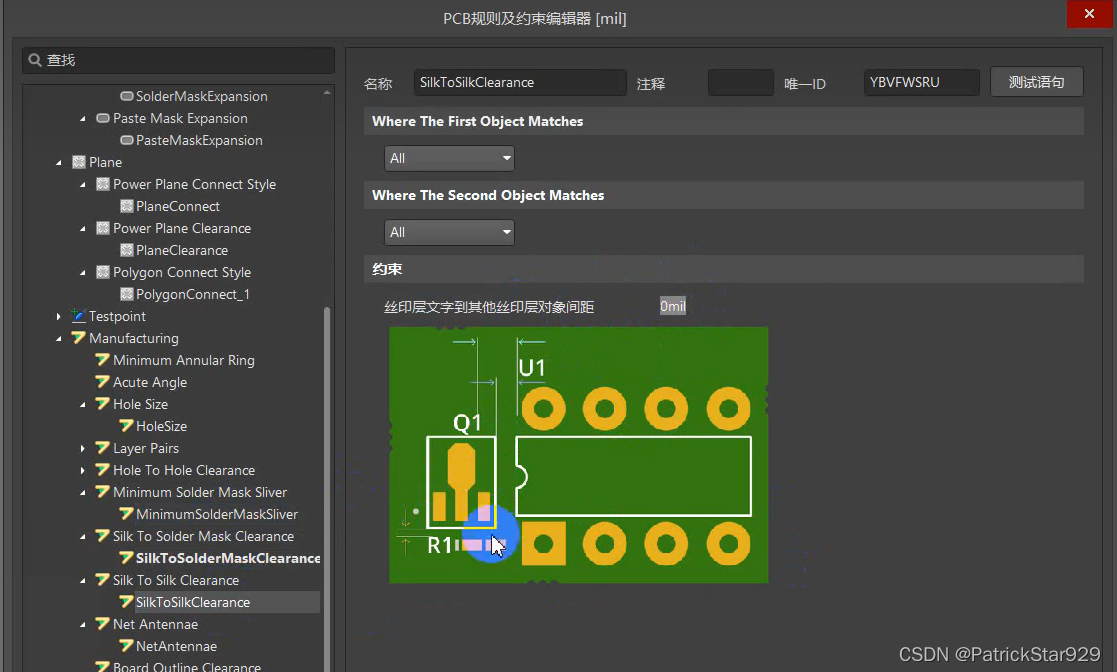

i.Manufacturing设置—丝印和丝印的间距:

为了防止丝印压丝印时出现报错,这里不设置(即按默认0mil)。

8.2 设置差分线规则:

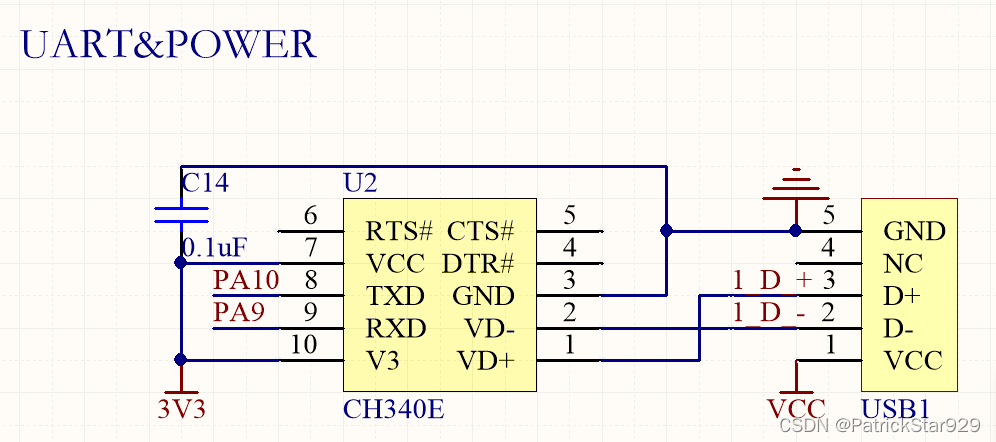

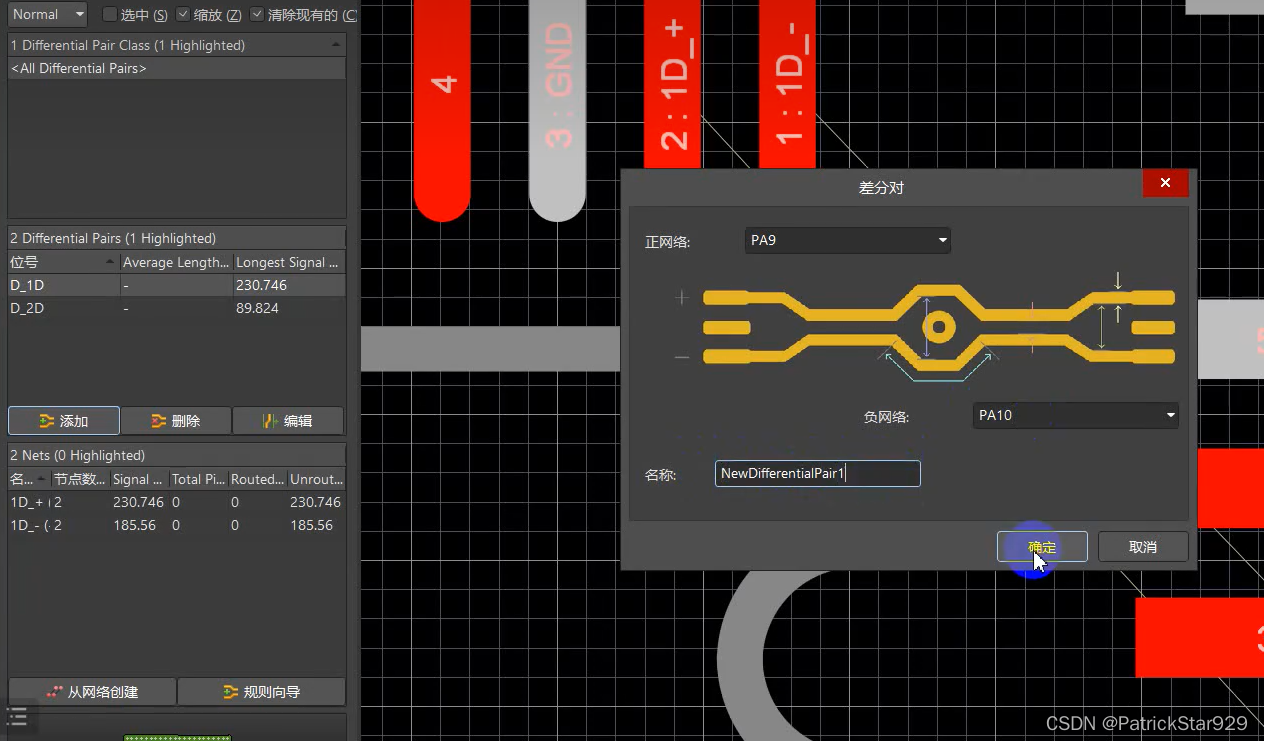

PCB的USB和晶振等需要差分走线,在差分走线之前需设置差分线规则。在AD软件中差分线的设置有两种方法:自动设置(需保证差分线的网络名称规范,如USB差分线中网络用D_+、D_-、P、N、H、L等成对地标清楚)和手动设置。如下图所示:USB座子1_D_+、1_D_-两根线网络命名是规范的,可使用自动设置差分线;PA9、PA10两根线可手动设置差分线。

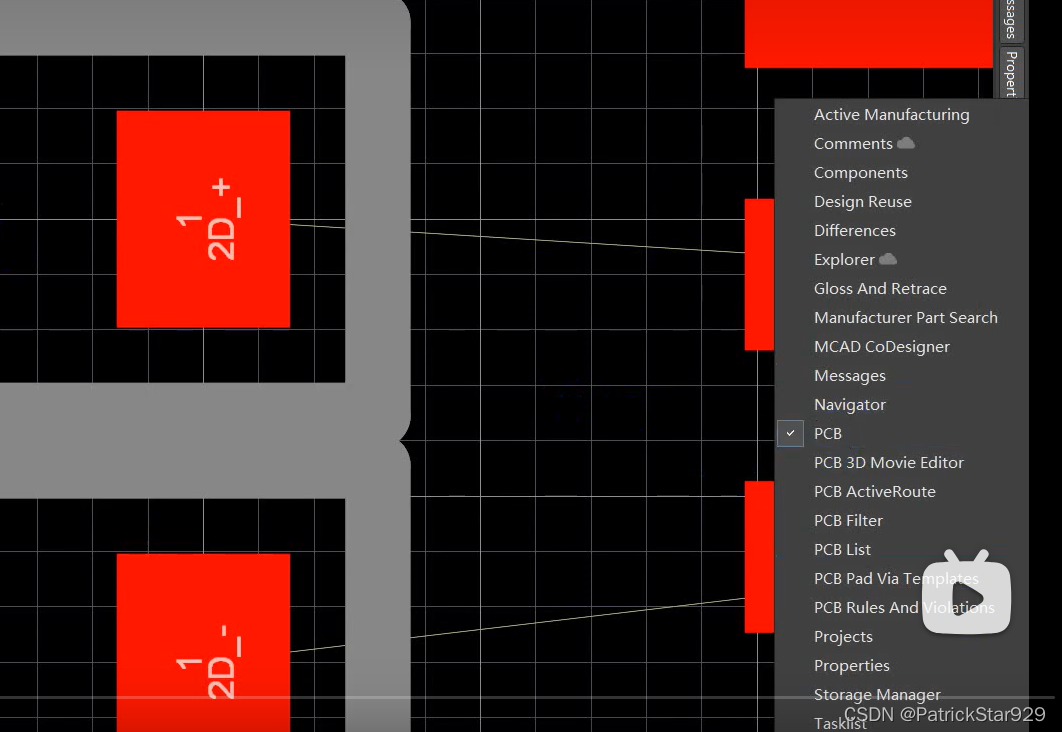

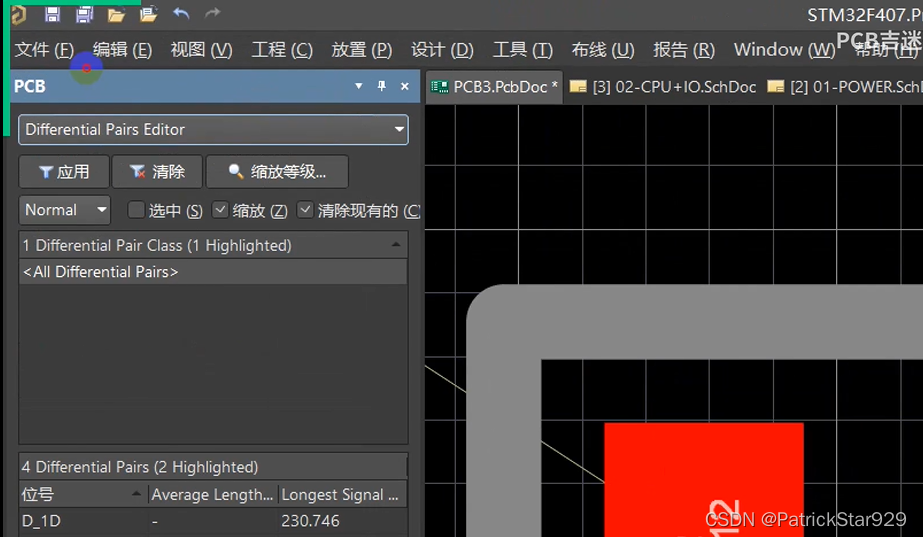

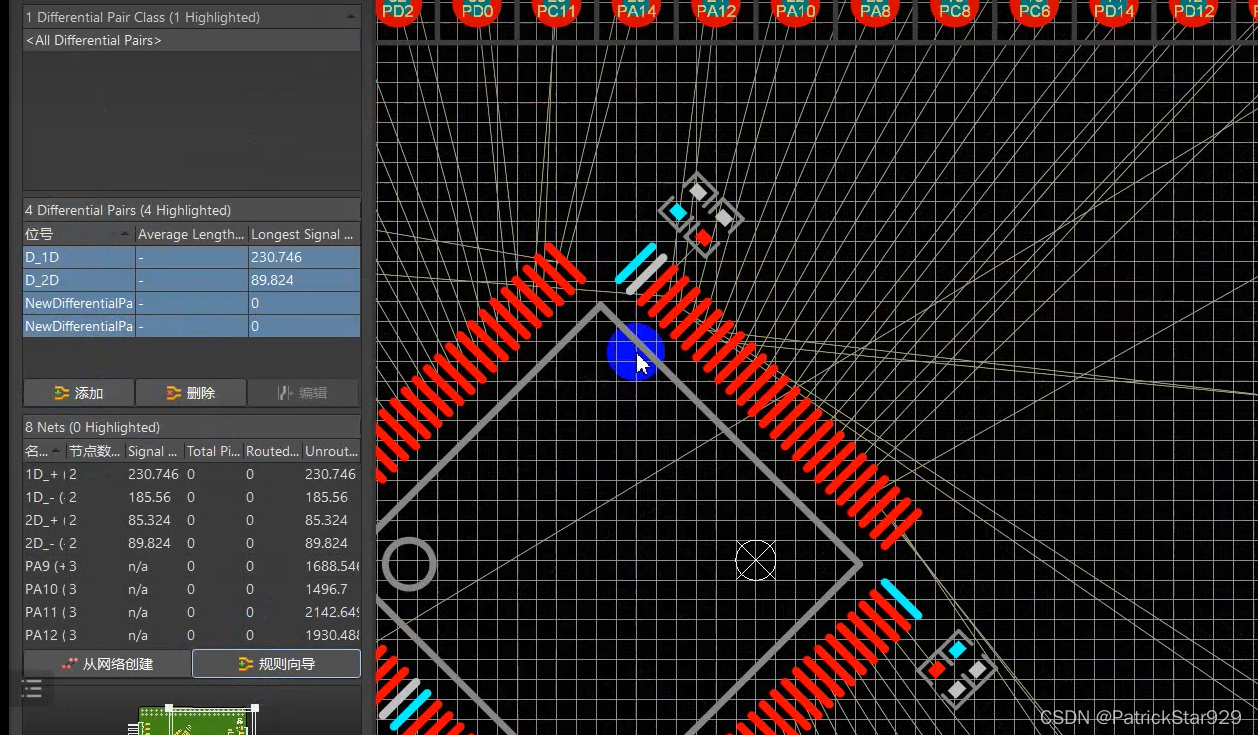

进入PCB布局布线的页面,右下角Panel面板选择PCB,调出PCB设置面板。在PCB设置面板中切换到Differential Pair Editor(差分对编辑器)。

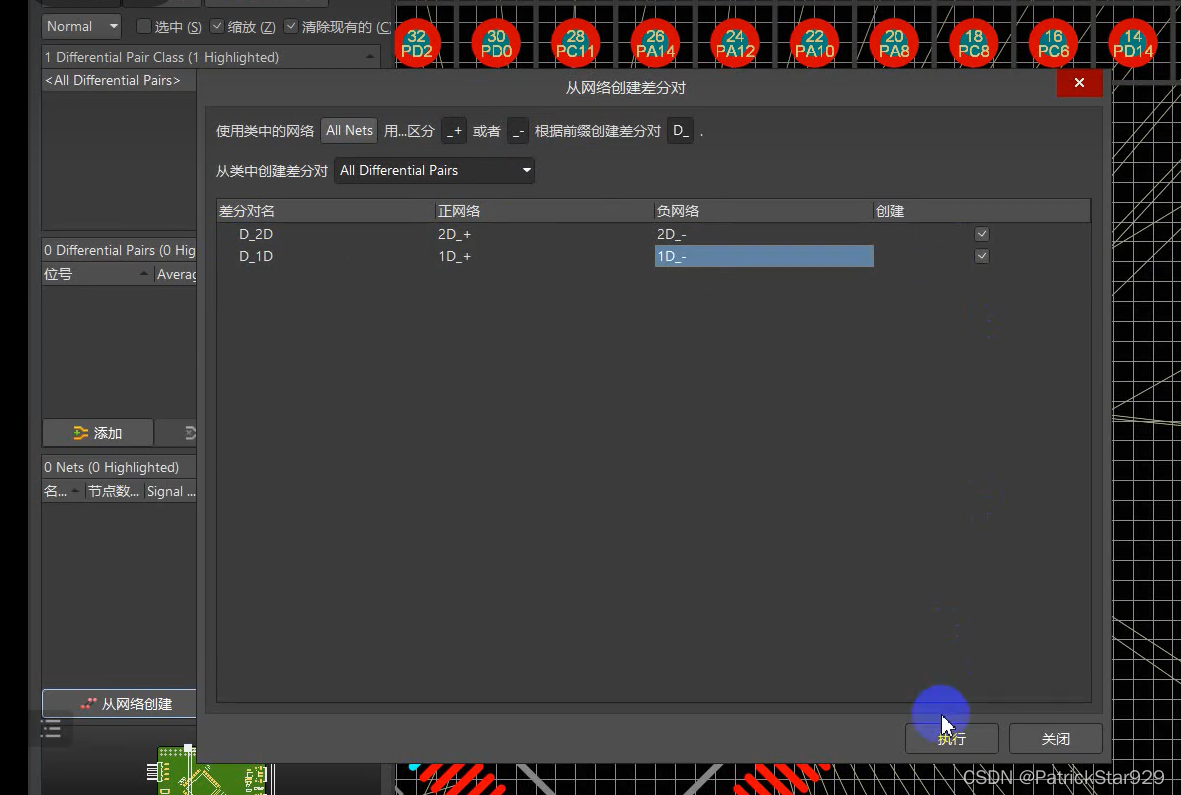

自动设置差分线:单击PCB设置面板中的“从网络创建”,弹出“从网络创建差分对”菜单,设置网络All Nets,设置区分差分对的标识_+、_-和前缀D-,从差分对类All Differential Pairs中创建差分对。AD软件自动得出差分对D_2D和D_1D,勾选它们并单击执行。

手动设置差分线:单击PCB设置面板中的“添加”,在弹出的“差分对”菜单中填写正网络和负网络的名称,如PA9和PA10、PA11和PA12,点击确定。

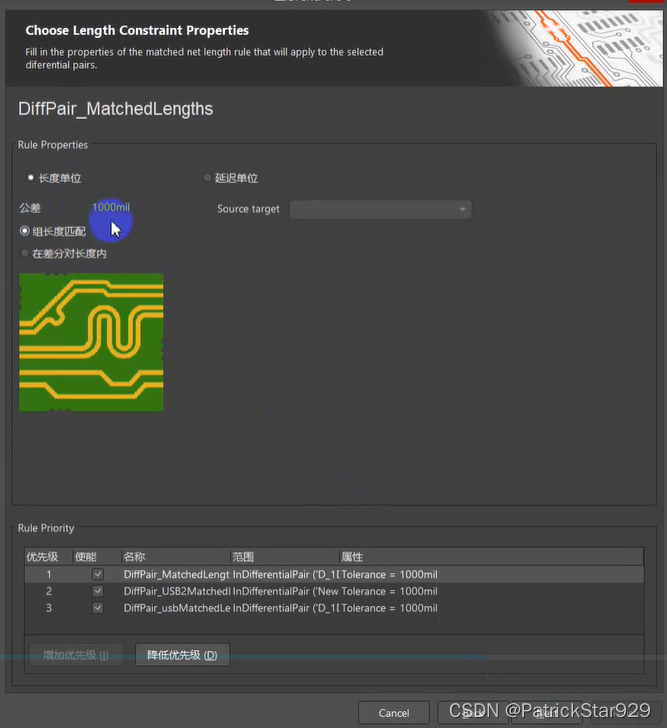

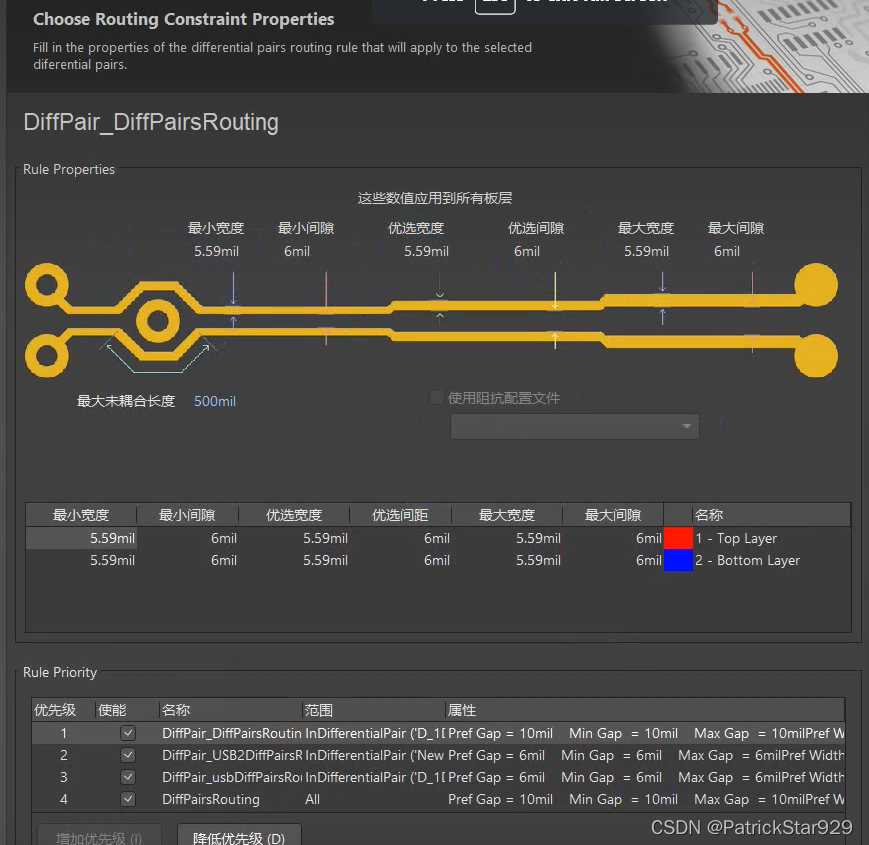

设置差分线的线宽线距:选中全部差分对,点击“规则向导”。

一路按默认并点击下一步,直到Diffpair_MatchedLengths,在这里设置等长差分线。由于这块PCB是低速板,可以不用设置等长差分对约束,因此此处依然按默认即可。

下一步DifferPair_DiffPairsRouting设置线宽线距。按照之前嘉立创阻抗计算工具中的计算结果(选择某一方案)设置线宽线距,此处差分线都是USB线,因此填入90欧姆的双端阻抗方案,宽度全填入5.59mil,间隙全填入6mil。

先写到这里,下一篇文章将记录PCB布线步骤。

、

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)