ARM架构不同版本与Coretex-M内核对应关系

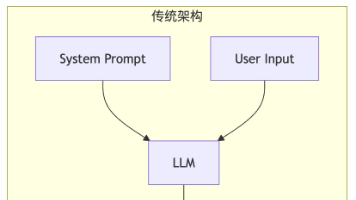

ARM架构版本(如ARMv6-M、ARMv7-M)是规范指令集与架构,而Cortex-M内核是具体实现。一个架构版本可对应多个内核,但一个内核仅属一个版本。ARMv6-M面向低功耗场景,支持Thumb-1指令集,代表内核有Cortex-M0/M0+。ARMv7-M支持Thumb-2指令集和FPU,代表内核包括Cortex-M3/M4/M7。ARMv8-M新增安全特性,分为Baseline(Cort

ARM 架构版本(如 ARMv6-M、ARMv7-M)是 指令集与架构规范(定义内核需支持的指令、寄存器、中断机制等),Cortex-M 内核是 基于该规范的具体实现(芯片中实际运行的计算核心)。

核心规律:一个架构版本可能对应多个内核(向下兼容基础规范,扩展不同功能),一个内核仅归属一个核心架构版本(部分高端内核会支持架构扩展,如 ARMv8-M Mainline 兼容 ARMv7-M)。

以下是 ARMv6-M 及后续主流架构版本与 Cortex-M 内核的完整对应关系(按架构版本从旧到新排序):

一、ARMv6-M 架构(入门级微控制器,低功耗、精简功能)

核心定位

面向低成本、低功耗场景(如传感器、简单控制模块),仅支持 Thumb-1 指令集(精简指令,减少代码体积),无 FPU(浮点单元),中断机制简化(NVIC 仅支持 2 位优先级,最多 4 级,不支持复杂嵌套)。

对应内核

| 内核型号 | 核心特性 | 典型应用场景 |

|---|---|---|

| Cortex-M0 | 基础版 ARMv6-M 内核,1.25 DMIPS/MHz,仅支持 Thumb-1,无硬件除法 | 极简成本设备(如按键控制、LED 驱动) |

| Cortex-M0+ | M0 增强版,1.34 DMIPS/MHz,新增硬件除法、单周期乘法,低功耗优化更出色 | 低功耗传感器(如温湿度传感器、蓝牙低功耗模块) |

| Cortex-M1 | 面向 FPGA 优化的 ARMv6-M 内核(可综合),功能与 M0 一致,适配可编程逻辑芯片 | FPGA 中的嵌入式软核(如工业控制 FPGA) |

二、ARMv7-M 架构(主流中端微控制器,平衡性能与功耗)

核心定位

嵌入式领域最常用架构,支持 Thumb-1 + Thumb-2 指令集(Thumb-2 融合 16 位/32 位指令,兼顾代码密度与执行效率),可选 FPU(单精度/双精度浮点),NVIC 支持多优先级位数(最多 8 位,256 级优先级),支持完整中断嵌套。

对应内核

| 内核型号 | 核心特性 | 典型应用场景 |

|---|---|---|

| Cortex-M3 | 基础版 ARMv7-M 内核,1.25 DMIPS/MHz,支持 Thumb-2,无 FPU,支持 MPU(内存保护单元) | 工业控制、电机驱动、中低端外设控制(如 STM32F1 系列) |

| Cortex-M4 | M3 增强版,1.25 DMIPS/MHz,新增 FPU(单精度浮点)、DSP 指令(乘加、滤波) | 带浮点运算/信号处理的场景(如音频处理、传感器数据融合、STM32F4 系列) |

| Cortex-M7 | 高性能 ARMv7-M 内核,2.14 DMIPS/MHz,支持双精度 FPU、L1 缓存(I-Cache/D-Cache)、AXI 总线 | 高端实时控制(如机器人、无人机、工业网关、STM32H7 系列) |

三、ARMv8-M 架构(高端微控制器,安全与性能升级)

核心定位

ARMv7-M 的升级架构,分为 Baseline(基础版) 和 Mainline(主线版) 两个分支,支持 TrustZone 安全扩展(硬件隔离安全/非安全世界),指令集兼容 ARMv7-M(向下兼容 Thumb-2),NVIC 增强(支持更多优先级、安全中断)。

对应内核

| 架构分支 | 内核型号 | 核心特性 | 典型应用场景 |

|---|---|---|---|

| ARMv8-M Baseline(基础版) | Cortex-M23 | 低功耗安全内核,1.34 DMIPS/MHz,支持 TrustZone,无 FPU,适配低成本安全设备 | 物联网安全终端(如智能门锁、加密传感器) |

| ARMv8-M Mainline(主线版) | Cortex-M33 | 平衡性能与安全,1.27 DMIPS/MHz,支持 TrustZone、FPU、DSP 指令、MPU | 中高端安全设备(如支付终端、工业安全控制器、STM32L5 系列) |

| ARMv8-M Mainline(主线版) | Cortex-M35P | M33 增强版,强化安全特性(如加密加速、防篡改),支持更多安全外设接口 | 高安全等级场景(如金融支付、汽车电子安全模块) |

| ARMv8-M Mainline(主线版) | Cortex-M55 | 高性能 AI 优化内核,3.0 DMIPS/MHz,集成 Helium 向量扩展(AI 加速)、L1 缓存 | 边缘 AI 场景(如图像识别、语音唤醒、STM32U5 系列) |

四、ARMv9-M 架构(最新一代,AI 与安全强化)

核心定位

ARMv8-M 的迭代架构,聚焦 AI 性能、安全增强、实时性优化,兼容 ARMv8-M 指令集,强化 Helium 向量扩展(AI 算力提升),支持更灵活的内存保护、安全调试机制。

对应内核

| 内核型号 | 核心特性 | 典型应用场景 |

|---|---|---|

| Cortex-M85 | 旗舰级 Cortex-M 内核,4.0 DMIPS/MHz,Helium 向量扩展(AI 加速)、双精度 FPU、L1 缓存 | 高端边缘 AI + 安全场景(如智能摄像头、工业 AI 传感器、汽车座舱控制) |

五、关键补充:架构与内核的核心关联规则

- 向下兼容:高版本架构内核可兼容低版本指令集(如 ARMv8-M 内核可运行 ARMv7-M/ARMv6-M 编译的代码),但低版本架构内核无法支持高版本指令(如 Cortex-M0 不能运行 ARMv7-M 的 Thumb-2 扩展指令)。

- 功能扩展:同一架构下的高型号内核,是对基础架构的功能增强(如 Cortex-M4 比 M3 多 FPU/DSP,Cortex-M7 比 M4 多缓存),而非架构升级。

- 芯片选型参考:芯片型号通常包含内核信息(如 STM32F407 用 Cortex-M4,STM32H743 用 Cortex-M7,STM32L562 用 Cortex-M33),可通过内核反推架构版本。

六、总结表格(快速查询)

| 架构版本 | 核心指令集 | 代表内核 | 核心优势 |

|---|---|---|---|

| ARMv6-M | Thumb-1 | M0、M0+、M1 | 低成本、低功耗、精简 |

| ARMv7-M | Thumb-1 + Thumb-2 | M3、M4、M7 | 平衡性能与功耗,应用最广 |

| ARMv8-M | Thumb-1 + Thumb-2 + 安全扩展 | M23、M33、M35P、M55 | 安全(TrustZone)、AI 优化 |

| ARMv9-M | Thumb-2 + Helium 扩展 | M85 | 高端 AI、极致性能与安全 |

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)