GPIO的开漏输出原理

开漏输出的原理可简化为“内部N-MOS拉低,外部电阻拉高”:它放弃了主动输出高电平的能力,换来了多设备并联的“线与”功能和灵活的电平兼容性,是总线通信(如I2C)、跨电压域控制等场景的核心输出模式,使用时需牢记“必须外接上拉电阻”这一前提。开漏输出(Open-Drain Output)的核心原理是仅通过单一路MOS管(通常是N-MOS)控制引脚电平,仅能主动拉低引脚电压,无法主动输出高电平,高电平

一、介绍

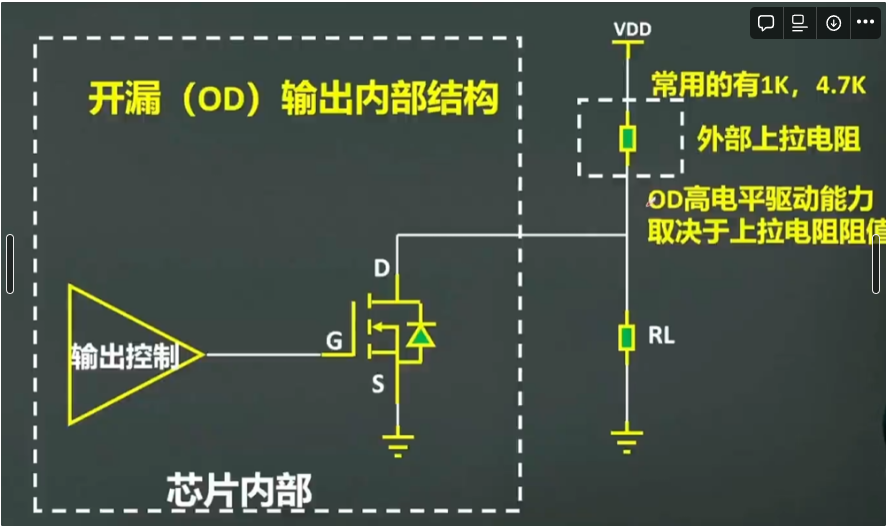

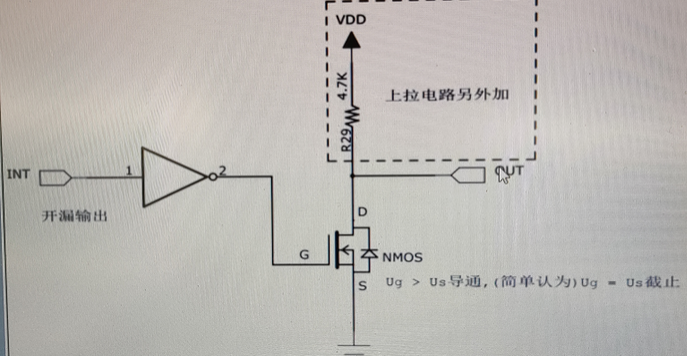

开漏指的是场效应管的“漏极”,开漏输出(Open-Drain Output)就是把场效应管的漏极直接引出来作为输出引脚,然后通过一个上拉电阻与高电平相连的输出模式。如下图:

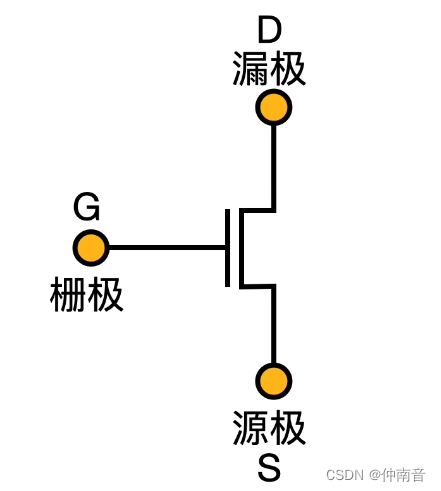

晶体管的结构如下:

当GPIO输出低电平时,通过一个晶体管(通常是NMOS晶体管)使得外部电路接地,从而实现低电平的输出;当GPIO输出高电平时,通过上拉电阻使得外部电路连接到高电平。

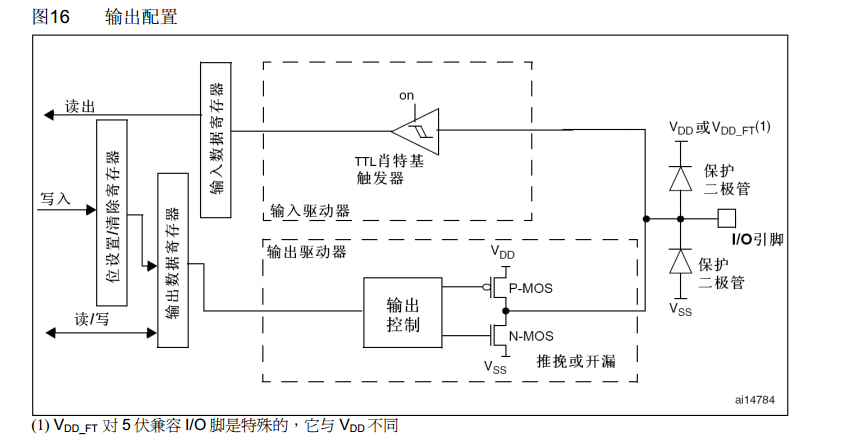

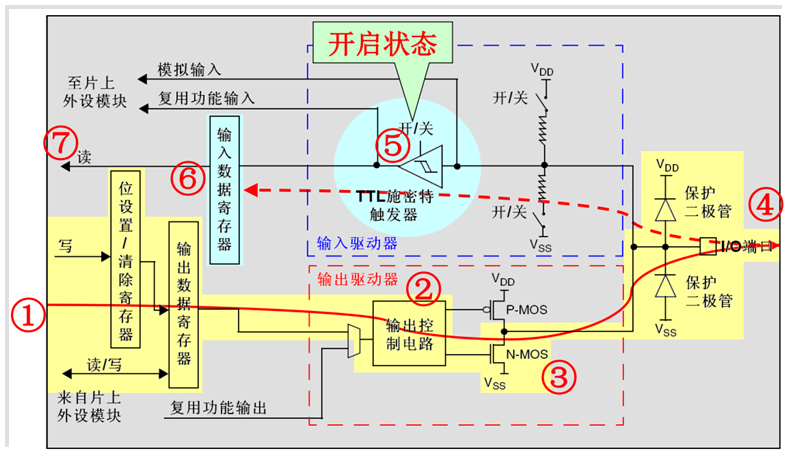

上面是大致结构,而单片机的GPIO内部详细设计结构如下:

二、核心硬件结构

开漏输出模式下(上拉电阻+N-MOS管),通过设置位设置/清除寄存器或者输出数据寄存器的值,途经N-MOS管,最终输出到I/O端口。如下图1,2,3,4所示:

核心原理是仅通过单一路MOS管控制引脚电平,仅能主动拉低引脚电压,无法主动输出高电平,高电平需依赖外部电路(如上拉电阻)实现,本质是一种“半主动”的输出驱动方式。

单N-MOS管的“拉低”逻辑:

开漏输出的GPIO引脚内部,仅集成了一个N-MOS管,其结构和工作逻辑如下:

结构上:

- MOS管的连接方式:N-MOS的一端接GPIO引脚,另一端直接连接GND,而引脚与单片机内部电源(如3.3V)之间无主动导通路径(这是与推挽输出的核心区别)。

逻辑上:

1. 输出低电平时:单片机通过寄存器,控制N-MOS管导通,此时GPIO引脚与导通的N-MOS直接连接到GND,引脚电压被拉低至接近0V(低电平)。

2. 输出高电平时:单片机控制N-MOS管“截止”,此时GPIO引脚与GND的通路被断开,但引脚也未连接到任何内部电源,所以引脚处于“悬空”(高阻)状态,无法主动输出高电平,此时需外部电路提供高电平通路。

为了实现完整的高电平输出功能,开漏输出通常需要一个外部上拉电阻。当输出端口处于高阻态时,外部上拉电阻将输出端口拉高至所需的高电平。

上拉电阻的阻值需合理选择:阻值太小会导致低电平时N-MOS导通电流过大(可能烧毁器件),阻值太大则会导致高电平驱动能力弱、电平上升速度慢(影响信号时序),常见取值为1kΩ~10kΩ。

3. 关键特性:

“线与”逻辑与电平兼容性

基于上述原理,开漏输出衍生出两个核心特性,也是其广泛应用的原因:

- 支持“线与”逻辑:多个开漏输出引脚可并联在同一条总线上(共用一个上拉电阻)。只要其中任意一个引脚控制N-MOS导通(输出低电平),整个总线就会被拉低;只有所有引脚的N-MOS都截止时,总线才会被上拉电阻拉为高电平——这就是“线与”(即多个信号中只要有一个低,结果就为低),典型应用如I2C总线的SDA、SCL引脚,实现多设备共享总线。

- 灵活的电平兼容性:通过选择不同电压的外部电源作为上拉电源,可实现跨电压域输出。例如,3.3V的MCU使用开漏输出时,若上拉电阻接5V电源,引脚就能输出5V高电平,轻松兼容5V电平的外设(无需额外电平转换芯片)。

三、总结

开漏输出的原理可简化为“内部N-MOS拉低,外部电阻拉高”:它放弃了主动输出高电平的能力,换来了多设备并联的“线与”功能和灵活的电平兼容性,是总线通信(如I2C)、跨电压域控制等场景的核心输出模式,使用时需牢记“必须外接上拉电阻”这一前提。

参考:

更多推荐

已为社区贡献41条内容

已为社区贡献41条内容

所有评论(0)