测试工程师视角下的 DDR4 内存 Training

摘要:DDR4内存系统面临更高的信号完整性挑战,包括更快的传输速率(达3200MT/s)和更低的工作电压(1.2V),导致时序和电压裕量大幅压缩。DDR4的关键技术变革包括采用POD接口替代SSTL,需要动态VREF校准机制。内存训练通过精确校准DQS-DQ偏斜、阻抗匹配(ZQ校准)、写均衡(解决Fly-by拓扑的时钟偏斜)等步骤,确保信号质量。训练过程包括读/写数据眼图校准、VREF优化等,通过

第一章 高速DDR4系统中校准

1.1 从DDR3到DDR4:信号完整性挑战的升级

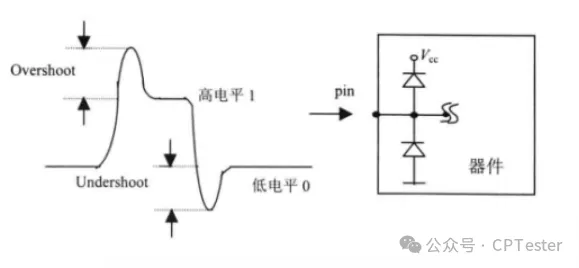

DDR4相较于其前代DDR3,在多个维度上实现了显著的技术飞跃。其数据传输速率从DDR3的最高2133 MT/s提升至DDR4的3200 MT/s甚至更高,同时工作电压从1.5V降至1.2V 。这些进步在提升带宽和降低功耗的同时,也极大地压缩了系统稳定运行的时序(timing)与电压(voltage)裕量。在更高的频率下,信号的有效窗口变得极其短暂,任何微小的时钟抖动、信号偏斜或噪声都可能导致数据采样错误。更低的电压则意味着信号的抗干扰能力减弱,使得系统对电源噪声和阻抗不匹配等问题更为敏感 。

此外,DDR4引入了一项关键的架构变革:数据(DQ)总线的I/O标准从DDR3的SSTL(Stub Series Terminated Logic,短截线串联端接逻辑)转向了POD(Pseudo Open Drain,伪开漏)接口 。SSTL接口具有对称的信号摆幅,其参考电压(VREF)通常固定在电源电压的一半(

VDDQ/2)。而POD接口则具有非对称的信号摆幅,其逻辑高电平为VDDQ,逻辑低电平则是一个浮动电压,其理想的参考电压不再是简单的VDDQ/2,而是会根据驱动强度和端接电阻等因素变化 。这一根本性的改变使得固定的外部参考电压方案不再适用,必须采用一种动态的、内部可调的VREF校准机制,这也是DDR4训练中新增的关键环节之一。

这些综合因素导致,仅仅依靠静态编程时序参数已远不足以保证DDR4内存的稳定工作。系统必须具备一种动态的、闭环的自适应能力,通过主动探测内存通道的物理特性并进行相应补偿,而内存训练正是实现这一目标的核心技术 。

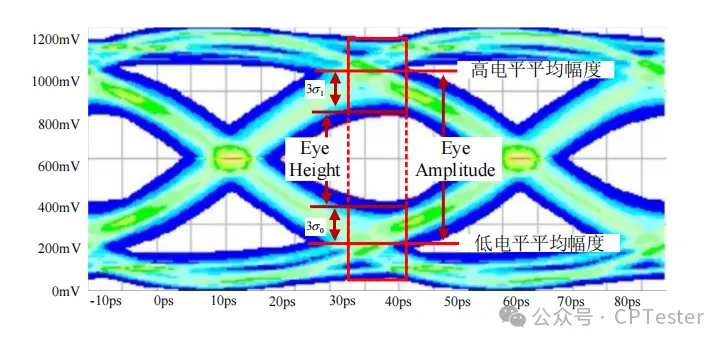

1.2 数据眼图:信号质量与时序裕量的可视化

在高速数字信号领域,“数据眼图”(Data Eye Diagram)是评估信号完整性的黄金标准。它通过在示波器上叠加显示信号波形的不同比特位而形成,其形状酷似一只眼睛。眼图的“眼睛”张开得越大,代表信号质量越好。

- 眼图宽度:代表有效的时序裕量。接收器需要在眼睛睁开的时间窗口内对数据进行采样。较宽的眼睛意味着系统对时钟抖动(jitter)和信号偏斜(skew)的容忍度更高,即建立时间(setup time)和保持时间(hold time)的裕量更大。

- 眼图高度:代表有效的电压裕量。较高的眼睛意味着信号的逻辑高电平和低电平之间有更大的差值,从而提高了信噪比,使系统能够更好地抵抗噪声干扰。

内存训练的根本目标,可以被形象地理解为:通过一系列精密的校准算法,为内存控制器(IMC)和DRAM芯片之间的每一条数据(DQ)链路,在接收端尽可能地张开一个最大、最清晰的数据眼图 。训练过程中的每一个步骤,无论是时序调整还是电压校准,都是为了对抗那些企图“闭上眼睛”的物理因素,如信号偏斜、抖动、串扰(crosstalk)和码间干扰(Intersymbol Interference, ISI)。

1.3 内存通道的物理现实:偏斜、衰减与码间干扰

理想情况下,从内存控制器发出的所有信号应同时到达DRAM芯片。然而,物理世界并非如此完美。内存通道——包括CPU封装内的引线、主板PCB上的铜走线以及DIMM内存条上的布线充满了非理想因素 。

- 信号偏斜(Skew):由于PCB走线长度的微小差异、硅芯片制造过程中的工艺偏差以及不同元器件的电气特性不一,导致本应同步的信号在不同时间到达目的地 。偏斜主要分为两类:

- 字节内偏斜(Intra-byte Skew):同一个数据字节(例如DQ0-DQ7)内的各个数据位之间存在的到达时间差异。

- DQS-DQ偏斜(DQS-to-DQ Skew):数据选通脉冲(DQS)信号与它所对应的DQ数据信号之间的到达时间差异。DQS是数据的同步时钟,如果它与数据不同步,接收方将无法在数据眼图的中心位置进行准确采样 。

- 信号衰减(Attenuation):信号在通过PCB走线时,由于铜的电阻和介电材料的损耗,其能量会逐渐损失,导致信号幅度降低,从而减小了眼图的高度。

- 码间干扰(ISI):由于通道的带宽限制,一个比特位的信号会拖尾并干扰到后续比特位的信号,导致信号失真,同样会压缩数据眼图。

内存训练的核心任务之一,就是精确测量并补偿这些偏斜,特别是DQS-DQ偏斜和字节内偏斜,确保数据和它的同步时钟在接收端能够完美对齐。

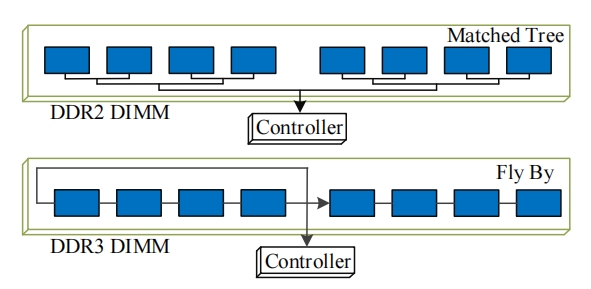

1.4 Fly-By拓扑:必要的妥协与偏斜的根源

为了在多DIMM、高频率环境下维持良好的信号完整性,DDR3和DDR4内存系统普遍采用了“Fly-by”布线拓扑结构来传输地址、命令(C/A)和时钟(CK)信号 。与早期的“T型”或“树形”拓扑不同,Fly-by拓扑将这些信号从内存控制器发出后,以菊花链的形式依次经过DIMM上的每一个DRAM芯片,并在线路末端进行端接。这种设计显著减少了信号反射,是实现高速运行的关键 。

然而,这种设计带来了一个不可避免的副作用:时钟(CK)信号的传播延迟。CK信号到达距离控制器最近的DRAM芯片的时间,要早于它到达最远的DRAM芯片的时间。这意味着在同一条DIMM上,不同的DRAM芯片看到的CK时钟存在一个固有的、可预测的相位差,即飞行时间偏斜(flight-time skew)。

与此同时,数据(DQ)和数据选通(DQS)信号通常采用点对点的短路径连接,其延迟相对固定。这就造成了一个根本性的时序矛盾:内存控制器在进行写操作时,必须确保其发出的DQS信号与CK信号在每一个DRAM芯片的输入引脚处都是同步的。但由于CK信号本身存在传播延迟,控制器不能以同一个时间基准向所有DRAM发送DQS信号。

这种由主板级物理布线设计所引入的系统性偏斜,直接催生了DDR4内存训练中一个至关重要的步骤写均衡(Write Leveling)。内存训练不再是可有可无的优化,而是解决高速内存总线物理设计固有问题的必要手段。它标志着内存接口设计理念的转变:从静态配置转向动态的、闭环的自适应校准。系统必须主动探测并量化这种物理偏斜,然后通过电子手段进行精确补偿,才能保证可靠的数据写入。

第二章 DDR4初始化与训练序列:详细流程剖析

DDR4的内存训练是一个结构化、分阶段的校准过程。在系统加电自检(POST)期间,内存控制器会遵循一套预定义的序列,与DRAM芯片协同工作,对内存通道的各项电气和时序参数进行精细调整。这个过程可以被视为一个自动化的测试工程师,利用闭环反馈系统,将内存接口从一个不确定的初始状态调校至最佳工作点 。整个训练序列体现了一种从粗调到精调、从系统级到比特级的层级化校准思想。

2.1 ZQ校准:跨越PVT变化的阻抗匹配维护

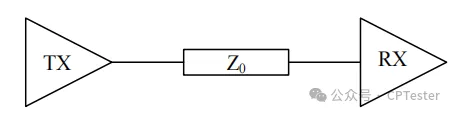

- 目的:ZQ校准旨在精确校准DRAM芯片内部的导通电阻(Ron)和片上端接电阻(ODT)。精确的阻抗匹配对于信号完整性至关重要,它可以最大限度地减少信号在传输线末端发生反射,从而保证信号质量和最大化功率传输 。

- 机制:在DRAM芯片上有一个专用的ZQ引脚,通过一个高精度的外部参考电阻(通常为240Ω,误差±1%)接地。当内存控制器发出ZQ校准命令(如ZQCL - ZQ Calibration Long或ZQCS - ZQ Calibration Short)时,DRAM内部的校准电路会以此参考电阻为基准,调整其内部的Ron和ODT电路,使其阻值与参考值成特定比例 。这个过程能够有效补偿因制造工艺(Process)、工作电压(Voltage)和环境温度(Temperature)——即PVT——变化所引起的阻抗漂移 。

- 结果:内存控制器和DRAM芯片的驱动器与端接器之间实现了精确的阻抗匹配,为后续所有高速信号的清晰传输奠定了坚实的物理基础。

2.2 写均衡:补偿Fly-By架构中的时钟-选通脉冲偏斜

- 目的:如前所述,写均衡(Write Leveling)的核心目标是解决Fly-by拓扑引入的CK到DQS的偏斜问题。它需要确保内存控制器发出的写DQS信号的上升沿,能够与CK时钟的上升沿在每一个DRAM芯片的输入引脚处精确对齐,从而满足关键的tDQSS时序参数 。

- 机制:这是一个精巧的闭环反馈过程。

- 控制器通过模式寄存器设置(MRS)命令,将目标DRAM芯片置于特殊的“写均衡模式” 。

- 在此模式下,DRAM的行为发生改变:它不再将DQS视为数据选通,而是用DQS的上升沿去采样CK时钟的状态(高电平或低电平)。

- 然后,DRAM将采样到的CK值(0或1)通过DQ数据线反馈给内存控制器 。

- 控制器接收到反馈后,会迭代地调整其内部一个可编程延迟线,微调DQS信号的发送相位,然后再次发出DQS脉冲。

- 这个“发送DQS -> DRAM采样CK -> 反馈结果 -> 控制器调整延迟”的循环会一直持续,直到控制器在DQ线上观测到一个从0到1的跳变。这个跳变点精确地标志着DQS的上升沿与CK的上升沿在DRAM端实现了对齐 。

- 结果:控制器为每个数据字节通道(DQS Group)都学习到了一个独立的、精确的延迟值。在后续的写操作中,控制器会应用这个延迟值来发送DQS信号,从而保证数据和时钟在DRAM芯片处是同步的,无论该芯片在Fly-by链路上的物理位置如何。

2.3 DQS门训练/读门训练:精确定位控制器的读取窗口

- 目的:在读操作期间,DQS信号由DRAM芯片发出,作为同步时钟来锁存DQ数据。然而,在读操作的间隙,DQS总线处于高阻态(Tri-stated),容易受到噪声干扰产生伪信号。DQS门训练(DQS Gate Training),又称读门训练(Read Gate Training),旨在让内存控制器精确地学会何时“打开大门”(使能内部接收电路)以接收有效的DQS前导码(preamble),以及在数据突发结束后何时“关闭大门”,以屏蔽掉总线空闲时的噪声和伪边沿,防止这些干扰信号污染内部的读FIFO缓冲 。

- 机制:控制器会向DRAM连续发出背靠背的读命令,以产生一个连续的DQS信号流。然后,控制器会扫描其内部“门控”信号的延迟设置,通过尝试在不同时间点开启和关闭接收门,来寻找一个“有效窗口”。这个窗口的左边界是能够完整捕获到DQS前导码的最早时间点,右边界则是最晚的时间点。最终,控制器会将门控信号的延迟设置在有效窗口的中心位置,以获得最大的时序裕量 。

- 结果:内存控制器建立了一个可靠的DQS接收机制,确保只在有效的读操作期间处理DQS信号,极大地提高了读操作的鲁棒性。

2.4 读数据眼图校准:将选通脉冲置于数据窗口中心

- 目的:在完成了DQS门训练后,控制器虽然能正确接收DQS信号,但DQS的边沿与各个DQ数据位的中心可能仍未完美对齐。此阶段的目标是进一步微调,确保DQS的锁存边沿能够精确地落在每个DQ数据位有效窗口(即数据眼图)的正中央,从而最大化建立时间和保持时间的裕量 。

- 机制:这个过程通常分为两步:

- 读每比特DQ去偏斜(Read Per-Bit DQ Deskew):控制器从DRAM的一个特殊寄存器——多用途寄存器(MPR)中读取一个预定义的、固定的数据码型。由于PCB走线长度差异等因素,这些数据位的信号到达控制器的时间会有微小差别。控制器会为每一条DQ线路独立调整一个微小的延迟,直到一个字节通道内的所有8个DQ信号都完美对齐,消除了比特间的偏斜 。

- 读DQS居中(Read DQS Centering):在所有DQ位对齐之后,控制器会整体调整DQS信号的接收时机。它通过扫描DQS的延迟,找到能够正确读取数据的有效窗口的左右边界,然后将最终的DQS接收延迟设置在这两个边界的中点 。

- 结果:控制器实现了对读取数据的最佳采样时机,拥有最大的时序裕量来应对温度、电压变化带来的时序漂移,显著提升了读取稳定性。

2.5 写数据眼图校准:在DRAM端对齐数据与选通脉冲

- 目的:与读校准类似,写数据眼图校准(Write Data Eye Calibration)旨在确保控制器发出的DQ数据和DQS选通脉冲在到达DRAM芯片时,DQS的边沿能够精确地落在DQ数据眼图的中心 。

- 机制:写校准比读校准更为复杂,因为控制器无法直接获知DRAM端的信号质量。它必须通过一种“写后读回验证”的间接方式来进行。

- 写每比特DQ去偏斜(Write Per-Bit DQ Deskew):控制器向DRAM写入特定的数据码型,同时为每个DQ位独立扫描一个延迟值。然后,它再将数据读回,通过比较写入和读出的数据是否一致,来判断哪个延迟设置是有效的。通过这种方式,控制器可以消除写路径上的比特间偏斜 。

- 写DQS-DQ居中(Write DQS-to-DQ Centering):在DQ位对齐后,控制器会固定DQS的发送时机,然后扫描DQ数据的发送延迟,找到能够被DRAM正确写入的有效窗口的左右边界,并最终将DQ的发送延迟设置在窗口的中心 。

- 结果:DRAM芯片能够在具有最大时序裕量的条件下接收写入数据,确保了高频率下写入操作的可靠性。

2.6 VREF训练:为POD接口优化参考电压

- 目的:为DDR4的伪开漏(POD)接口找到最佳的参考电压(VREF)。这个VREF是接收器(读操作时是控制器,写操作时是DRAM)用来判断输入信号是逻辑“1”还是逻辑“0”的阈值电压 。由于POD接口的信号眼图在垂直方向上是非对称的,一个优化的VREF对于最大化电压裕量、抵抗噪声至关重要 。

- 机制:在VREF训练期间,发送方会发送一个已知的数据码型。接收方则会在一个预设的范围内扫描其内部VREF的电压值。在每个VREF设置下,接收方都会检查接收到的数据错误率或评估眼图的张开程度。最终,它会选择那个能够提供最大垂直裕量(即位于眼图垂直方向中心)的VREF值作为最终设定 。DDR4支持在每个DRAM芯片甚至每个Rank(内存列)的粒度上进行独立的VREF训练,以应对不同芯片间的细微差异 。

- 结果:系统为读写操作分别建立了最佳的电压判决阈值,极大地增强了信号的抗干扰能力和整体稳定性。

2.7 DDR4关键训练阶段总结表

为了清晰地概括上述复杂的校准流程,下表总结了DDR4内存训练中的关键阶段、其核心目标以及所解决的物理问题。

|

训练阶段 |

核心目标 |

解决的物理问题 |

关键JEDEC参数 |

|

ZQ校准 |

校准DRAM的驱动和端接阻抗 |

信号反射、阻抗不匹配、PVT漂移 |

N/A (内部阻抗) |

|

写均衡 |

在DRAM端对齐写DQS与CK时钟 |

Fly-by拓扑引入的时钟传播延迟偏斜 |

tDQSS |

|

DQS门训练 |

精确定位读DQS的有效接收窗口 |

总线空闲时的噪声和伪信号干扰 |

tDQSCK |

|

读每比特DQ去偏斜 |

对齐同一字节内各DQ位的到达时间 |

PCB走线长度不等造成的比特间偏斜 |

N/A (内部延迟) |

|

读DQS居中 |

将DQS采样边沿置于读数据眼图中心 |

DQS与DQ数据之间的整体时序偏斜 |

建立/保持时间裕量 |

|

写每比特DQ去偏斜 |

在DRAM端对齐各DQ位的写入时间 |

写路径上的比特间偏斜 |

N/A (内部延迟) |

|

写DQS-DQ居中 |

将DQS写入边沿置于写数据眼图中心 |

写路径上DQS与DQ的整体时序偏斜 |

tDS/tDH |

|

VREF训练 |

优化接收器的电压判决阈值 |

POD接口的非对称信号摆幅、噪声干扰 |

V_{IH}/V_{IL} |

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)