调试过程中遇到的差分电压检测电路的问题

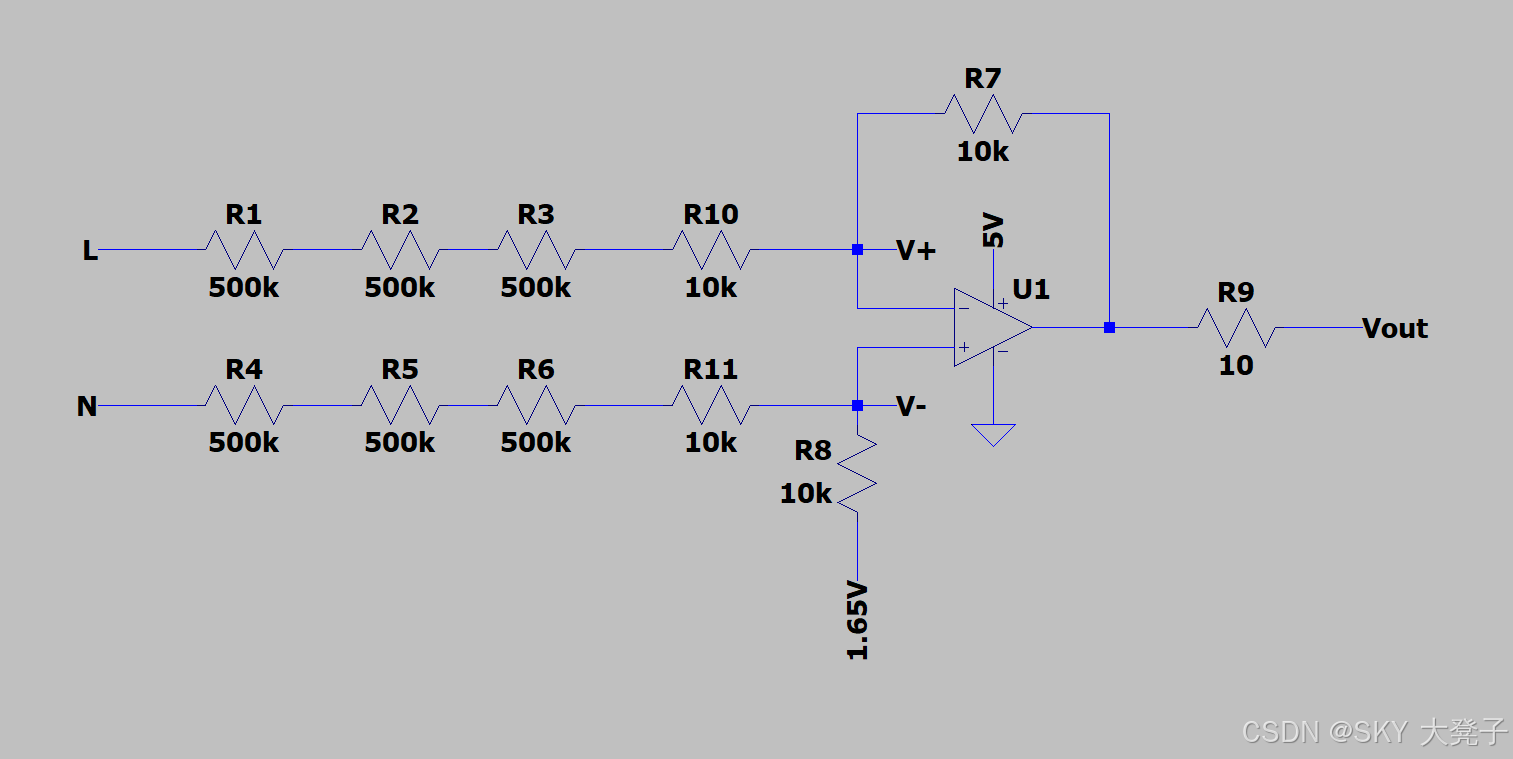

第二张图中,R3右手和R6右手的电压差值可以很容易计算出来,约是1.457V,在PCB layout时往往也会将R10和R11放在靠近运放的地方。在实际应用中,交流作为高压,需要和低压之间有足够的安全距离,另外在对PCB layout时,也会区分高压部分和低压部分,而上面两张图的大阻值分压电阻,就会被放在靠近高压侧的区域,而运放及其周边的阻容器件则会放在低压区域。看第一张图易知,当输入端是交流22

最近在调试电路中发现,交流电压检测电路容易受到外部干扰,导致采样到的电压与实际电压出现较大偏差。原因一部分是由于产品体积小,器件多而密,为考虑安规,而导致采样电路走线过长;另一方面也是发现电路没有考虑到抗干扰的设计。

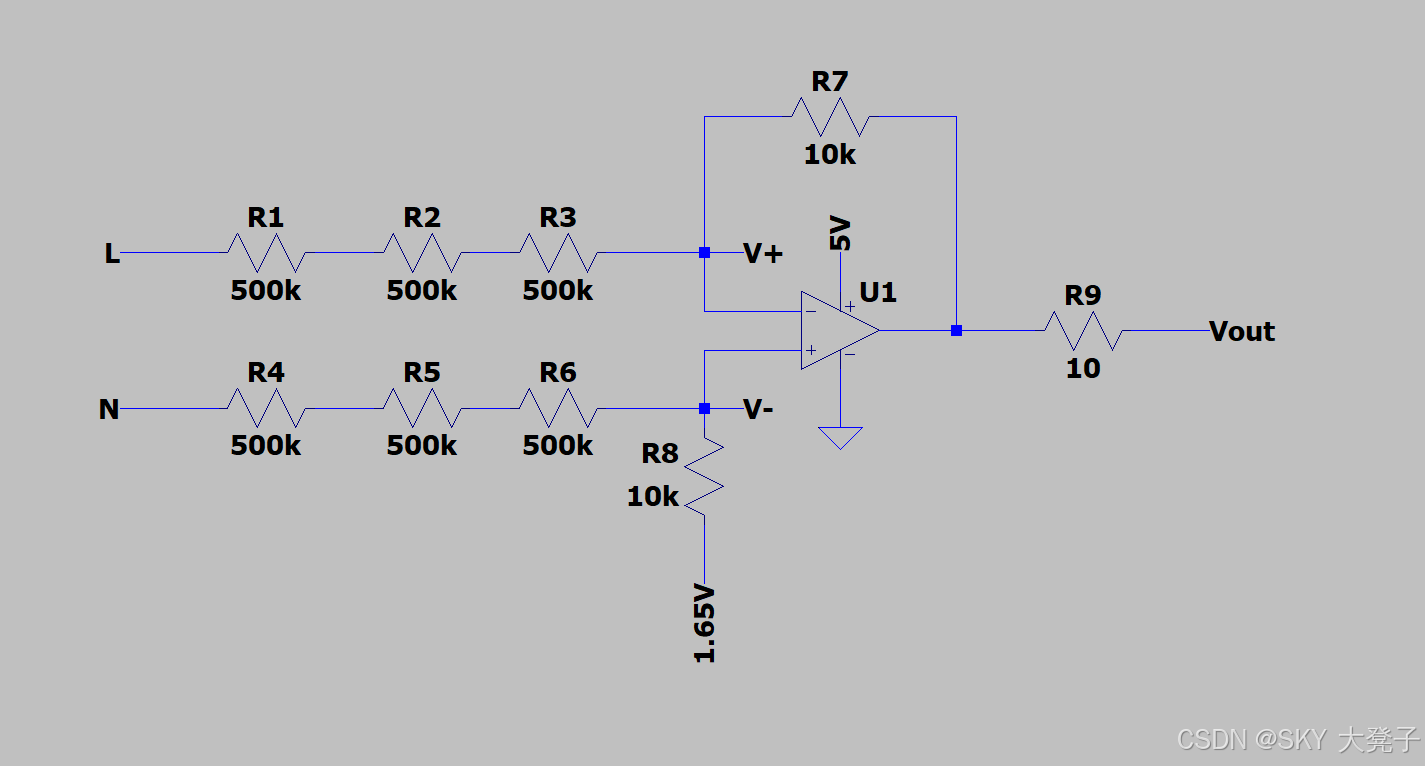

以下是常见的差分电压检测电路图:

对于上面的第二张图,我一度不能理解这样设计的原因,直到最近遇到了问题,才发现第二张图的设计是多么有必要。不知道有多少人能直接说出第二张图的优点?!!!两者看似得到的结果相差不大,但是第二张图在抗干扰方面却能优于第一张图。

看第一张图易知,当输入端是交流220V时,理想情况下,输出端电压波形应是骑在1.65V直流电压上,有效值约为1.47V的正弦波。而第二张图,则是骑在1.65V直流电压上,有效值约为1.457V的正弦波。

在实际应用中,交流作为高压,需要和低压之间有足够的安全距离,另外在对PCB layout时,也会区分高压部分和低压部分,而上面两张图的大阻值分压电阻,就会被放在靠近高压侧的区域,而运放及其周边的阻容器件则会放在低压区域。

第一张图V+和V-在经过R3和R6之后,会有很长一段的走线。由于运放在负反馈状态下存在虚短,V+和V-这两处的电压几乎相等。在电路不干净的时候就可能在走线上耦合到外部的杂讯,进而影响采样的准确性。

第二张图中,R3右手和R6右手的电压差值可以很容易计算出来,约是1.457V,在PCB layout时往往也会将R10和R11放在靠近运放的地方。这样布局后,由于长走线上电压差值为1.457V,相较于图1中长走线上uV或者mV级的电压,抗干扰能力明显增强。

当然,实际电路设计时,往往还会在R8,R7旁边并联电容,在运放的同向端和反相端并联电容以增强抗干扰能力;也可以通过不改变分压比,降低阻值的方式提高电路抗干扰能力(增大功耗)。具体电容的参数需要根据具体的需求和调试结果进行修正。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)