AD 等长设计

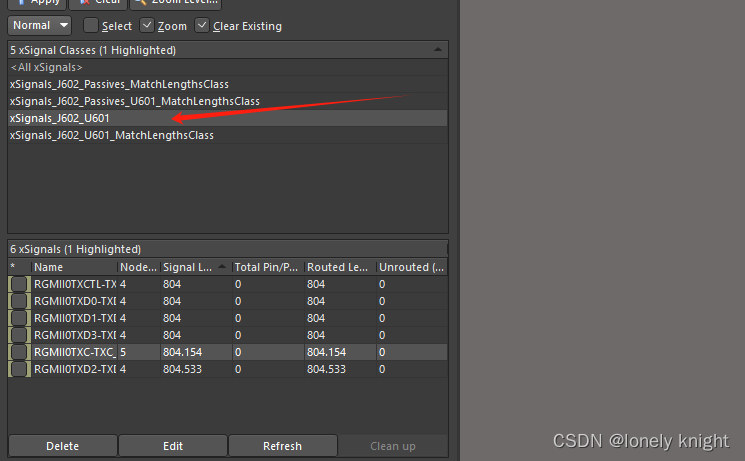

3. 生成后选择器件到器件的等长,并根据长度排序,已信号长度为准(理论上信号长度和走线长度应保持一致,走线长度大于信号长度说明有线头或者断头线)b.等长设计完成后,只保留器件到器件的xSignals,将其余都删除,不然DRC会报错,他默认检查每一段的等长设计。5. 以最长的线段的信号长度为等长目标,将其余线段绕线到统一长度,根据经验一般有两种绕线思路。同一信号层大于8根线需要等长设计的,一般从最中

·

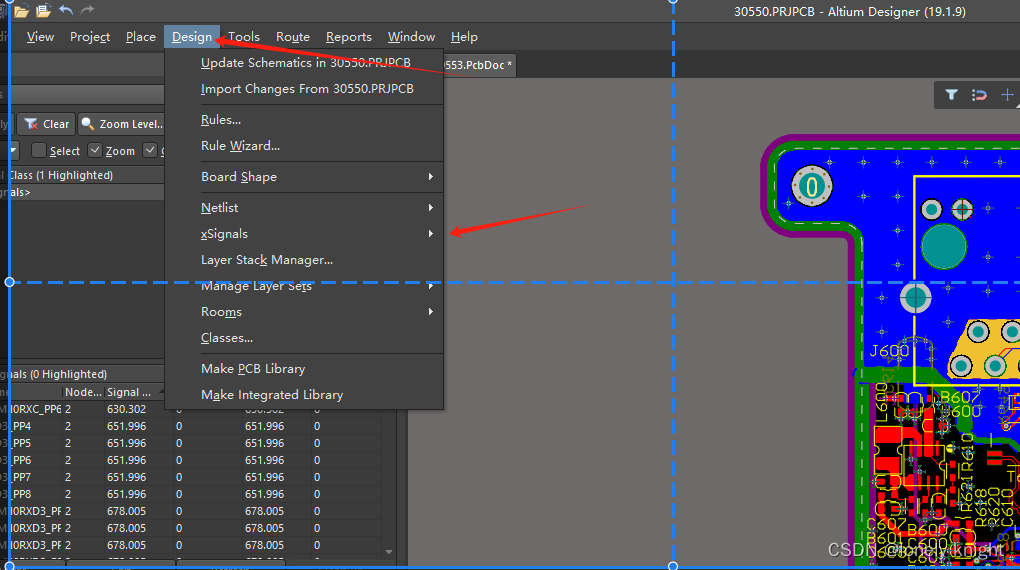

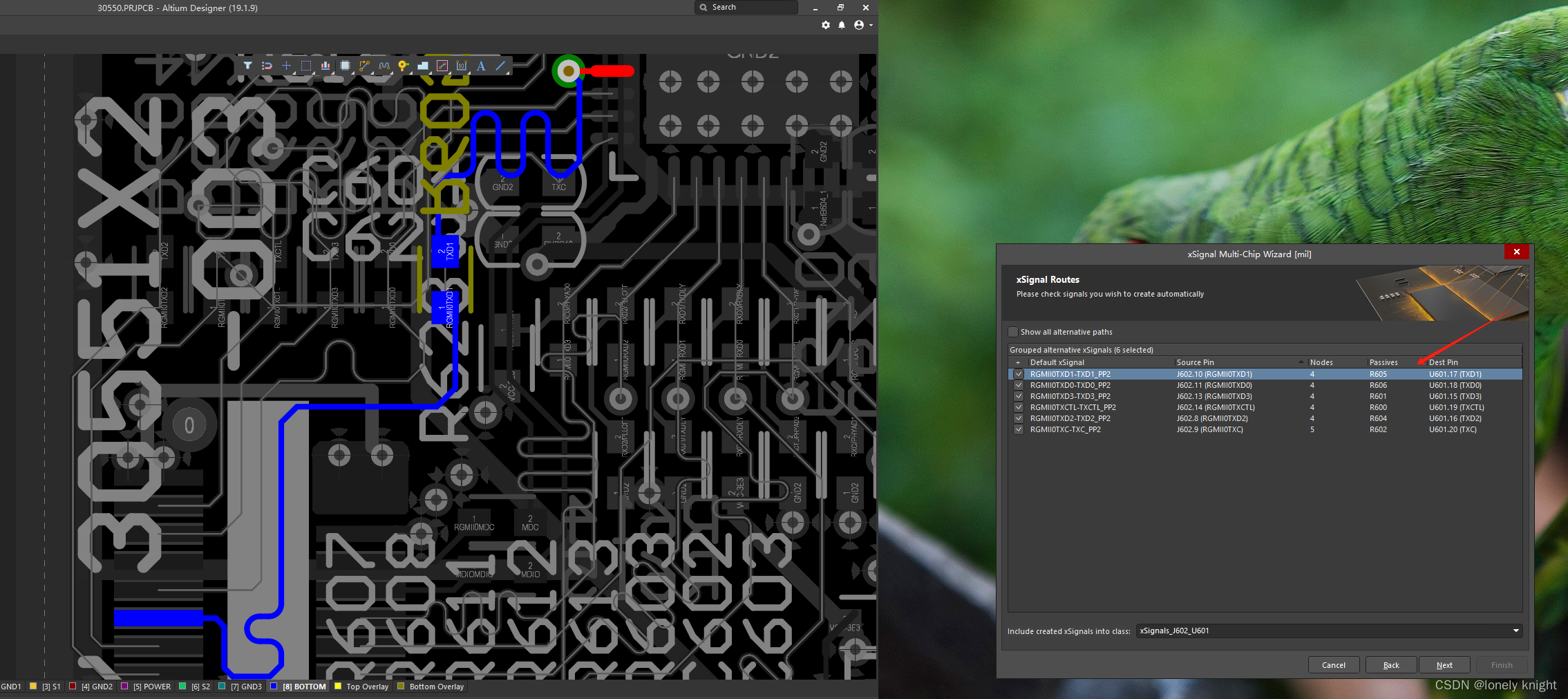

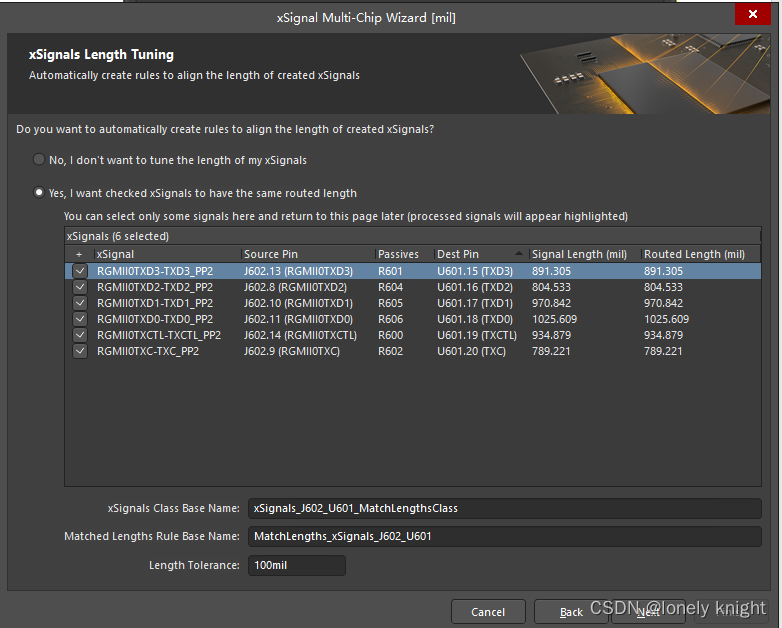

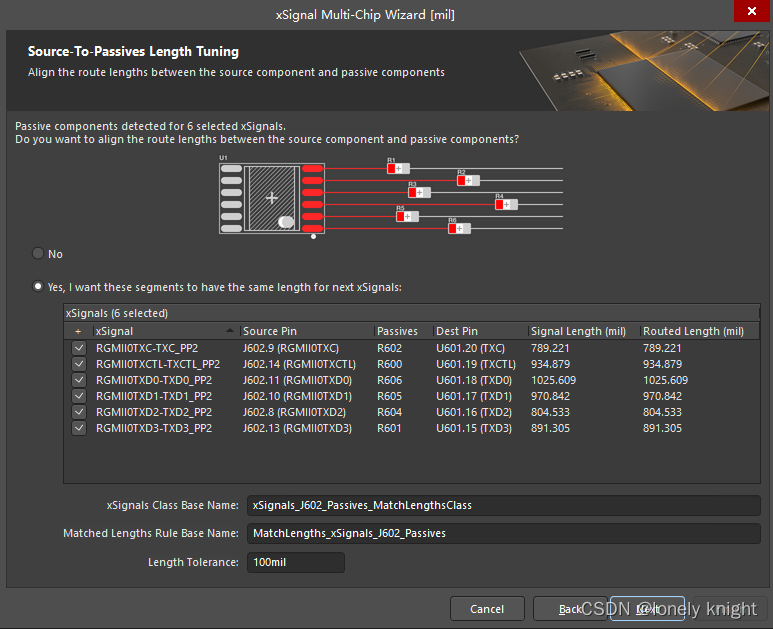

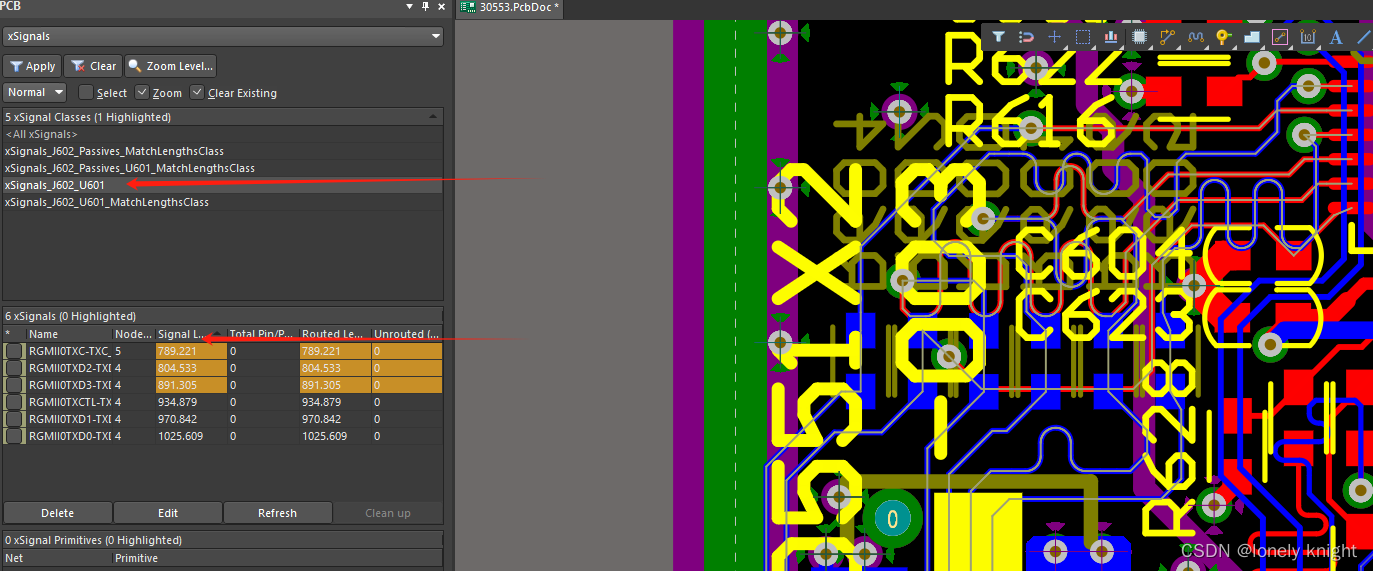

1. 建立等长规则

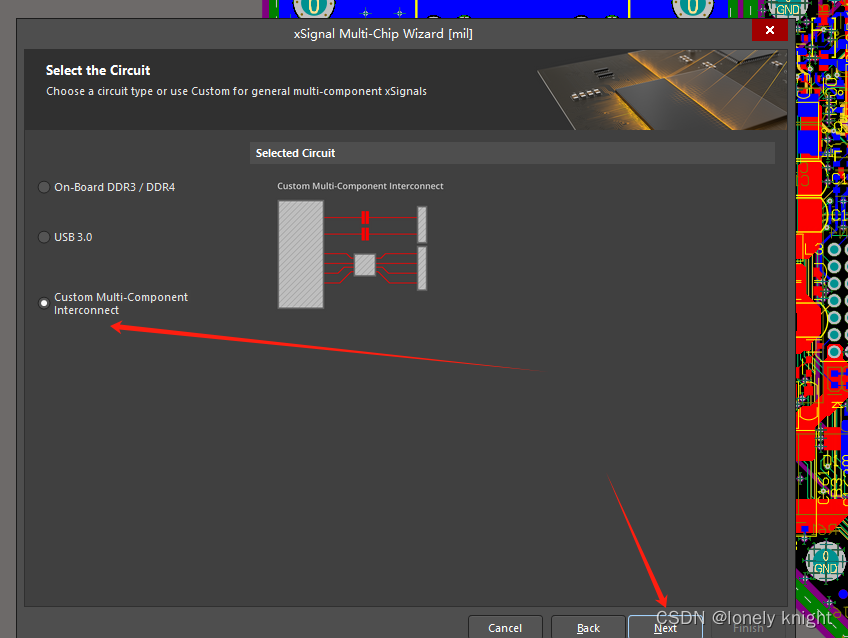

根据引导进行选择

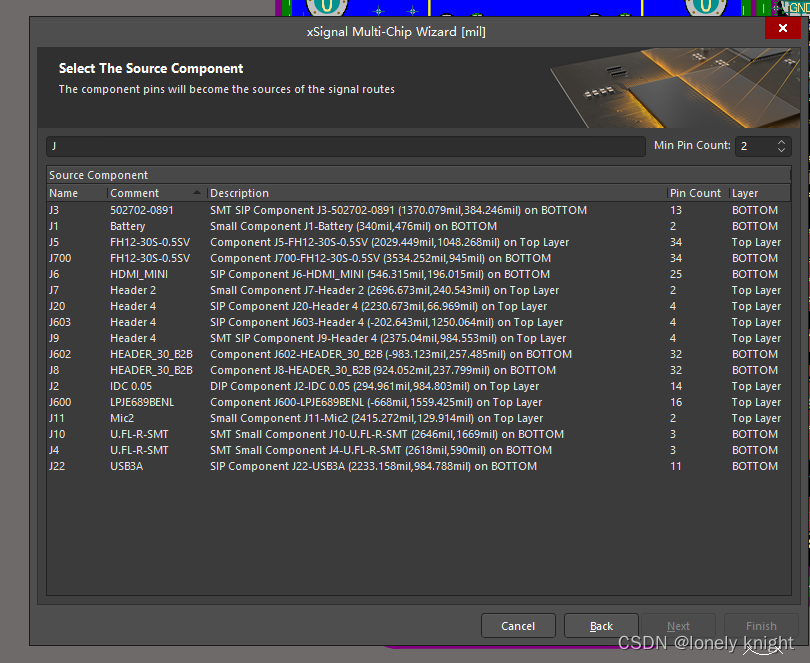

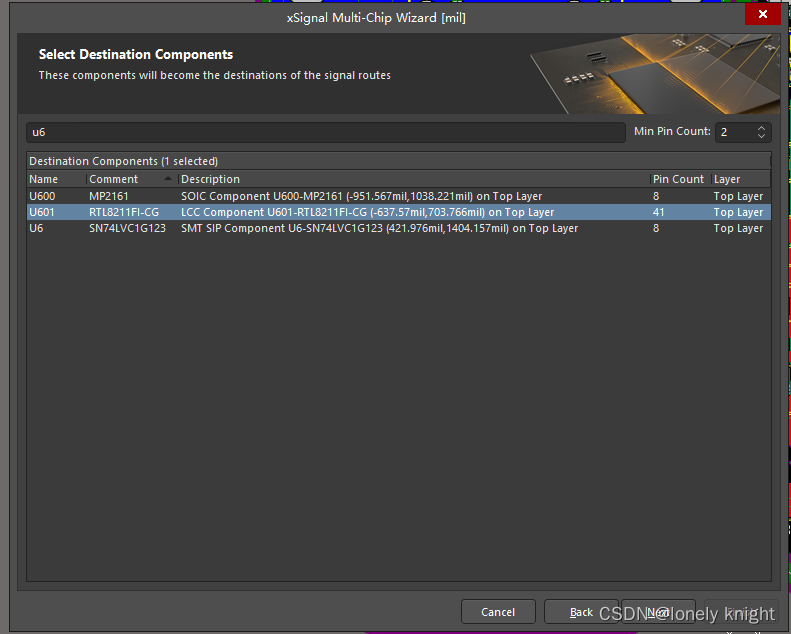

端口器件选择,一般选择引脚数较少的IC或者连接器

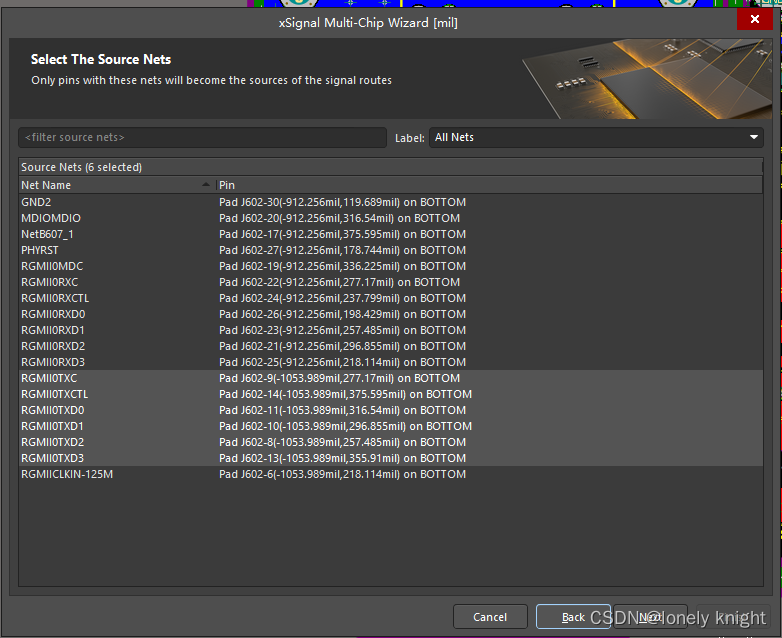

选择要等长的网络

选择第二颗IC或者连接器

2.通路建立后需要确认数据通路正确 不正确的需要更改

- 需要点击每一行确认数据连接是正确的

- PCB要在所有信号层打开的状态

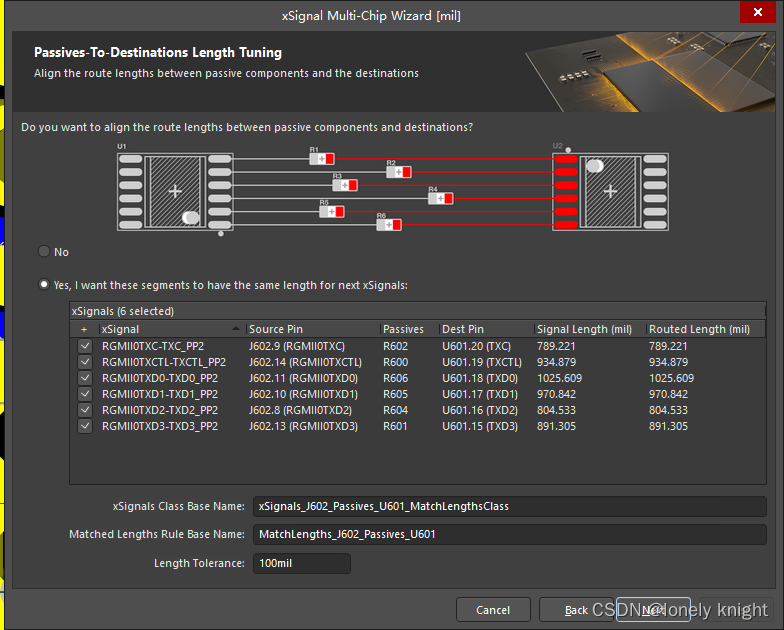

后续所有的都需要生成,不然无法做到自动识别过孔,电阻等长度

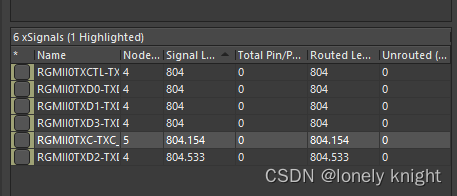

3. 生成后选择器件到器件的等长,并根据长度排序,已信号长度为准(理论上信号长度和走线长度应保持一致,走线长度大于信号长度说明有线头或者断头线)

4. 点击选择高亮的走线,调整走线使其到最短

在这个过程中,可能最长的线段不断变换,要一直重复调整直到这组线最长的线无法再变短

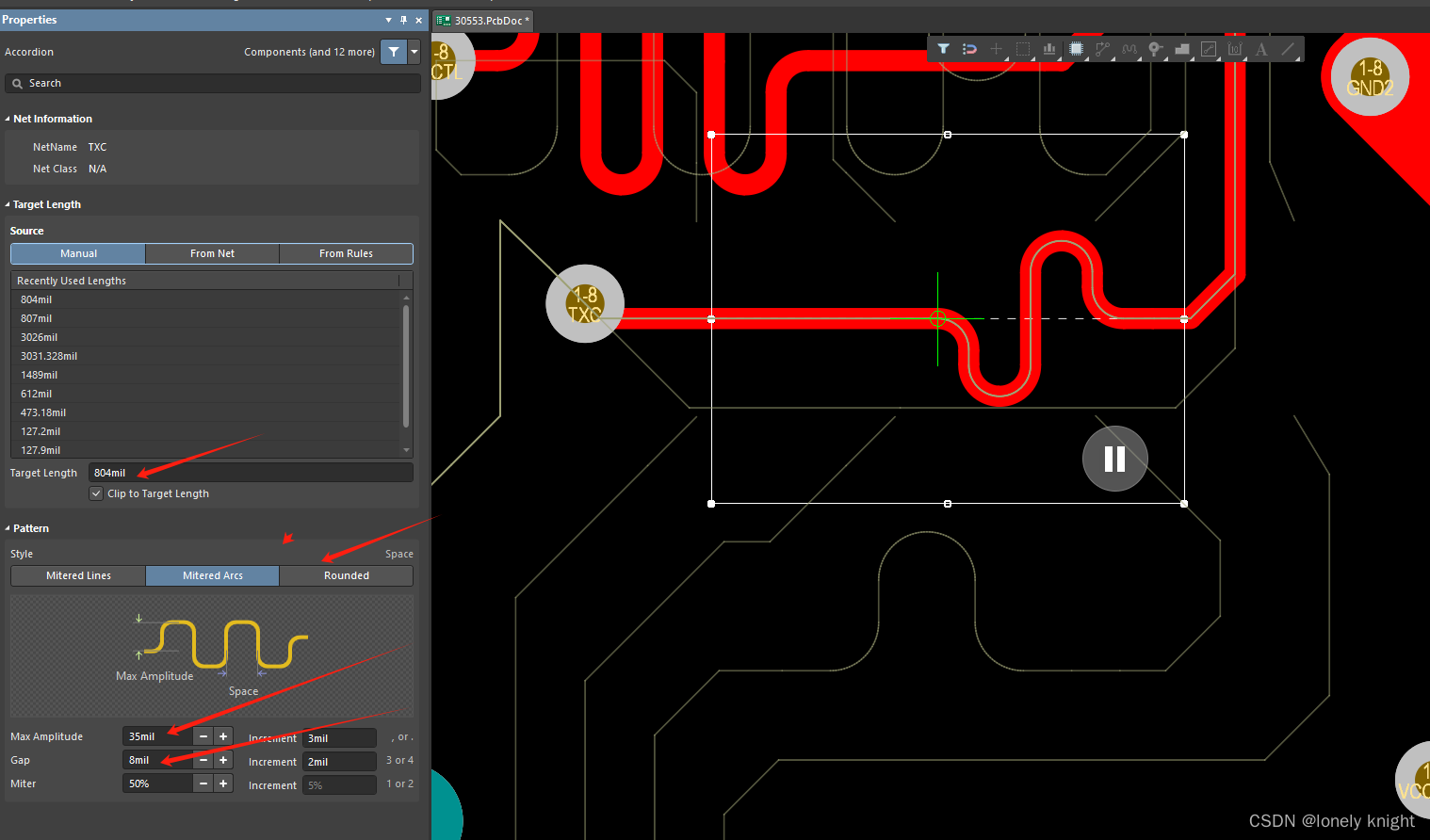

5. 以最长的线段的信号长度为等长目标,将其余线段绕线到统一长度,根据经验一般有两种绕线思路

- 同一信号层少于8根线需要等长设计的,一般从线长最短的开始绕线

- 同一信号层大于8根线需要等长设计的,一般从最中间的信号开始绕线

6. 选择等长走线,找到要等长走线的线,走线开始选择规则如下

- 不等长发生开始的位置做为起点

- 根据信号性质,从源端做为起点

- 查看对应器件PCB设计说明

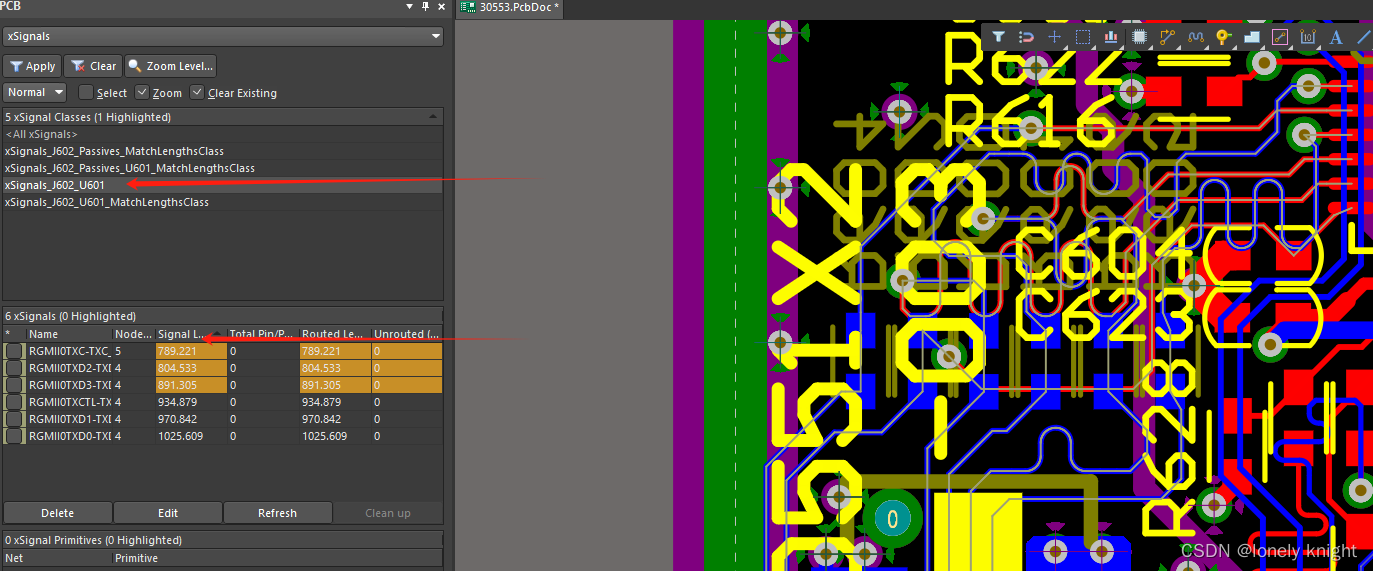

7. 第一根线开始等长,出现第一走线绕线时按下TAP

根据最长线段设置走线长度

根据需要设置绕线类型

根据需求设置绕线间隔和绕线长度

8. 等长设计完成

后记

a.遇到等长设计和高速/模拟区域相邻时,可画一条无网络的辅助线

b.等长设计完成后,只保留器件到器件的xSignals,将其余都删除,不然DRC会报错,他默认检查每一段的等长设计

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)