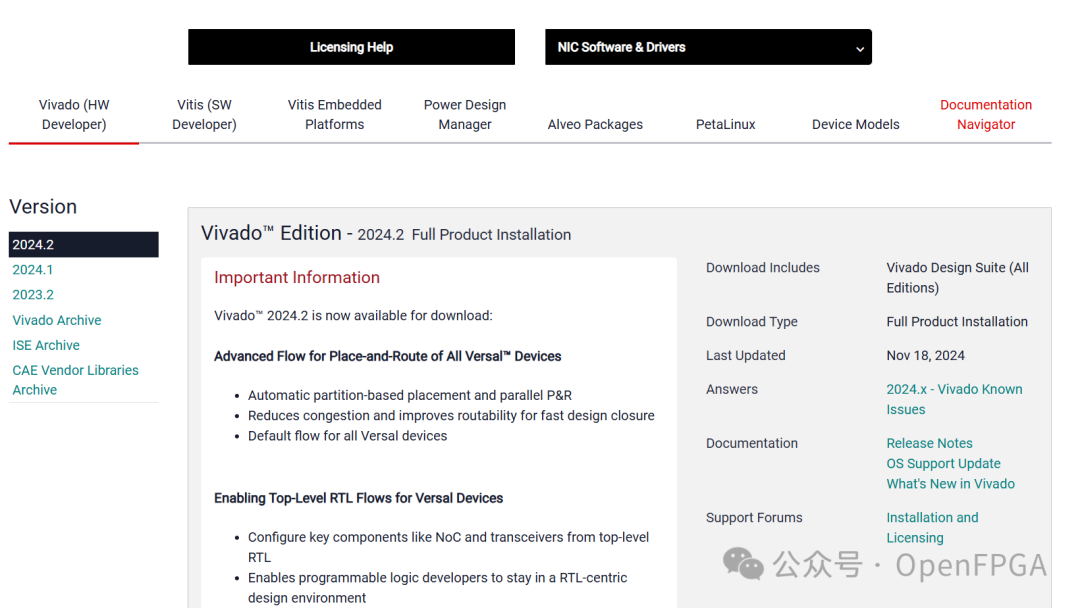

Vivado 2024.2现已推出,可供下载

先放下载链接:https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools.html大小:124.8GB ,Crazy~奔着200G去了文末提供网盘链接。新增特性适用于所有 Versal 器件的快速布局布线新的基于分区的布局和并行布局布线算法减少拥塞以提高可布

先放下载链接:

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools.html

大小:124.8GB ,Crazy~奔着200G去了

文末提供网盘链接。

新增特性

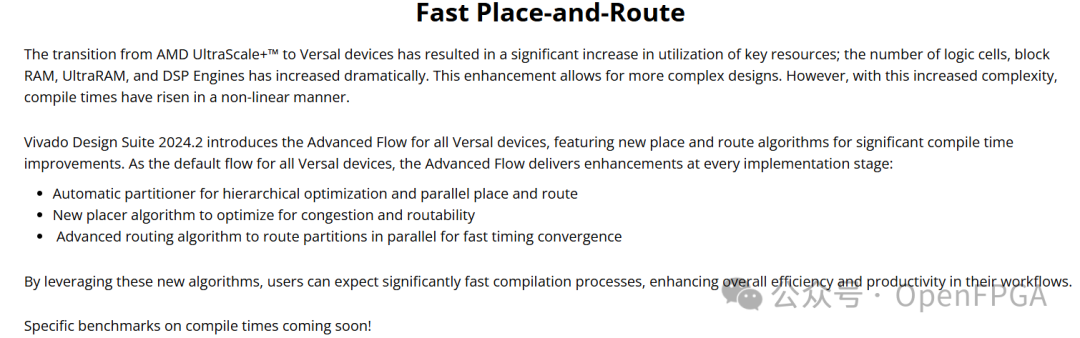

适用于所有 Versal 器件的快速布局布线

-

新的基于分区的布局和并行布局布线算法减少拥塞以提高可布线性

从AMD UltraScale+™到Versal设备的过渡显著提高了关键资源的利用率;逻辑单元、BlockRAM、UltraRAM和DSP引擎的数量急剧增加,随着复杂性的增加,编译时间以非线性的方式增加。Vivado Design Suite 2024.2为所有Versal设备引入了Advanced Flow,采用了新的位置和路由算法,显著改善了编译时间。作为所有Versal设备的默认流程,Advanced flow在每个实施阶段都提供了增强功能,以下是新增(改进)的算法

通过利用这些新算法,可以显著减少编译过程,提高其工作流程的整体效率和生产力。

为 Versal Adaptive SoC 启用顶层 RTL 流程

-

从顶层 RTL 配置 NoC 和收发器等关键组件

-

绕过 IP 集成器,简化复杂设计的流程

升级了NoC功能,引入了“modular NoC”,使RTL用户更容易将NoC功能直接集成到他们的RTL设计中。

GTY(32 Gb/s)、GTYP(PCIe®为32 Gb/s的)和GTM(56 Gb/s或112 Gb/s)收发器等收发器的类似简化流程。新的Versal收发器向导提供了一个围绕GT原语创建的RTL包装器,并允许进行自定义。通过这两个功能,用户可以从其顶级RTL设计中访问Versal设备的关键功能。

快速启动 Versal 处理系统

-

首先启动 PS,并延迟配置可编程逻辑

-

使用 DDR 快速启动操作系统,满足启动顺序要求

Inline HDL for utility IP Faster IP load and configuration

New utility for PDI debug (decode and analyze boot configuration errors)

Pblocks的GUI增强功能

增强型动态功能交换(DFX)平面图可视化和DFX总结报告

其他特性可以查看下面网页:

https://www.amd.com/zh-cn/products/software/adaptive-socs-and-fpgas/vivado/vivado-for-versal.html#place

下载地址

通过百度网盘分享的文件:Vivado2024.2

链接:https://pan.baidu.com/s/1QHp6tc277RL4CQjdxYJLOA?pwd=open

提取码:open

更多推荐

已为社区贡献90条内容

已为社区贡献90条内容

所有评论(0)