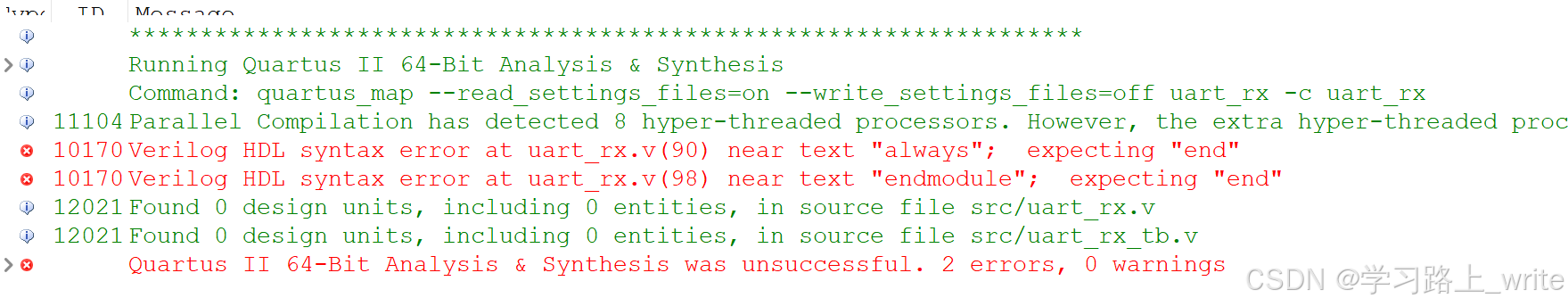

Quartus 软件报错:Error (10170): Verilog HDL syntax error XX near text “always“; expecting “end“

问题解决

·

遇到了报错,通常意味着在你的 Verilog 代码中,一个或多个 always 块没有正确闭合

可能原因:

-

缺少

end关键字:每个always块必须以end关键字结束。如果你的always块没有闭合,编译器就会抛出这个错误。 -

嵌套错误:在

always块内部可能还有其他结构(如if,for,while等),这些结构也需要正确闭合。如果内部结构的end关键字缺失或位置不正确,也可能导致编译器错误地指向always块。 -

代码格式问题:有时候,错误的缩进或格式可能导致编译器难以正确解析代码结构,尽管这通常不会导致直接指向

always的错误,但值得检查以确保代码清晰易读。

解决:

- 检查

always块:确保每个always块都有一个对应的end。- 检查嵌套结构:确保所有嵌套的结构(如

if,for,case等)也都正确闭合。- 代码审查:仔细审查代码,特别是错误提示附近的代码,看是否有遗漏或错误的关键字。

- 借助代码编辑器的帮助:大多数现代代码编辑器都有语法高亮和错误提示功能,这些功能可以帮助你快速定位问题。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)