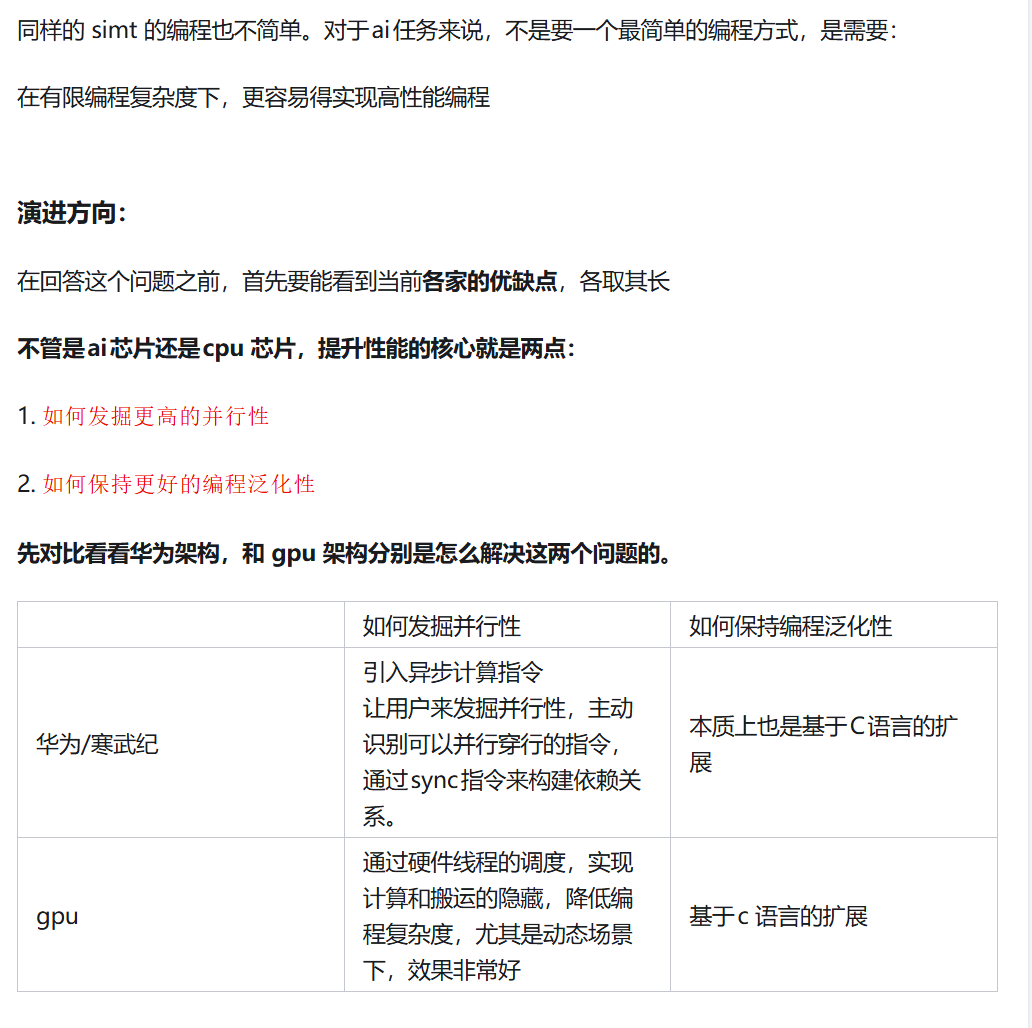

NPU下一代架构设计,哪一种更适合LLM推理?一.类SIMT+ TC 2.纯SIMD+DSA?

摘要:AI芯片发展正经历从专用架构(DSA)向通用性转变。早期专注于CNN加速的SIMD+DSA架构已难以满足大模型的动态控制流、不规则访存和算子灵活性需求。当前趋势是采用SIMT+张量专用核架构,通过多线程调度隐藏延迟。专家建议采用纯SIMD+SMT技术路线,强调应注重提升硬件调度能力和算力实际利用率,而非盲目转向SIMT。国内AI芯片行业已进入比拼泛化性和实用性的下半场竞争阶段。

·

NPU下一代的架构设计,哪个架构更适合大模型部署

回顾跑深度学习神经网络到大模型的硬件架构变化

- 一开始CV类CNN,可用CPU的向量并行写算子

-后面NPU的架构是SIMD+DSA

- 到如今大模型,似乎都走SIMT+张量专用核

可以看到一个趋势是Nvidia的tensor core越来越像NPU的专用加速单元,tensor memory专用,DMA来搬运数据

而通用可编程模块,从SIMD到SIMT的转变原因是什么?

- SIMD:同PC同执行同控制流,一起执行整个向量必须同步

SIMT:以warp为单位独立调度,虽然

NV warp = 32 thread

AMD wavefront = 64 thread

单warp 内,它们物理上确实像 32/64 lane的 SIMD,单SIMT执行模型的核心在于不同warp可以有不同PC,硬件快速切换指令调度来隐藏延迟

大模型部署的三大刚需

① 动态控制流

生成式Decoder = 无限if+loop

② 不规则访存

-

KV cache 索引

-

散点/聚集

-

稀疏访问

SIMT 靠多线程隐藏延迟

SIMD 要求对齐连续,根本扛不住。

③ 算子灵活性

下一代模型天天变架构:

-

MoE

-

新Attention

-

新Norm

-

新激活

编程性也不好说谁好谁坏,毕竟dsl层出不穷,总要根据需求设计对应的dsl

更多推荐

已为社区贡献68条内容

已为社区贡献68条内容

所有评论(0)