USB3.0 / USB3.1 / USB3.2 真正差异 + Tx / Rx 电容原理解析

在日常开发中,我们经常会听到:🎯先来一张清晰的对比表👇📌注意:从 USB 3.0 到 USB 3.2,它们的物理层都遵循一个共通的架构:TX:发送端 PHYRX:接收端 PHYAC Coupling Capacitor:串联在 TX 端差分对中Differential Pair:成对差分线,大多数板里用 TP/TM 标记⚠️这句话是设计高速 USB 成败的根本。这是最容易被误解的地方。从硬件

🎯🚀 USB3.0 / USB3.1 / USB3.2 真正差异 + Tx / Rx 电容原理解析

从理论到实战,带你看懂超级高速 USB 的物理层如何影响你的硬件设计

🔥第一章:USB 3.x 到底有几个版本?

在日常开发中,我们经常会听到:

- USB 3.0

- USB 3.1 Gen1 / Gen2

- USB 3.2

- 甚至还有 USB4

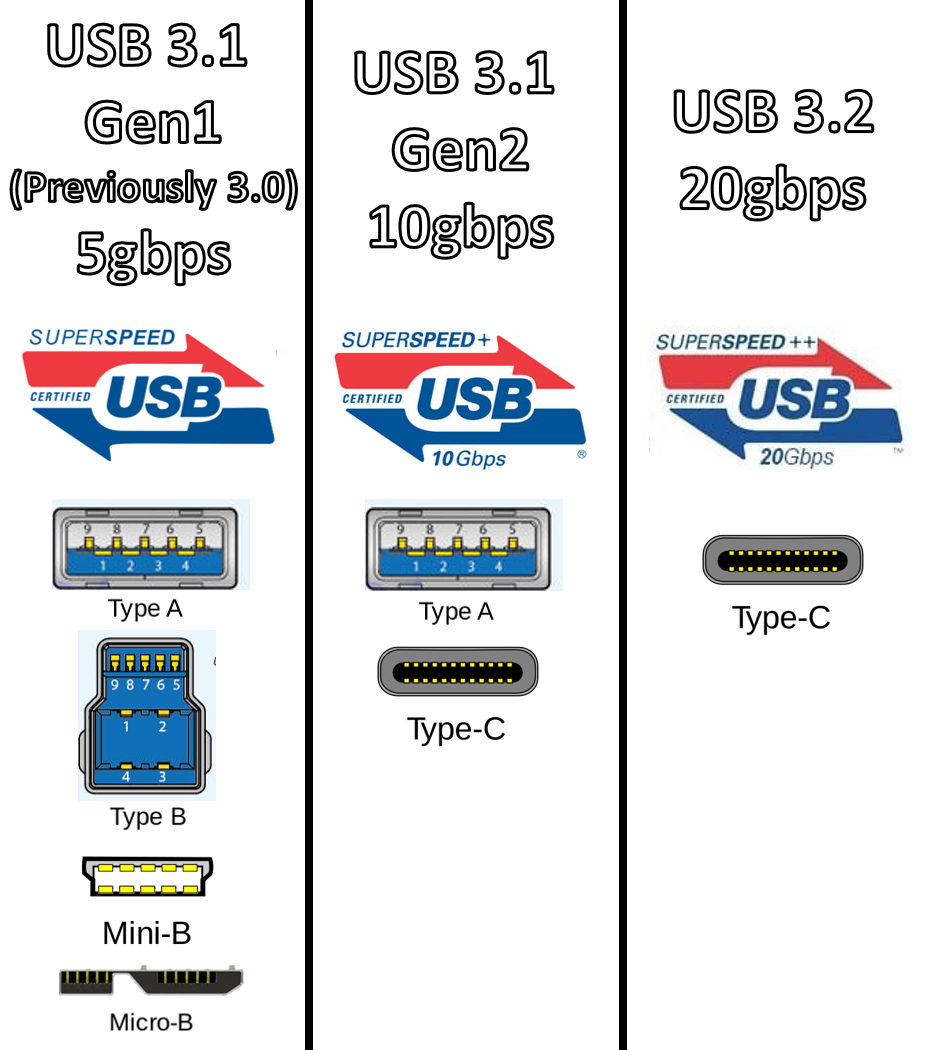

🎯先来一张清晰的对比表👇

| 名称 | 规格名称 | 速率 | 通道结构 |

|---|---|---|---|

| USB 3.0 | SuperSpeed | 5 Gbps | 1 lane |

| USB 3.1 Gen1 | SuperSpeed | 5 Gbps | 1 lane |

| USB 3.1 Gen2 | SuperSpeed+ | 10 Gbps | 1 lane |

| USB 3.2 Gen1x2 | SuperSpeed | 5 Gbps ×2 | 2 lanes |

| USB 3.2 Gen2x2 | SuperSpeed+ | 10 Gbps ×2 | 2 lanes |

📌注意:

- USB 3.0 = USB 3.1 Gen1(是同一回事)

- 你说的 USB3.2 不一定是 20 Gbps,要看具体版本

🚗第二章:USB 3.x 高速物理结构一览

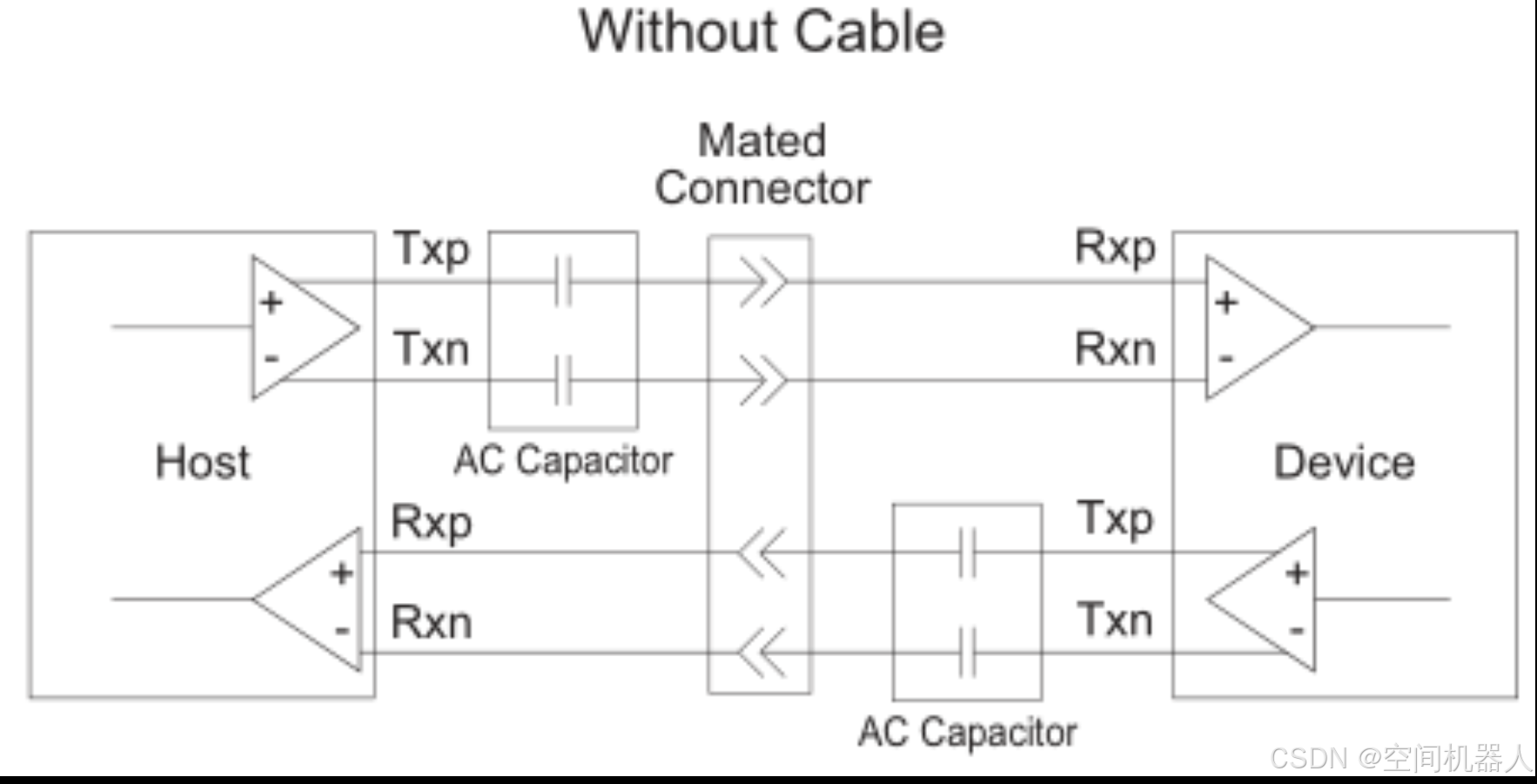

从 USB 3.0 到 USB 3.2,它们的物理层都遵循一个共通的架构:

TX (PHY) → AC Coupling → Differential Pair → RX (PHY)

- TX:发送端 PHY

- RX:接收端 PHY

- AC Coupling Capacitor:串联在 TX 端差分对中

- Differential Pair:成对差分线,大多数板里用 TP/TM 标记

⚠️这句话是设计高速 USB 成败的根本。

🎯第三章:为什么 TX 一定要串电容,而 RX 不用?

这是最容易被误解的地方。

从硬件工程的角度来说,这里面隐藏着 USB 3.x 的本质:高速差分 + 共模偏置 + 编码结构。

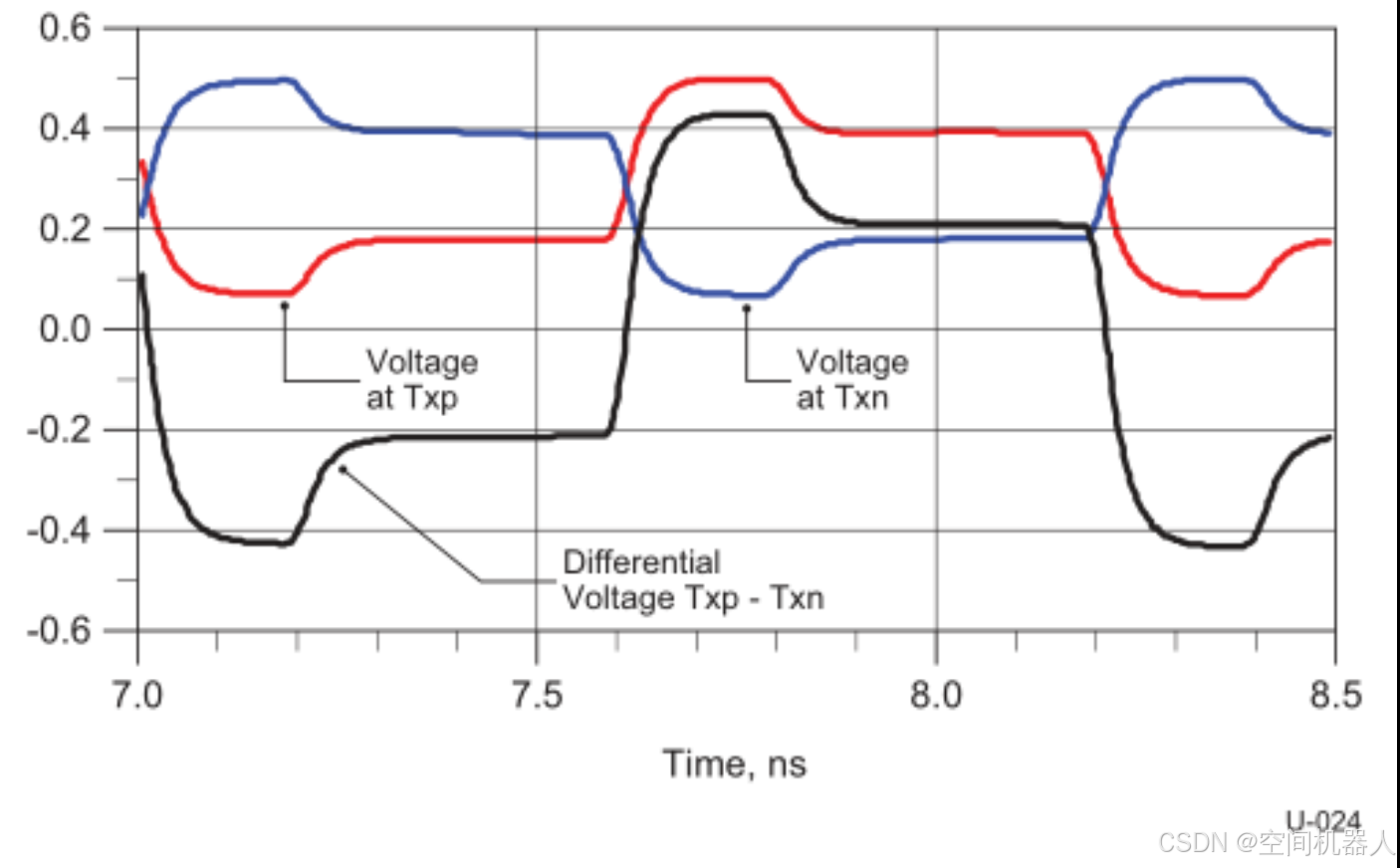

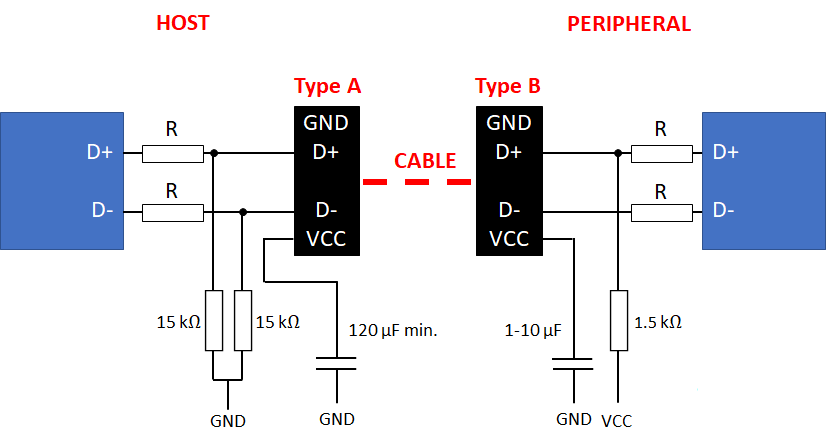

🧠 1、共模电压不同,不能直连

不同芯片(比如 SoC / USB Hub / PHY)之间的 TX 端:

- 可能有不同的 DC 偏置电平

- 可能根本不共享参考电压

若直连,会导致 RX 端无法正确判决数据,出现误码或掉链。

而串电容的目的是非常简单——

👉 把直流分量隔断,只传高频信号。

这就是所谓的“AC 耦合”。

📌 2、USB 3.x 用的是 8b/10b 编码

USB 3.x 使用 8b/10b 编码:

- 确保长期直流平衡

- 但在短时间内仍可能出现直流分量

没有 AC 耦合,

➡ 全链路直流偏置漂移

➡ RX接收端难以建立正确判决阈值

➡ 链路训练失败

这是一个物理层约束,不是抽象理论。

🚫 3、为什么 RX 不能串电容?

因为 RX 端有自己的偏置网络和终端匹配结构,它基于内部共模参考来判决输入信号。

串了电容后:

- RX 无法建立稳定的共同偏置

- 信号变成了“浮空”

- 串联电容在 RX 端变成了性能杀手

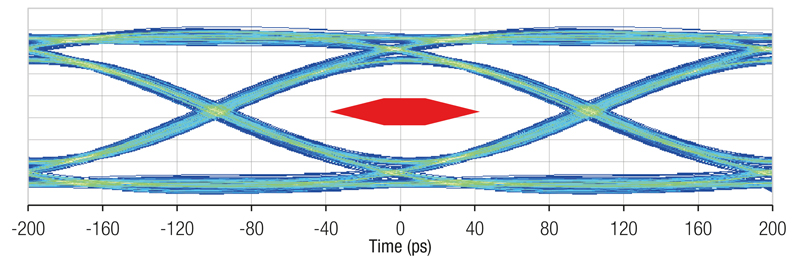

📊 支持图示:USB3.x 发送/接收结构(简化版)

📈 第四章:USB3.1 / 3.2 是如何升级的?

USB 3.1 / 3.2 相比 USB 3.0 不再是“简单提速主频”。

它的演进体现在:

✨ USB 3.1 Gen2(10 Gbps)

- 速度翻倍

- 物理层仍然 TS/AC coupling

- 系统眼图更难保持稳

🚀 USB 3.2 Gen2x2(20 Gbps)

- 用到了 2 条通道 × 10 Gbps

- 这意味着两组差分线都要做 AC 耦合

- 对 PCB 的介质、阻抗控制、串扰要求大幅提高

🧪 第五章:工程里面真正要关心的

在实际量产项目里(尤其是车载环境),你要考虑:

📍 1、AC 电容放在哪里?(至关重要)

✅ 正确做法:(靠近 TX PHY 放)

TX+ ── C ─────────────────────── RX+

TX− ── C ─────────────────────── RX−

❌ 错误做法:

TX+──── C ── ESD ── RX+

→ ESD 在中间,链路稳定性直接掉半档

🧰 2、器件选型与布局

推荐用:

- 0402 / 0201 电容

- 100 nF(标配)

- 低 ESL / ESR

这些细节虽小,却是能否稳定枚举 + 耐温耐干扰的关键。

🧪 3、车规环境 VS 普通消费级

在车载项目里:

- EMC 要求极严

- 温度从 -40 到 85℃

- 地弹 / 瞬态噪声很狠

这就导致你下面 3 点必须做到:

🔹 AC 电容值稳定

🔹 TX 端放置靠近 PHY

🔹 RX 不要串电容并保证 bias network

📌 真实案例:USB3.1 Gen2 在流媒体后视镜里的调试

项目背景:

🚗 CMS 设备

🚗 USB3.1 Gen2 接摄像头(10 Gbps)

🚗 电源噪声大、机械振动多

问题复现:

| 情况 | 结果 |

|---|---|

| TX 串电容靠近连接器 | ❌ 无法枚举 |

| TX 串电容靠近 PHY | ✅ 稳定 |

| RX 端加电容 | ❌ 链路未锁定 |

这个规律一查:

➡️ 原来 RX 偏置网络被破坏了

最终改进效果:

✔ AC 电容固定靠近 PHY

✔ 同时加 ESD 在接近接口一侧

✔ PCB 增加过孔减小串扰

最终得到:

🎉 10 Gbps 稳定链路

🎉 全车温度可靠

🎉 EMC 通过

🧠 结论

✅ USB 3.x 物理层设计规范

1️⃣ TX 端必须串 AC 耦合电容

2️⃣ RX 端绝对不串电容

3️⃣ 电容靠近 TX PHY

4️⃣ RX 端保持 bias network 完整

5️⃣ PCB 阻抗控制严格

6️⃣ EMC 层次要能分离高速、共模

🎯 记住这 6 条,

你在设计高速 USB 成败的概率将自动从 80% 降到 10%。

📌 图示总结

更多推荐

已为社区贡献18条内容

已为社区贡献18条内容

所有评论(0)