DDR5 SDRAM 4.17 读训练模式(Read Training Pattern)详解(JEDEC Standard No.79-5D)

本文详细解析DDR5 SDRAM的读训练模式机制,包括串行和LFSR两种核心模式。读训练模式通过MR25-MR31寄存器配置,支持固定模式输出和LFSR生成序列,用于内存接口训练。LFSR模式采用8位Galois结构,支持两个独立实例分配,可切换为时钟模式。文章还阐述了连续突发模式的操作规则、时序要求及典型配置示例,强调使用前必须禁用CRC功能。该内容整理自JEDEC标准文档,可直接用于工程实践参

本文为作者原创内容,首发于同名微信公众号【TechShareMore】,首发时间:2026年2月11日,已获得作者本人独家授权,同步发布于CSDN。

本文完整整理自JEDEC Standard No.79-5D标准文档第4.17章节,聚焦DDR5 SDRAM的读训练模式(Read Training Pattern)核心机制、模式配置、LFSR生成规则、示例序列及时序要求,结构清晰易读,可直接用于技术分享或工程实践参考。

4.17 读训练模式(Read Training Pattern)

读训练模式的核心作用是在启用DRAM写操作前,让主机读取已知数据模式,完成内存接口训练。由于DDR5支持更高工作频率,简单重复模式已无法满足训练需求,因此引入线性反馈移位寄存器(LFSR)模式,同时保留串行模式,并支持连续突发输出,适配不同训练场景。

核心基础特性

1.触发方式:主机向MR31地址发送MRR命令,DRAM返回BL16格式的读训练模式数据(忽略MR0中的突发长度设置)。

2.CRC约束:使用读训练模式前必须禁用CRC功能,连续突发模式下需额外确保读CRC已禁用。

3.模式分类:支持两种核心模式(串行模式/Serial、LFSR模式),LFSR模式可衍生出高频时钟模式;支持两种输出方式(MRR命令触发/默认、连续突发输出)。

4.寄存器依赖:模式配置、种子值、反转设置、LFSR分配需通过MR25-MR30寄存器编程,未编程时使用上电默认值。

5.状态保留:退出连续突发模式后,DRAM不保存当前LFSR状态,可能清空MR26-MR30配置,再次使用需重新编程。

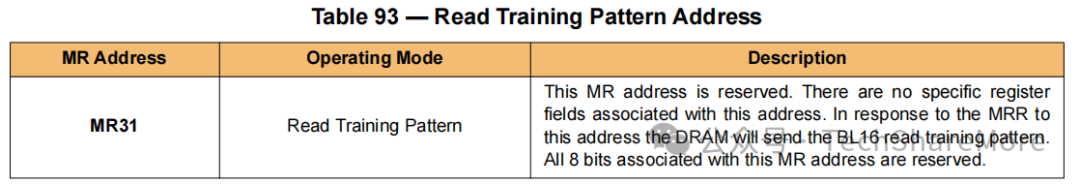

Table 93 - Read Training Pattern Address(读训练模式地址表)

4.17.1 概述(Introduction)

本节详细说明读训练模式的配置方式、支持的操作模式及核心规则,是后续功能实现的基础。

1. 模式寄存器配置(关键MR地址定义)

读训练模式的所有参数通过专用模式寄存器配置,核心寄存器及功能如下:

|

MR地址 |

操作模式 |

核心描述 |

默认值 |

|

MR25 |

读训练模式设置 |

控制模式格式、LFSR选项、连续突发模式 |

OP[0]=0(Serial)、OP[1]=0(LFSR0)、OP[2]=0(LFSR1)、OP[3]=0(默认模式) |

|

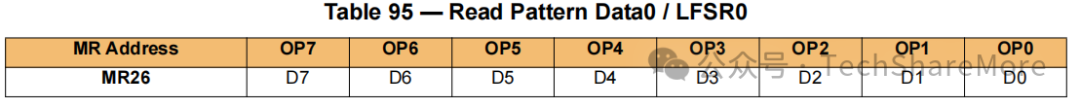

MR26 |

Read Pattern Data0/LFSR0 |

串行模式下存储数据位D7-D0,LFSR模式下存储LFSR0种子 |

0x5A |

|

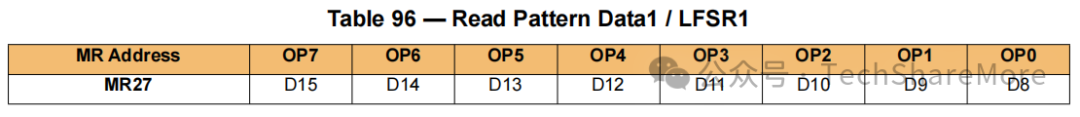

MR27 |

Read Pattern Data1/LFSR1 |

串行模式下存储数据位D15-D8,LFSR模式下存储LFSR1种子 |

0x3C |

|

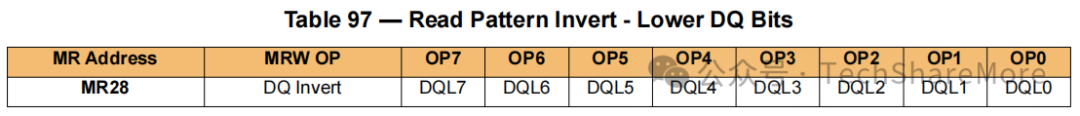

MR28 |

Read Pattern Invert - Lower DQ Bits |

控制低字节DQ位(x4/x8/x16通用)的模式反转 |

0x00 |

|

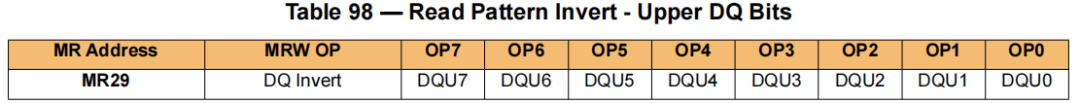

MR29 |

Read Pattern Invert - Upper DQ Bits |

控制x16器件高字节DQ位的模式反转 |

0x00 |

|

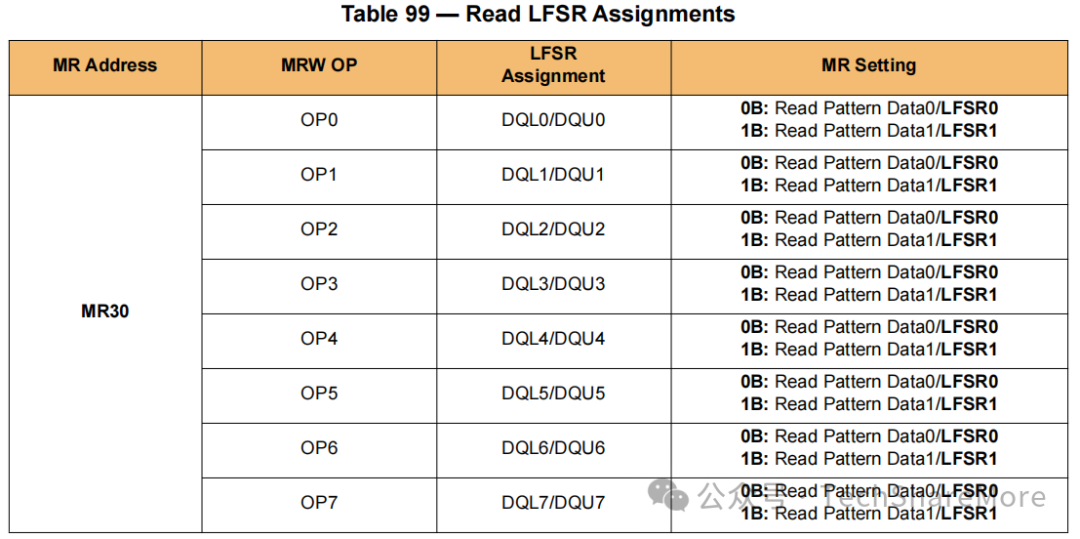

MR30 |

Read LFSR Assignments |

配置每个DQ通道使用LFSR0还是LFSR1 |

0xFE |

|

MR31 |

Read Training Pattern |

触发读训练模式的MR地址(无寄存器字段,仅用于MRR命令) |

- |

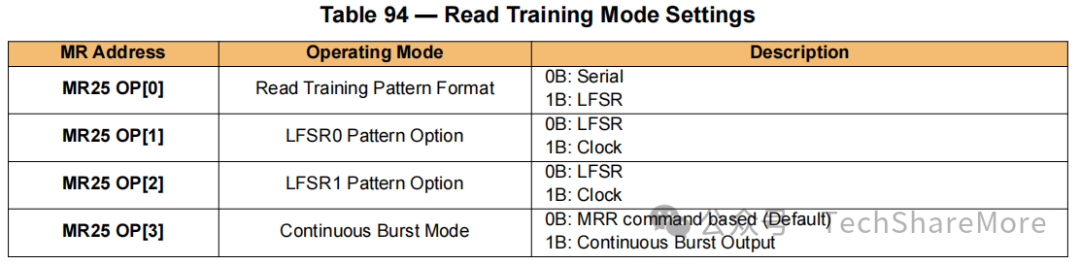

Table 94 - Read Training Mode Settings(读训练模式设置表)

Table 95 - Read Pattern Data0 / LFSR0(数据0/LFSR0寄存器表)

Table 96 - Read Pattern Data1 / LFSR1(数据1/LFSR1寄存器表)

Table 97 - Read Pattern Invert - Lower DQ Bits(低字节DQ反转寄存器表)

Table 98 - Read Pattern Invert - Upper DQ Bits(高字节DQ反转寄存器表)

2. 核心操作规则

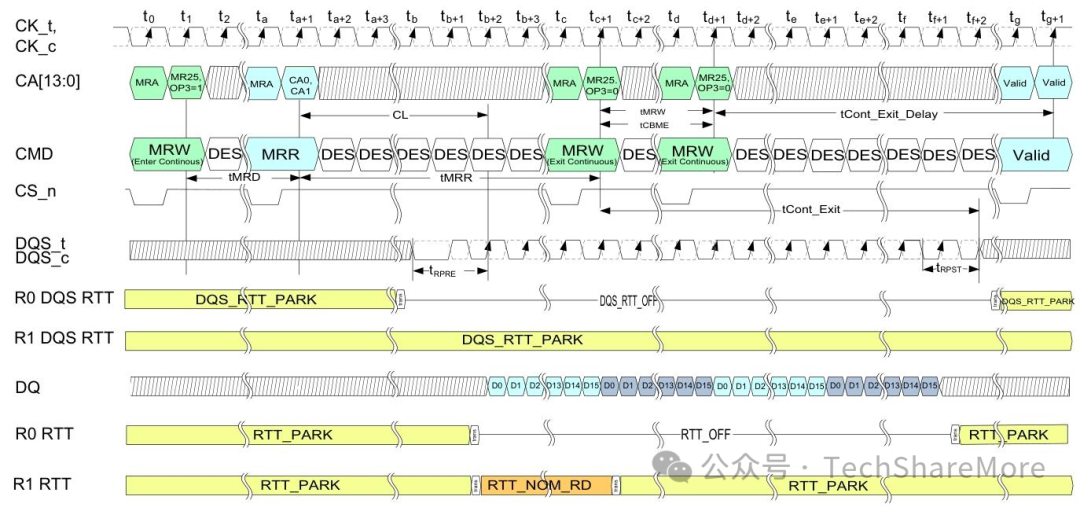

-连续突发模式配置:通过MRW命令设置MR25:OP[3]=1启用,MRR访问MR31后自动持续输出模式,需通过MRW设置MR25:OP[3]=0退出(需发送两次MRW确保稳定退出)。

-连续突发模式约束:仅允许MRR(仅MR31地址)和退出连续突发的MRW命令,其他MRR地址无效,需复位恢复。

-ODT设置:连续突发模式下,目标rank的DQ ODT设为RTT_OFF、DQS ODT设为DQS_RTT_OFF;非目标rank需将RTT_PARK编程为与RTT_NOM_RD一致(如需提供终止)。

-寄存器默认值恢复场景:进入自我刷新、掉电、退出连续突发模式时,MR26-MR30的配置可能恢复默认值,需重新编程。

3. 两种核心模式说明

-串行模式(Serial,MR25:OP[0]=0):通过MR26/MR27存储16位固定模式,支持按DQ通道独立反转,适用于低频率场景。

-LFSR模式(MR25:OP[0]=1):基于8位Galois LFSR生成模式,支持两个独立LFSR实例(LFSR0/LFSR1),适配高频总线,可切换为时钟模式(仅输出0/1交替的高频时钟)。

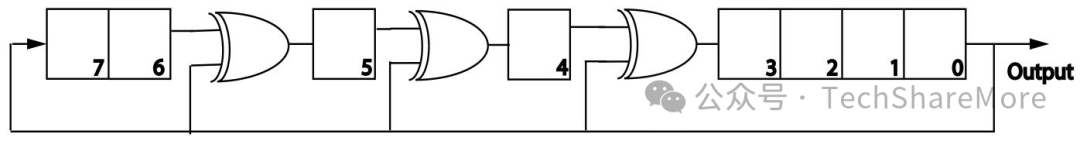

4.17.2 LFSR模式生成(LFSR Pattern Generation)

LFSR模式是DDR5高频场景下的核心训练模式,其生成逻辑、配置规则及操作约束如下:

1. LFSR核心参数

-多项式:采用Galois LFSR,多项式为

![]()

。

-实例数量:两个独立LFSR(LFSR0/LFSR1),分别使用MR26/MR27作为种子寄存器,支持不同DQ通道分配不同LFSR实例。

-输出频率:每个UI(单位间隔)更新一次输出值,BL固定为16。

Figure 95 - Read Training Pattern LFSR(读训练模式LFSR逻辑图)

2. 关键配置规则

-种子寄存器:MR26(LFSR0)和MR27(LFSR1)的种子值决定初始输出,若设为0x00,LFSR将输出恒定0模式。

-LFSR分配:通过MR30配置每个DQ通道(DQL0-DQL7、DQU0-DQU7)使用LFSR0(0B)或LFSR1(1B),实现不同通道独特模式,覆盖串扰场景。

Table 99 - Read LFSR Assignments(LFSR分配表)

-时钟模式选项:

- MR25:OP[1]=1:LFSR0切换为时钟模式,仅分配给LFSR0的DQ通道输出0/1交替信号(首UI为0)。 - MR25:OP[2]=1:LFSR1切换为时钟模式,规则同上。 -LFSR状态更新:仅当处于LFSR模式且未启用时钟模式时,MRR访问MR31才会更新LFSR状态;串行模式或时钟模式下,LFSR状态保持不变。

3. 反转设置

-

低字节DQ(DQL0-DQL7)通过MR28控制反转,高字节DQ(DQU0-DQU7,仅x16)通过MR29控制。

-

寄存器中某bit设为1时,对应DQ通道的输出模式反转;设为0则保持原模式。

4.17.3 读训练模式示例(Read Training Pattern Examples)

原文提供3个典型示例,涵盖串行模式、LFSR模式、LFSR时钟模式,核心配置及输出特点如下:

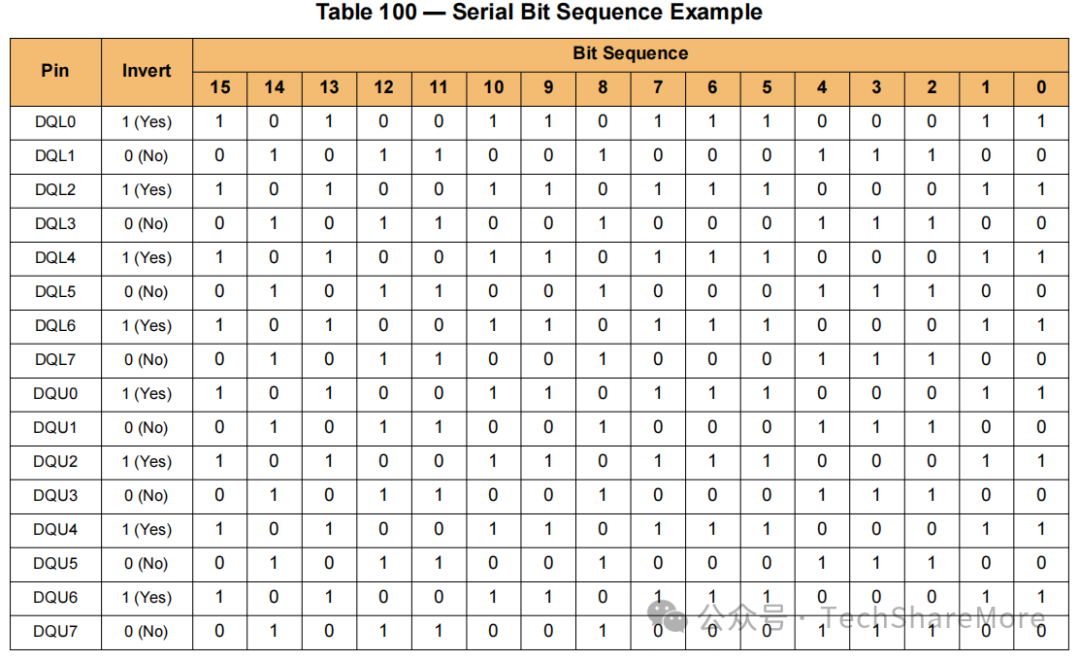

示例1:串行模式(Serial)

-编程配置:Read Training Pattern Format=0(Serial)、Read Pattern Data0=0x1C、Read Pattern Data1=0x59、Lower DQ Invert=0x55、Upper DQ Invert=0x55。

-输出特点:每个DQ通道按MR26/MR27的16位数据重复输出,奇数索引通道反转模式,偶数通道保持原模式,位序列呈现规律性交替。

Table 100 - Serial Bit Sequence Example(串行位序列示例表)

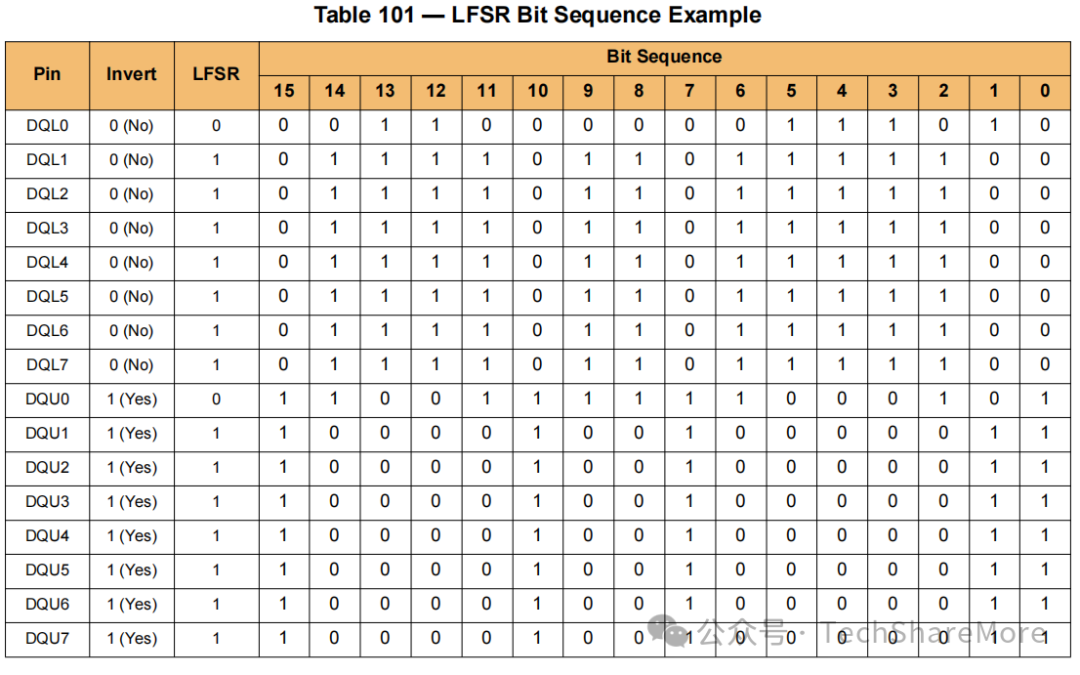

示例2:LFSR模式(默认选项)

-编程配置:Read Training Pattern Format=1(LFSR)、LFSR0/LFSR1 Pattern Option=0、Read Pattern Data0=0x5A、Read Pattern Data1=0x3C、LFSR Assignments=0xFE、Lower DQ Invert=0x00、Upper DQ Invert=0xFF。

-输出特点:DQL通道使用LFSR0输出,DQU通道使用LFSR1输出且反转,位序列无固定重复周期,适配高频串扰测试。

Table 101 - LFSR Bit Sequence Example(LFSR位序列示例表)

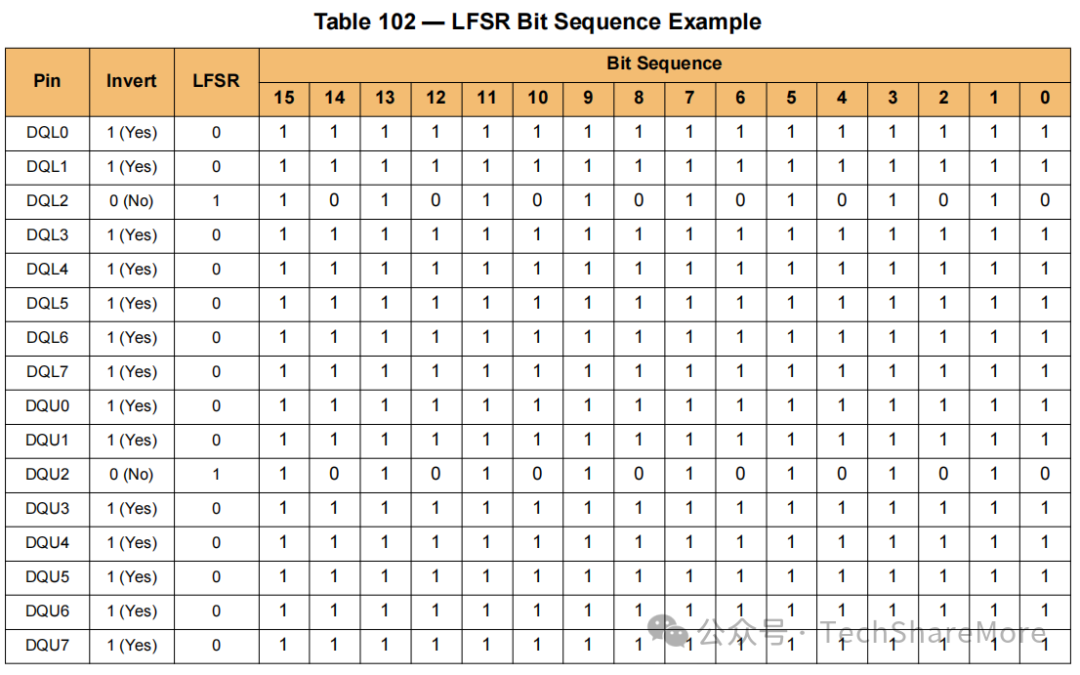

示例3:LFSR时钟模式

-编程配置:Read Training Pattern Format=1(LFSR)、LFSR1 Pattern Option=1(时钟模式)、Read Pattern Data0=0x00(恒定0)、LFSR Assignments=0x04、Lower/Upper DQ Invert=0xFB。

-输出特点:分配给LFSR1的DQ通道(如DQL2、DQU2)输出0/1交替时钟信号,其他通道输出恒定1(因LFSR0种子为0x00且反转)。

Table 102 - LFSR Bit Sequence Example(LFSR时钟模式位序列示例表)

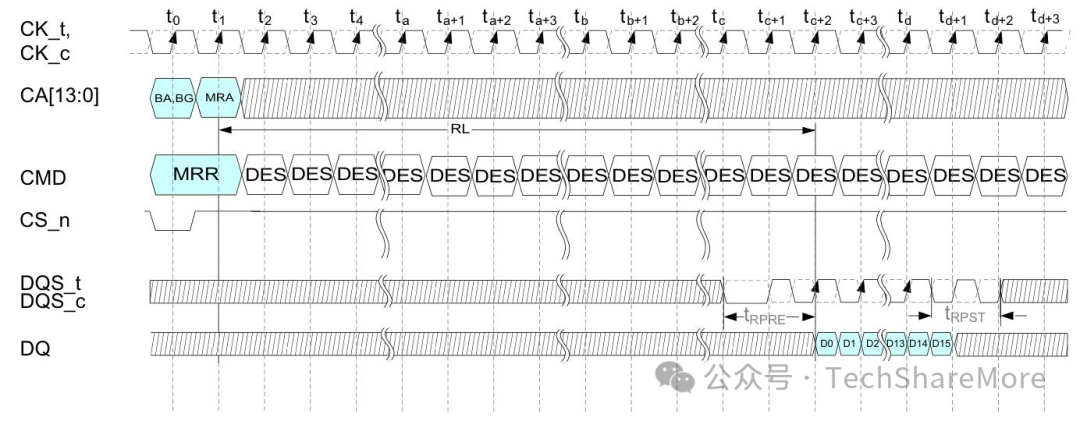

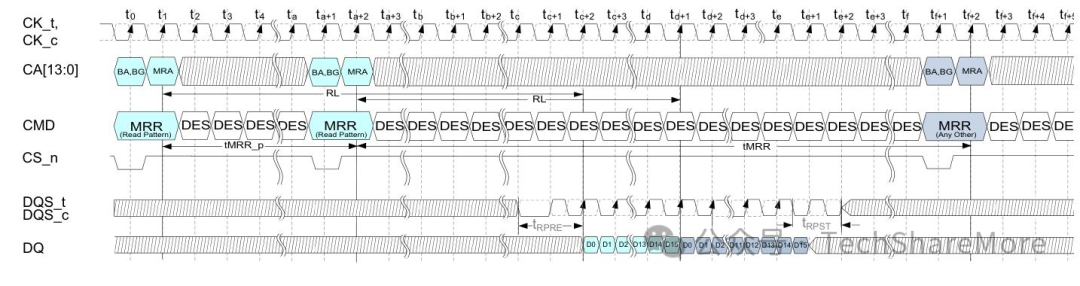

4.17.4 读训练模式时序图(Read Training Pattern Timing Diagrams)

时序部分定义了MRR触发模式输出、连续突发模式的时序关系,核心时序参数及约束如下:

1. 核心时序关系

-普通模式时序:MRR命令触发后,数据输出时序与普通读命令一致,BL固定为16,需遵循DDR5前导码时序要求。

-连续突发模式时序:进入后持续输出BL16重复模式,退出命令(MR25:OP[3]=0)后,DRAM在tCont_Exit内停止输出(可能截断当前突发),需等待tCont_Exit_Delay后才能发送其他命令。

-背靠背模式:支持MRR命令每8tCK连续触发,输出背靠背BL16模式,间隔为tMRR_p(快于普通MRR间隔tMRR)。

2. 关键时序图引用

Figure 96 - Timing Diagram for Read Training Pattern(读训练模式基础时序图)

Figure 97 - Timing Diagram for Back to Back Read Training Patterns(背靠背读训练模式时序图)

Figure 98 - Timing Diagram for Continuous Burst Mode Read Training Patterns(连续突发模式读训练时序图)

3. 核心时序参数表

Table 103 - Timing Parameters for Read Training Patterns(读训练模式时序参数表)

|

参数名称 |

符号 |

最小值 |

最大值 |

单位 |

核心说明 |

|

连续突发退出到下一条命令延迟 |

tCont_Exit_Delay |

tCont_Exit + tMRD |

- |

- |

确保模式输出完全停止 |

|

连续突发退出到训练模式结束 |

tCont_Exit |

- |

RL + BL/2 + 10nCK |

- |

可能提前停止输出 |

|

两次退出连续突发MRW命令最大间隔 |

tCBME |

- |

CL - 10nCK |

- |

第二次MRW需在该间隔内发送 |

4.17章节关键备注汇总

1.CRC约束:使用读训练模式(尤其是连续突发模式)前,必须禁用读CRC,否则会导致模式输出异常。

2.寄存器恢复:自我刷新、掉电、退出连续突发模式后,MR26-MR30可能恢复默认值,需重新编程种子、反转和LFSR分配。

3.连续突发模式操作:进入后仅允许MR31地址的MRR和退出MRW命令,其他命令可能导致DQ行为异常,需复位恢复。

4.非目标rank ODT:连续突发模式下,非目标rank的RTT_PARK需与目标rank的RTT_NOM_RD一致(如需终止),退出后需恢复RTT_PARK为正常配置。

5.LFSR状态:仅LFSR模式(非时钟选项)下,MRR访问MR31才会更新LFSR状态,其他场景状态保持不变。

未经作者本人授权,禁止任何形式的转载、洗稿、商用,侵权必究。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)