AI 算力时代的先进封装 Underfill 填充胶可靠性与应力管理—峻茂针对芯片级封装的低 CTE、流动性导热解决方案

随着生成式 AI (Generative AI) 与超算中心 (HPC) 的爆发,NVIDIA H100/Blackwell、AMD MI300 及 Google TPU v5p 等顶级算力芯片正全面转向 CoWoS、EMIB、HBM 等 2.5D/3D 先进封装架构。这种高密度异构集成技术在大幅提升算力密度的同时,也制造了前所未有的 热机械应力 (Thermo-mechanical Stress

核心关键词:#Underfill底部填充胶 #先进封装 # HBM3E #应力消除 #低CTE #高TG # AI芯片散热 #半导体封装可靠性 #毛细流动 #导热Underfill封装胶

摘要 (Executive Summary)

随着生成式 AI (Generative AI) 与超算中心 (HPC) 的爆发,NVIDIA H100/Blackwell、AMD MI300 及 Google TPU v5p 等顶级算力芯片正全面转向 CoWoS、EMIB、HBM 等 2.5D/3D 先进封装架构。这种高密度异构集成技术在大幅提升算力密度的同时,也制造了前所未有的 热机械应力 (Thermo-mechanical Stress) 与 散热 (Thermal Dissipation) 挑战。底部填充胶 (Underfill) 作为连接芯粒 (Chiplet) 与硅中介层 (Interposer) 的关键结构材料,其技术门槛已从传统的“流动与填充”升级为“应力再分布”与“主动热传导”。本文结合 峻茂在 CTE 13 ppm 超低膨胀与 37 W/m·K 极限导热领域的最新突破,解析如何破解高算力芯片的封装可靠性难题。

一、行业背景:算力时代的封装技术变革

半导体技术正经历从“微缩”向“堆叠”的范式转移。封装形式已从传统的 BGA、CSP 演进至以 TSV (硅通孔)、Micro-bump (微凸块) 为核心的晶圆级封装 (WLP)。

- 算力军备竞赛: 无论是 NVIDIA 的 GPU 集群,还是 Google 的 TPU 矩阵,都在通过 TSMC CoWoS 或 Intel EMIB 技术,将 HBM3E 高带宽内存与逻辑计算单元集成在同一封装体内。这种 Chiplet (芯粒) 设计显著缩短了互连距离,提升了通信带宽。

- 工程挑战升级: 异构芯片间的热膨胀系数差异、微米级的凸点间距 (Pitch < 40μm) 以及数百瓦的功耗,使得传统的 Underfill 材料面临严峻考验。材料必须兼顾高流动性与高导热性,这在物理上本身是一对矛盾。

二、核心机理:Underfill 如何解决封装失效难题

硅芯片 (CTE ≈ 2.6 ppm/°C) 与有机基板 (CTE ≈ 15-20 ppm/°C) 乃至硅中介层之间存在复杂的 CTE 错配 (Mismatch)。在回流焊的剧烈温变或 AI 负载波动产生的热循环中,这种错配会转化为巨大的剪切应力,直接撕裂脆弱的 Low-k 介质层或焊点。

2.1 应力解耦与焊点保护 (Stress Management)

峻茂 Underfill 胶液利用毛细作用原理 (Capillary Flow) 渗透至封装底部,固化后形成高模量交联网络。

- 应力吸收: 固化后的填充胶通过机械耦合作用,将原本集中在焊点上的热应力分散到整个芯片表面,防止焊点因疲劳而分层或开裂 。

- 抗跌落冲击: 在移动设备中,Underfill 能有效吸收跌落产生的动态机械应力,显著增强手持设备的板级可靠性 。

2.2 极端环境下的屏障构建 (Protection)

封装体内部的微隙是湿气和离子迁移的通道。峻茂 Underfill 构建了 Zero-Void (零空洞) 的密封层,阻断水汽路径,防止在高偏压下发生电化学迁移 (ECM) 短路,这对先进制程节点的可靠性至关重要。

2.3 辅助热管理 (Thermal Enhancement)

对于高功率密度的高算力芯片或图像传感器,传统的“空气间隙”是热的不良导体。峻茂开发了具有导热功能的 Underfill,作为热传导介质辅助散热 。

三、峻茂Underfill 胶技术参数解析

针对不同制程需求,峻茂开发了多系列的环氧基填充材料,涵盖绝缘、导热、耐高温等特性 。

3.1 热膨胀系数 (CTE) 的精准调控

为了匹配硅晶圆,峻茂通过高填充量微纳米硅粉改性,将 Underfill 的 CTE 严格控制。

- 技术指标: 峻茂低 CTE 系列产品可实现 CTE < 30 ppm/°C 。这一指标对于大尺寸 Die 的封装至关重要,能最大程度降低翘曲 (Warpage) 风险。

3.2 玻璃化转变温度 (Tg) 与耐温性

- 技术指标: 峻茂高 Tg 系列产品的 Tg 点可 > 130°C 。这意味着在器件高温工作区间内,材料始终保持刚性状态,不会因软化而失去对焊点的支撑保护力。

3.3 导热性能 (Thermal Conductivity)

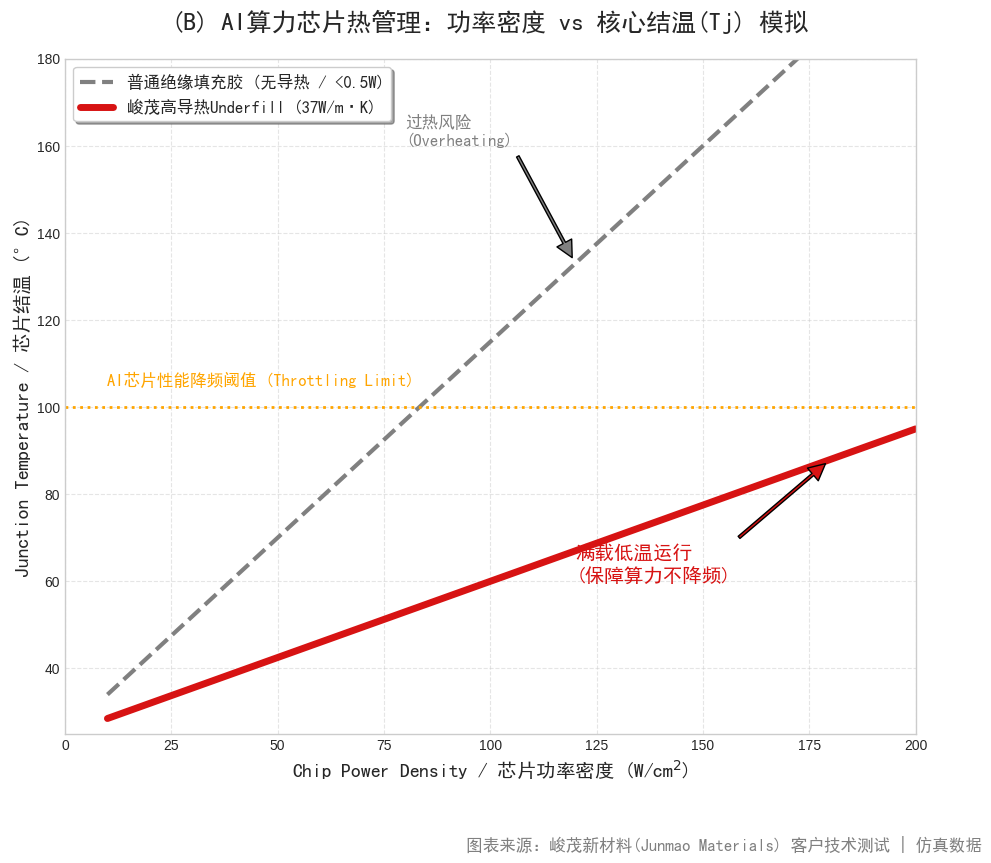

- 技术指标: 针对特定散热需求(如超高算力芯片),峻茂推出了导热系数高达 37 W/m·K 的低粘度可流动 Underfill 。这在保持优异流动性的前提下,实现了热学性能的跨越式提升。

3.4 “不可能三角”级的难度

在常规认知中,提高导热系数需要添加大量陶瓷填料,这往往会导致胶水粘度剧增、CTE 升高且变脆,粘度升高对Underfill工艺可操作性接近0,而且AI训练芯片的散热需求越来越高。

- CTE 13 ppm/°C:常规的Underfill胶偏低的CTE也有30+,但峻茂将其压低至 13,极其接近基板与芯片的综合膨胀率。这意味着在冷热冲击下,胶体与芯片“同呼吸、共膨胀”,界面应力极低。

- Tg 140°C: 玻璃化转变温度高达 140°C,确保在芯片满载运行(通常 90°C-110°C)时,材料始终处于刚性的玻璃态,提供稳定的机械支撑,不会软化塌陷。

- 剪切强度 32 MPa:尽管作为非结构专用胶,但该配方仍保持了 32 MPa 的超高粘接 强 度(常规产品仅 10-15 MPa)。这种“既要又要还要”的特性,使其成为大尺寸 AI 芯片封装的理想选择。

峻茂针对算力芯片的导热填充封装方案

四、应用场景与解决方案矩阵

峻茂不仅提供Underfill,还提供与之适配的低 CTE 导电银胶,形成完整的芯片封装材料解决方案 。

| 应用场景 | 关键挑战 | 峻茂推荐方案特性 |

| WLP (晶圆级封装) | 超低翘曲控制(Warpage) | 低 CTE (<30 ppm),高模量设计,低收缩率,防止晶圆应力变形 |

| CoWoS/HBM | 异构集成应力、微凸点保护 | 高 Tg (>130°C),匹配硅中介层,优异的耐冷热冲击性能 |

| AI Core/HPC/图像传感器 | 散热与填充并重,极端热流密度、热点消除 | 高导热 (37W),CTE 13 ppm,32 MPa 高强,兼顾散热与结构刚性 |

| 返修工艺 (Rework) | 昂贵芯片的回收 | 可返修系列,在特定温度下可去除,降低生产损耗 |

五、面向未来的封装材料愿景

从 Fan-Out (扇出型) 到 Hybrid Bonding (混合键合),乃至未来的 CPO (光电共封装) 技术,全球半导体封装正在经历一场深刻的架构重塑。未来的芯片将不再是单一的硅片,而是由无数芯粒通过 3D 互连构成的复杂系统。

在此趋势下,封装材料的性能边界将被不断推高。峻茂新材料 (SCITEO) 将持续在高导热 (50W+)、低 CTE (<20 ppm) 及 超低温固化 (50℃)领域投入研发。我们致力于追踪新一代 NVIDIA Blackwell 架构、硅光子互连及 6G 通信芯片等最新型技术,为半导体封装提供最坚实的材料保障,助力摩尔定律在三维空间延续。本文系峻茂新材料技术原创,未经授权不可转载。本文所含的技术测试模型图表可移步峻茂官网查阅。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)