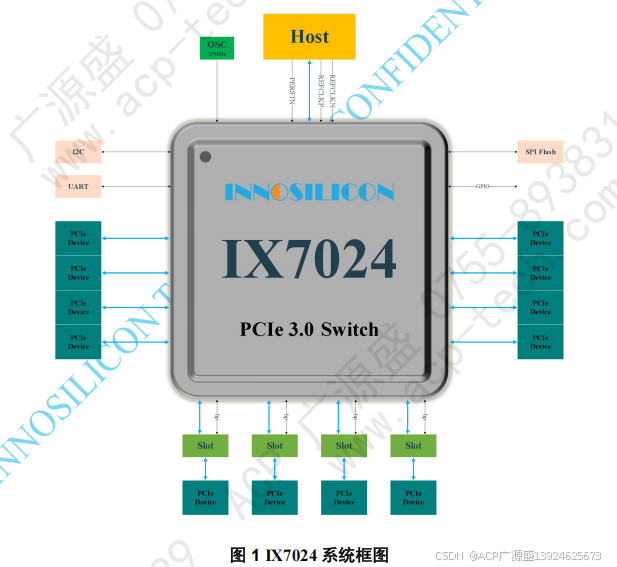

IX7024@ACP#7024 PCIe 3.0 交换芯片规格参数剖析及应用场景总结

本文详细解析了一款PCIe交换芯片的核心规格参数与应用场景。该芯片采用BGA封装,支持24条PCIe3.0通道,最大数据传输速率8Gb/s,具备多模式配置能力。功能特性包括支持多播、消息和点对点传输,提供多种电源管理方案,并配备丰富的外设接口。电气特性方面详细规定了I/O参数、时钟特性和信号阻抗要求。产品适用于服务器GPU扩展、存储系统、工业控制等多个领域,可满足AI训练、企业存储等高性能场景需求

·

一、核心规格参数剖析

(一)基础硬件参数

- 核心架构与端口配置

- 通道与端口:支持 24 条 8 GT/s 的 PCIe 3.0 通道,包含 1 个 x8 上游端口(USP)和最多 12 个下游端口(DSP),下游端口分为 Group 0(lane0~7)和 Group 1(lane8~15)两组,支持多模式配置(如 x8、x4、x2、x1 组合)。

- 端口传输能力:每条通道支持 2.5Gb(250MB/s)、5Gb(500MB/s)和 8Gb(1GB/s)传输速率,最大数据载荷 512Byte,最大读请求 4096Byte,支持通道倒序和极性反转。

- 封装与物理特性

- 封装规格:BGA 封装,尺寸 21mm×21mm,管脚间距 0.80mm,ball 总数 492 个,符合 JESD22-A114B(HBM)2000V 和 JESD22-C101D(CDM)250V ESD 标准。

- 温度范围:商业级 0~105℃(结温 Tj),工作壳温(Tc)0~70℃,无散热片时结温 - 环境热阻 14.9℃/W,结温 - 壳温热阻 0.93℃/W。

- 电源特性

- 供电电压:核心电源(VDD09)0.855~0.945V,PHY 电源(VCC18)1.71~1.89V,I/O 电源(VCC33)3.135~3.465V,电源动态纹波要求 VDD09 和 VCC33≤3%,VCC18≤2%。

- 功耗:Gen3 模式下,12 条活跃通道功耗 4.3W,24 条活跃通道功耗 7.1W。

(二)功能特性参数

- 交换与传输功能

- 核心交换:支持 USP 与 12 个 DSP 间数据交换,支持 Multicast、Message 和 P2P 端到端传输功能,下游端口上行仲裁支持固定轮询(RR)和加权轮询(WRR32/64/128),支持 Read Pacing 带宽管理。

- 电源管理:支持 L0s、L1-ASPM、L1 子状态(L1SS)和 PCI-PM 节能模式,未使用端口时钟可软件关闭以降低功耗。

- 时钟与复位

- 时钟输入:25MHz OSC 时钟(来自外部晶体或振荡器)、100MHz 差分时钟(来自 PCIe Host),I2C 接口时钟 SCL;时钟输出包括 SPI_SCK、12 对 PCIe Link 差时钟(DPE_CLK*),时钟逻辑类型为 HCSL。

- 复位机制:仅 1 个外部复位 PERSTN(来自上游设备),1 个输出复位 DPE_RSTN,触发条件包括 PERSTN、内部 POR 和全局软复位。

- 外设接口

- 主要接口:SPI Flash(支持 Standard SPI/QSPI 模式,SCLK 最高 100MHz,最大容量 16MB)、UART(支持 5/6/7/8bit 数据位,1/2bit 停止位,最高 5Mbps 波特率,64×8bit 发送 FIFO 和 64×12bit 接收 FIFO)。

- 扩展接口:I2C/SMBus Slave(支持 7bit 地址,兼容 SMBus v2.0)、I2C Master(支持 7/10bit 地址,100kbit/s 标准模式和 400kbit/s 快速模式)、32 个 GPIO(支持输入 / 输出 / 中断源,多配置模式)、热插拔(4 组信号,支持端口映射)。

- 启动与固件升级

- 启动模式:支持 BootROM(默认)和 BootFlash 两种启动模式,启动流程含寄存器配置、Flash 读取、SPL 加载等步骤。

- 固件升级:支持 5 种方式(烧录器、UART、MCU JTAG、I2C/SMBus、PCIe BAR)。

(三)电气与信号特性

- I/O 电气参数

- 输入输出电压:输入低电平(VIL)≤0.8V,输入高电平(VIH)≥2.0V,输出低电平(VOL)≤0.4V,输出高电平(VOH)≥2.4V,输入漏电流 ±10uA。

- 驱动能力:低电平输出电流(IOL)4.1~39.2mA,高电平输出电流(IOH)5.7~56.1mA(随配置值变化)。

- 时钟电气参数

- 100MHz 差分时钟:差分输入高电平≥150mV,低电平≤-150mV,交叉点电压 250~550mV,占空比 40%~60%,周期抖动≤150ps,上升 / 下降沿速率 0.6~4.0V/ns。

- 信号阻抗要求

- 差分信号:UPE_Tx/Rx、DPE_Tx/Rx 阻抗 85Ω±10%,UPE_CLK、DPE_CLK 阻抗 100Ω±10%。

- 单端信号:未定义阻抗统一为 50Ω±10%,SPI Flash 相关信号(SPI_SCK/SDIO/CS)阻抗 50Ω±10%。

二、产品应用场景总结

(一)核心应用领域

- 服务器与计算加速

- GPU 扩展:支持连接 2 个 PCIe Gen3 x8 或 4 个 PCIe Gen3 x4 GPU 加速卡,适用于 AI 训练、高性能计算(HPC)等场景,满足多 GPU 协同计算的高速数据传输需求。

- 多设备集成:可同时连接 GPU、NIC(网络接口卡)、NVMe SSD,构建服务器内部高速 IO 扩展架构,适用于云计算、数据中心等对多设备协同访问要求较高的场景。

- 存储系统

- NVMe SSD 扩展:支持连接 4~12 个 PCIe Gen3 x4 NVMe SSD,可根据带宽和端口数量需求灵活配置,适用于企业级存储阵列、分布式存储节点等场景,提供高并发存储访问能力。

- 工业与嵌入式系统

- 高速 IO 扩展:通过 Fanout 模式连接最多 12 个不同类型和速率的 PCIe 端点设备(如采集卡、接口卡等),适用于工业控制、安防网络、通信平台等需要多设备扩展的场景。

- 汽车电子:符合工业级可靠性要求,可用于电动汽车的车载计算平台、自动驾驶感知模块等高速设备互联场景。

(二)典型应用场景细分

| 应用场景 | 配置方式 | 核心优势 |

|---|---|---|

| AI 训练服务器 | 1 个 USP(x8)+4 个 DSP(x4 GPU) | 支持多 GPU 端到端传输,低延时、高带宽,满足 AI 模型并行训练需求 |

| 企业级存储阵列 | 1 个 USP(x8)+8 个 DSP(x2 NVMe SSD) | 支持 12 个 NVMe 设备扩展,高并发 IO,适配存储密集型业务 |

| 工业控制平台 | 1 个 USP(x4)+6 个 DSP(x1/x2 工业接口卡) | 多端口灵活配置,支持热插拔,适配工业场景设备动态接入 |

| 车载计算系统 | 1 个 USP(x8)+3 个 DSP(x4 GPU+ x2 NIC+ x2 存储) | 低功耗、高可靠性,满足车载环境多设备协同需求 |

| 数据中心边缘节点 | 1 个 USP(x8)+12 个 DSP(混合接口设备) | Fanout 模式适配多类型设备,简化边缘节点硬件架构 |

三、应用关键注意事项

- 硬件设计:需遵循 PCB 叠层阻抗要求(推荐 8 层 / 10 层通孔板),高速信号(PCIe、时钟)需参考完整地平面,避免跨分割;电源过孔数量需满足通流和瞬态电流需求(VDD09≥15 个,VCC18≥7 个,VCC33≥4 个)。

- 兼容性:支持与主流 SPI Flash 器件兼容(如 AMIC A25L512、GigaDevice GD25Q512、Winbond W25X05CL 等),I2C/SMBus 接口支持地址配置和 ARP 功能。

- 可靠性:工作温度需严格控制在 0~105℃(结温),避免长期超温运行;热插拔操作需遵循规范上电 / 下电时序,防止设备损坏。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)