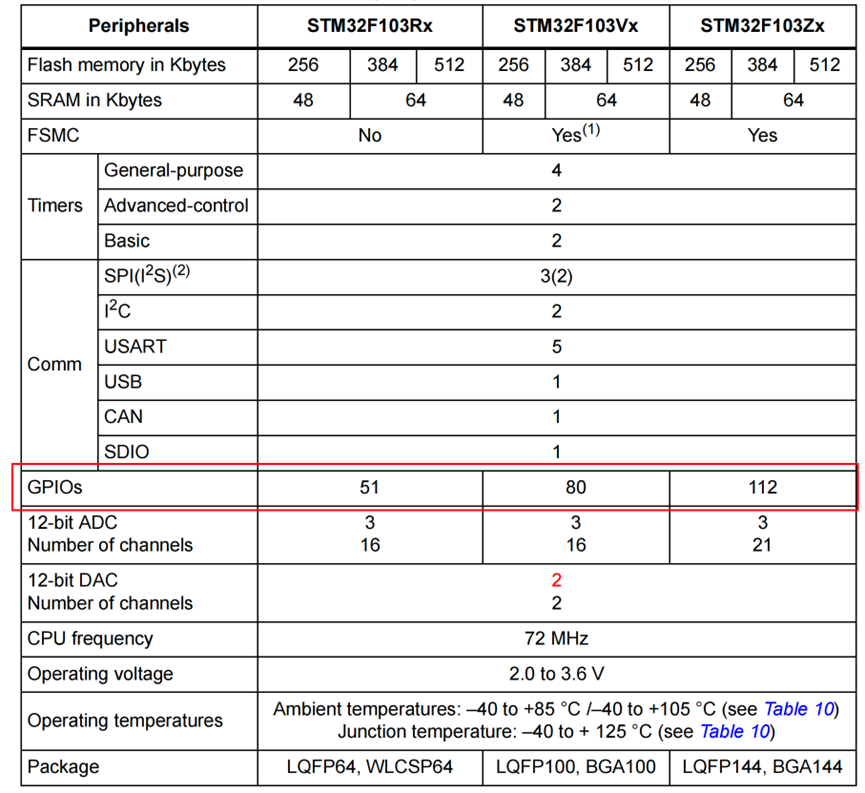

STM32F103ZET6学习笔记

简单理解就是我们可以控制输入输出的STM32引脚,统称为GPIO。(7)推挽式复用功能(Alternate function push-pull)(8)开漏复用功能(Alternate function open-drain)(5)通用开漏输出(Output open-drain)(6)通用推挽式输出(Output push-pull)(3)输入下拉(Input-pull-down)(1)输入浮空

目录

GPIO外设

GPIO(General-purpose input/output),通用型输入输出。简单理解就是我们可以控制输入输出的STM32引脚,统称为GPIO。

GPIO的8种工作模式

GPIO端口的每个位(引脚)可以由软件分别配置成8种模式,当然对同一个引脚同一时间只能处于某一种模式中。

(1)输入浮空(Input floating)

(2)输入上拉(Input pull-up)

(3)输入下拉(Input-pull-down)

(4)模拟输入(Analog)

(5)通用开漏输出(Output open-drain)

(6)通用推挽式输出(Output push-pull)

(7)推挽式复用功能(Alternate function push-pull)

(8)开漏复用功能(Alternate function open-drain)

I/O端口寄存器必须按32位字被访问

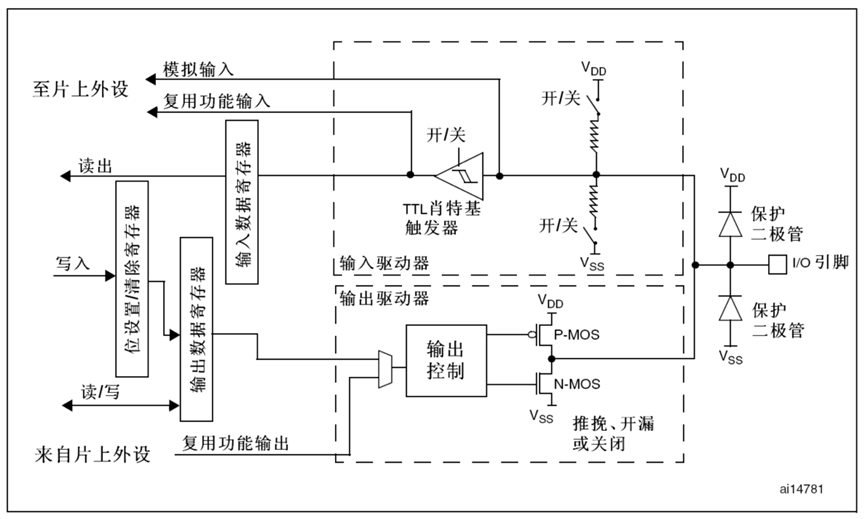

输出模式

推挽输出 :

1.向设置/清除寄存器对应的设置位或清除位写1

2.或者直接输出寄存器对应位写1或0

3.也可以从输入寄存器读取引脚状态:

4.工作时两个MOS管交替工作来驱动负载。输出1时,上部晶体管导通将电流推向负载;输出0时,下部晶体管导通,将电流拉回地线。所以叫推挽输出。

开漏输出:

1.上部晶体管永远关闭。

2.可以输出0

3.如果要输出1必须接上拉电阻

推挽输出和开漏输出的选择

使用推挽

1.驱动能力需求较高的场合

2.高速信号传输

3.无需共用信号线的场合

使用开漏

1.多个设备共用信号线

2.不同电压系统之间的接口

3.需要外部上拉电阻来确定逻辑高电平的场合

复用输出模式

从片上外设来

(1)在开漏或推挽式配置中,输出缓冲器被打开

(2)内置外设的信号驱动输出缓冲器(复用功能输出)。

(3)施密特触发输入被激活。

(4)弱上拉和下拉电阻被禁止。

(5)在每个APB2时钟周期,出现在I/O脚上的数据被采样到输入数据寄存器。

(6)开漏模式时,读输入数据寄存器时可得到I/O口状态。

(7)在推挽模式时,读输出数据寄存器时可得到最后一次写的值。

输入模式

2个保护二极管的作用是保护我们的芯片不会由于电压过高或过低而烧毁

施密特(图中翻译成肖特基触发器应该是翻译错误,英文版手册是TTL Schmitt trigger)触发器是包含正反馈的比较器电路。可以对信号进行波形整形。

上拉输入,下拉输入,浮空输入

2个开关控制引脚在没有输入的时候是上拉,下拉还是浮空。当上面的开关闭合的时候,输入被拉高到高电平。当下面的开关闭合的时候,输入被拉低到低电平。如果两个都不闭合,输入就是悬空状态。两个同时闭合,就是费电了,不会这么做的

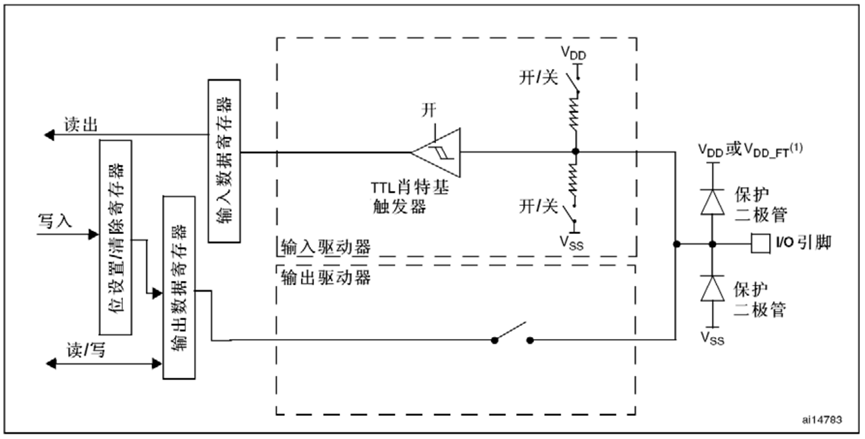

模拟输入

当配置为模拟输入时:

(1)输出部分被禁止。

(2)禁止施密特触发输入,实现了每个模拟I/O引脚上的零消耗。施密特触发输出值被强置为0。

(3)弱上拉和下拉电阻被禁止。

(4)读取输入数据寄存器时数值永远为0。

与GPIO相关的7个寄存器(重要)

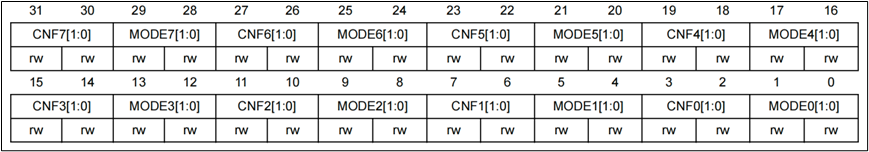

GPIOx_CRL(端口配置低寄存器)

MODE:

00:输入模式(复位后的状态) 01:输出模式,最大速度10MHz

10:输出模式,最大速度2MHz 11:输出模式,最大速度50MHz

CNF:

(1)当MODE是00 (输入模式) 00:模拟输入模式

01:浮空输入模式(复位后的状态) 10:上拉/下拉输入模式 11:保留

(2)当MODE>00(输出模式)

00:通用推挽输出模式 01:通用开漏输出模式

10:复用功能推挽输出模式 11:复用功能开漏输出模式

GPIOx_CRH(端口配置高寄存器)

该寄存器配置的是每个端口的 8-15引脚,配置方式和低位寄存器完全一样

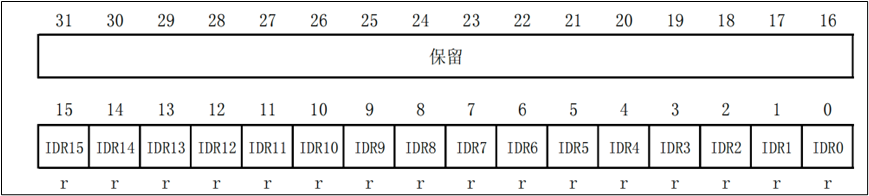

GPIOx_IDR(端口输入数据寄存器)

IDRy[15:0]:

这些位为只读并只能以字(16位)的形式读出。读出的值为对应I/O口的状态。

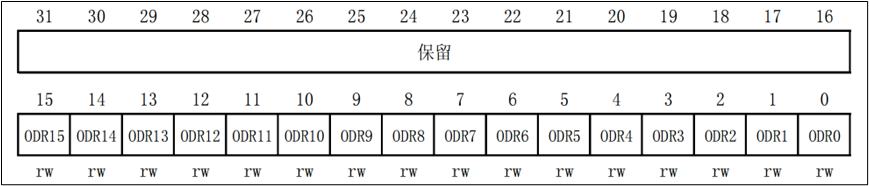

GPIOx_ODR(端口输出数据寄存器)

保留位始终读为0。剩下的分别对应每个引脚的输出值。

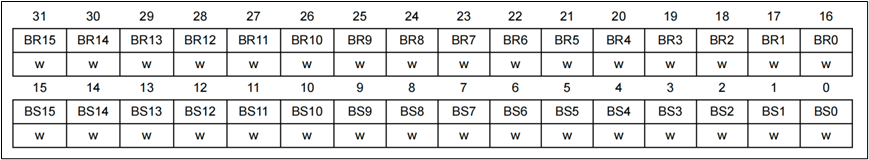

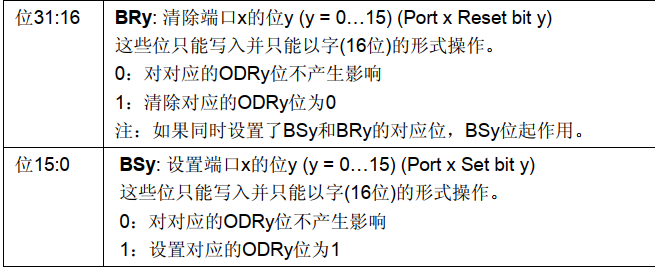

GPIOx_BSRR(端口位设置/清除寄存器)

(1)高16位是用清除对应的数据输出寄存器的位(0-15)的值:设置为0不影响,设置为1会清除ODR对应的位的值(置为0)。

(2)低16位是用设置对应的数据输出寄存器的位(0-15)的值:设置为0不影响,设置为1会设置ODR对应的位的值(置为1)。

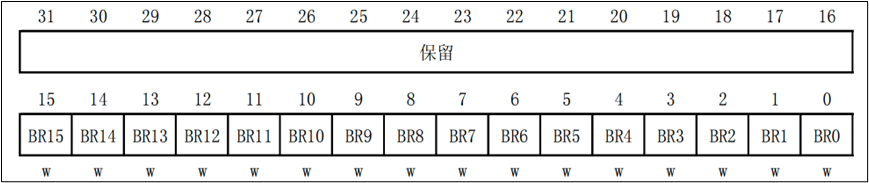

GPIOx_BRR(端口位清除寄存器)

这个寄存器具有了GPIOx_BSRR一半的功能:清除。

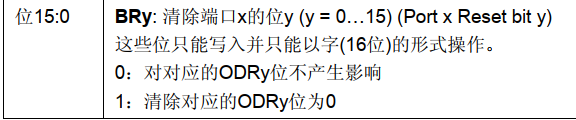

GPIOx_LCKR(端口配置锁定寄存器)

对0-15位:0:不锁定对应端口的配置。1:锁定对应端口的配置

第16位用来激活锁定寄存器,必须按照规定的时序来操作才行: 写1 -> 写0 -> 写1 -> 读0 -> 读1

- 该序列是硬件设计的保护机制,防止误写而锁定引脚配置。只有按规定的读写次序才能真正把 LCKK 置为“已锁定”状态。

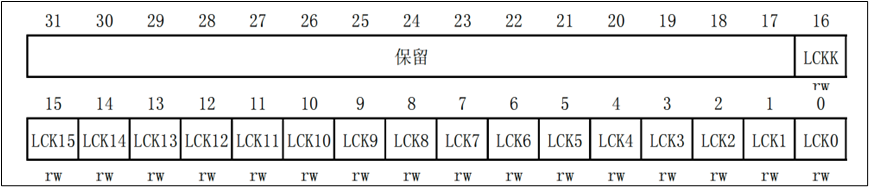

系统架构

三个被动单元

内部SRAM

存储程序执行时用到的变量

内部闪存存储器

存储下载的程序。程序执行时用到的常量

AHB到APB的桥(AHB to APBx)

桥1,通过APB2总线连接到APB2上的外设。高速外设,最高72MHz。

桥2,通过APB1总线连接APB1上的外设。低速外设,最高36MHz。

四个驱动(主动)单元

CortexTM-M3内核DCode总线(D-bus)

通过外部的DCode总线连接到总线矩阵然后与闪存存储器的数据接口相连接,实现从Flash常量加载和调试访问

内核系统总线(S-bus)

通过外部的System总线连接到总线矩阵

通用DMA1(Direct Memory Access)

通用DMA2

通过DMA总线,连接到总线矩阵。作用就是降低CPU负担,不通过CPU实现内存和外设之间的数据传输

其他单元

内核ICode总线

通过外部的ICode总线连接Flash,实现指令的读取

FSMC(Flexible Static Memory Controller)

用来扩展外部SRAM,Flash,连接LCD屏幕等

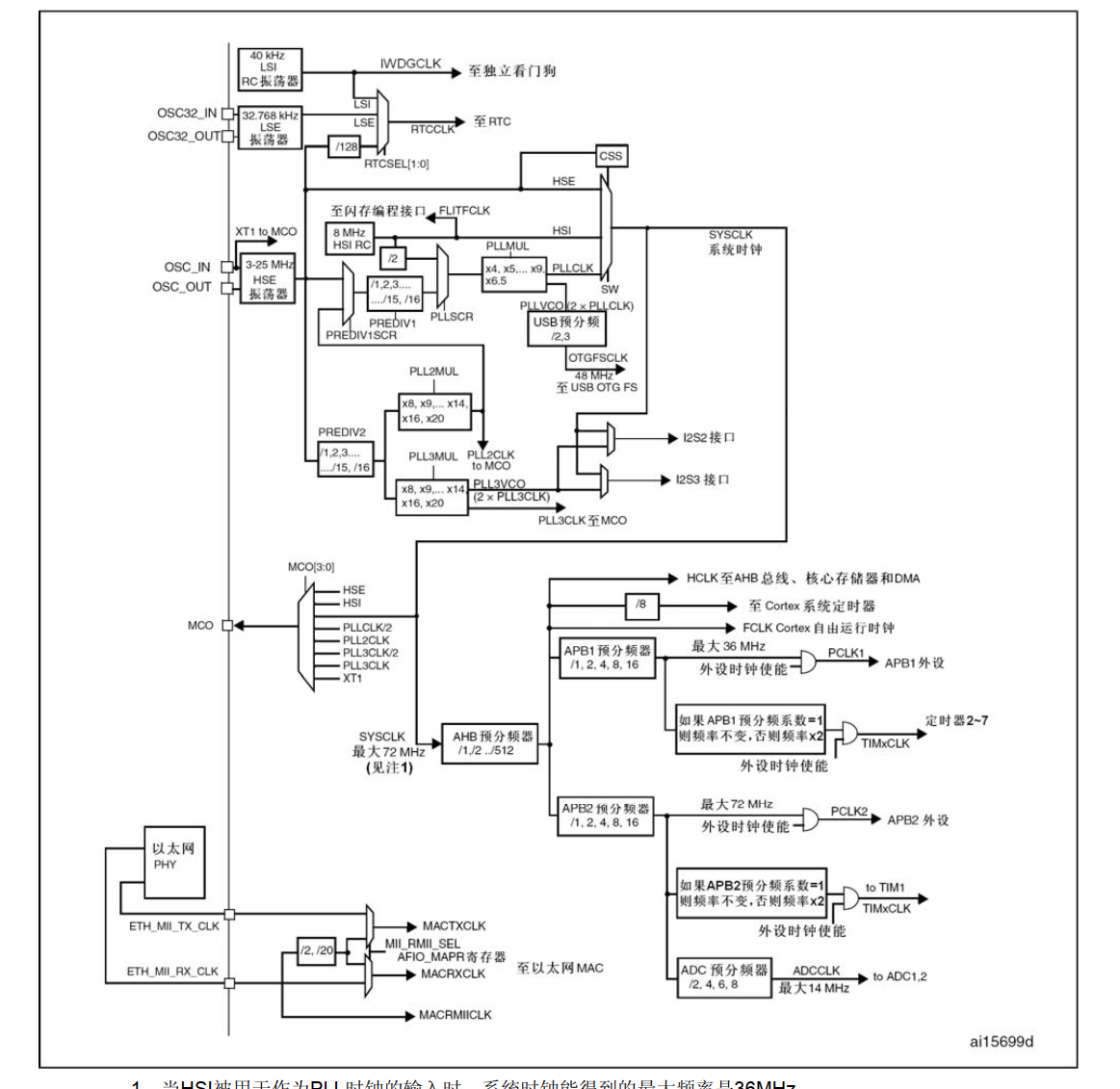

时钟系统

时钟树

在STM32中有3种不同的时钟源用来驱动系统时钟(SYSCLK):

(1)HSI振荡器时钟(High Speed Internal oscillator,高速内部时钟)

(2)HSE振荡器时钟(High Speed External(Oscillator / Clock),高速外部时钟)

(3)PLL时钟(Phase Locked Loop 锁相环/倍频器)

还有2种2级时钟:

(4)LSI时钟(Low Speed Internal,低速内部时钟)

(5)LSE时钟(Low Speed External oscillator,低速外部时钟)。

节能!高速设备接高速时钟,低速设备接低速时钟,可以最大程度的达到节能效果

STM32F103ZET6中断系统

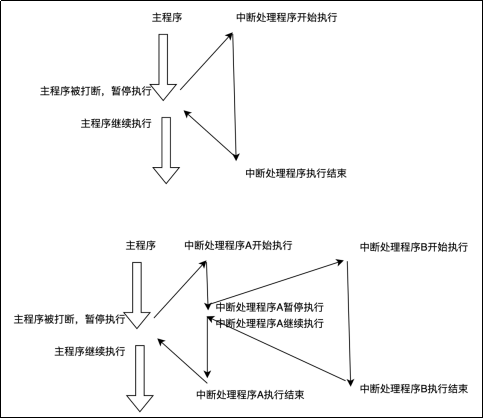

在主程序运行过程中,出现了特定事件,使得CPU暂停当前正在运行的程序,转而去处理这个事件,等这个事件处理完成之后,CPU再回到刚才被打断的位置继续处理,这就是中断。

那个打断CPU执行的特定事件,我们一般称之为中断源。被中断源打断的位置我们称为断点。处理特定事件的过程,我们称为执行中断处理程序。

正在执行中断程序的时候,这个时候有可能被另外一个中断源给中断,CPU转而去执行另外一个中断源的中断处理程序,这叫中断嵌套。

中断源可以是外部的,也可以是内部的。外部的叫外部中断源,内部的叫内部中断源(内部的中断有时候也叫异常)。

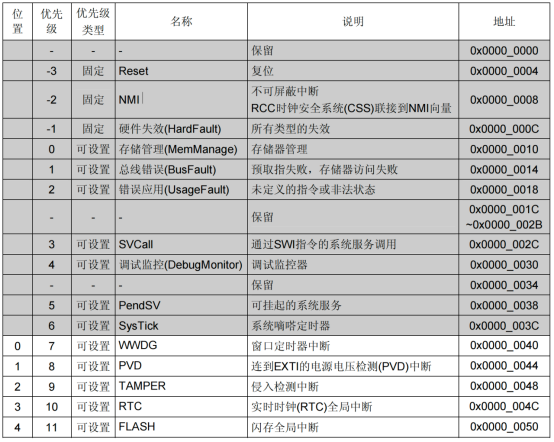

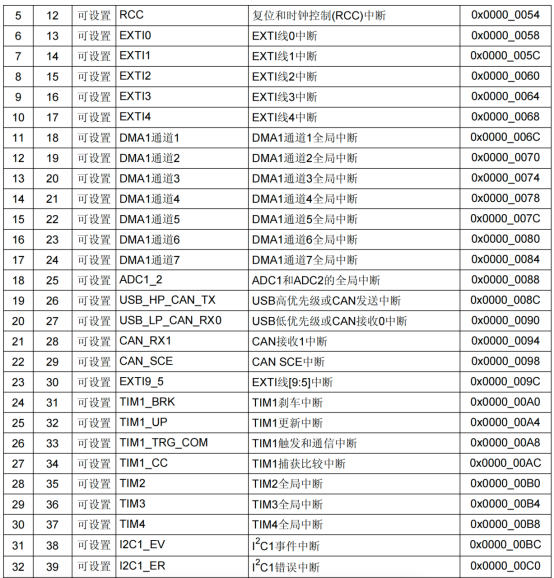

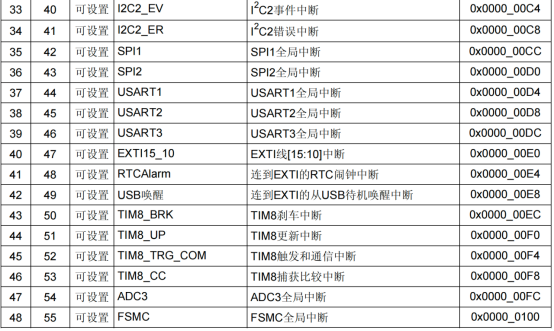

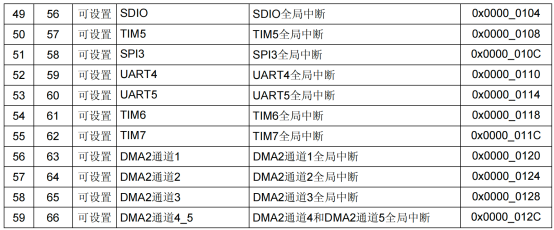

Cortex-M3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

STM32有84个中断,包括16个内核中断和68个可屏蔽中断,具有16级可编程的中断优先级。

STM32F103系列70个中断有10个内核中断和60个可编程的外部中断。

灰色背景的是内部中断(或者异常),其他的为外部中断

NVIC嵌套向量中断控制器

NVIC(Nested vectored interrupt controller嵌套向量中断控制器)和处理器核的接口紧密相连,可以实现低延迟的中断处理和高效地处理中断。嵌套向量中断控制器管理着包括内核异常,外部中断等所有中断。由NVIC决定哪个中断的处理程序交给CPU来执行。

16个IO的中断与PVD(电源电压检测),RTC(实时时钟),USB,以太网检测这20个外部中断会通过EXTI来控制,然后交给NVIC。其他中断都是直接交给NVIC来处理。

NVIC用4个位来控制优先级,值小的优先级高。把优先级分为两种:抢占优先级和响应优先级。

优先级值越小,优先级越高。如果不设置优先级,则默认优先级为0。先比较抢占优先级。抢占优先级高的可以打断抢占优先级低的。若抢占优先级一样,再比较响应优先级。但是响应优先级不会导致中断嵌套。若抢占优先级一样的同时挂起,则优先处理响应抢占优先级高的。若挂起的优先级(抢占和响应)都一样,则查找中断向量表,值小的先响应。

外部中断控制器

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)