推挽电路内部结构详解

本文系统分析了推挽电路的结构与工作原理。推挽电路由PMOS和NMOS管组成,分别作为上拉和下拉开关,实现非门功能。其核心特点是两管交替导通,无静态功耗,具有rail-to-rail输出能力。文章详细阐述了MOS管的导通条件,并通过高低电平输入时的电流路径解释了"推"(提供电流)和"挽"(吸收电流)的物理含义。对比开漏输出结构,推挽电路具有更强的驱动能力和更快

·

1. 推挽电路概述与背景

- 推挽电路(Push-Pull Circuit),其在数字电路、电源驱动、IO 口设计等场景中常见。

- 实际芯片中,二输入 NAND/NOR 等基础逻辑门常采用 5-pin 封装:VCC、GND、2×Input、1×Output。

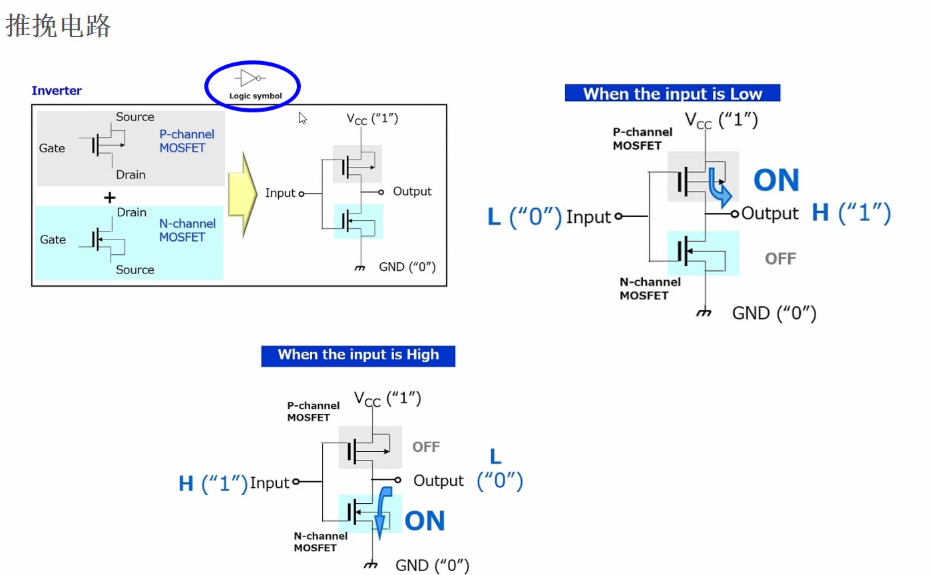

2. CMOS 反相器(推挽结构)的内部构成

- 核心结构:由一个 PMOS 与一个 NMOS 管组成,二者 源极(Source)分别接 VCC 和 GND,漏极(Drain)相连作为输出端,栅极(Gate)并联作为输入端。

- 此结构即为 互补 MOS(CMOS)反相器,也是最基础的推挽输出单元。

- 该结构无静态功耗(理想情况下),开关速度快,抗干扰能力强,是现代数字 IC 的基石。

3. MOSFET 导通/截止条件详解

MOSFET 是电压控制型器件,其导通取决于栅源电压 VGS与阈值电压 VTH 的关系:

NMOS:

- 导通条件:VGS>VTN(VTN>0,典型值 0.4~1.2 V)

- 截止条件:VGS<VTN

PMOS:

- 导通条件:VGS<VTP(VTP<0,典型值 -0.4 ~ -1.2 V)

- 等价表述:∣VGS∣>∣VTP∣ 且 VGS<0

- 截止条件:VGS>VTP即 VGS大于负阈值,如 VGS=−0.2 V 而 VTP=−1.0 V,则不导通)

4. 推挽电路工作原理:输入为低电平(逻辑 0)

- 输入 VIN=0(接地)

- 对 PMOS:VGS=VG−VS=0−VCC=−VCC

- 因 −VCC<VTP(如 VCC=3.3 V,VTP=−1.0 V),满足导通条件 → PMOS 导通

- 对 NMOS:VGS=0−0=0<VTNVGS=0−0=0<VTN → NMOS 截止

- 输出端通过导通的 PMOS 连接到 VCC → 输出为高电平(逻辑 1)

5. 推挽电路工作原理:输入为高电平(逻辑 1)

- 输入 VIN=VCC

- 对 PMOS:VGS=VCC−VCC=0>VTP(因 VTP<0)→ PMOS 截止

- 对 NMOS:VGS=VCC−0=VCC>VTN→ NMOS 导通

- 输出端通过导通的 NMOS 连接到 GND → 输出为低电平(逻辑 0)

结论:该电路实现 非门(Inverter)功能:Y=X‾

6. “推”与“挽”(拉)的物理含义:电流方向分析

名称来源源于输出级对负载的驱动方式:

“推”(Push):

- 当上管(PMOS)导通、输出为高时,电流从 芯片内部(VCC)→ 输出端 → 负载 → 地

- 电流由芯片“推出”至外部负载 → 称为 ** sourcing current(拉电流 / 提供电流)**

注:术语易混。“拉电流”(sourcing current)指芯片向外提供电流;“灌电流”(sinking current)指芯片吸收电流。视频中将“推出”称为“推”,符合工程习惯。

“挽”(Pull,或 Pull-down):

- 当下管(NMOS)导通、输出为低时,电流从 负载 → 输出端 → 芯片内部(GND)

- 电流被芯片“拉入”内部 → 称为 ** sinking current(灌电流)**

关键点:推挽结构可同时提供拉电流与灌电流能力,驱动能力强,输出阻抗低,适用于高速、大电流场景。

7. 推挽电路结构总结与设计要点

- 基本结构:

- 上管:PMOS,Source 接 VCC,Drain 接 Output

- 下管:NMOS,Source 接 GND,Drain 接 Output

- Gate 并联接 Input

- 关键特性:

- 无静态功耗(两管永不同时导通,理想情况下)

- 输出摆幅接近 rail-to-rail(0 ~ VCC)

- 高驱动能力(可直接驱动 LED、小电机等)

- 设计注意:

- 需避免输入电平处于阈值附近导致两管部分导通 → 产生直通电流(shoot-through current),造成功耗与发热

- 实际中常加入死区时间(dead time)控制或使用施密特触发输入改善噪声容限

8. 对比:开漏输出(Open-Drain)结构

- 结构差异:仅保留 NMOS(或 PMOS),去掉上管(PMOS),输出端需外接 上拉电阻 到 VCC。

- 工作特点:

- 输出高电平时:NMOS 截止,靠上拉电阻将 Output 拉至 VCC

- 输出低电平时:NMOS 导通,Output 接地

- 优势:

- 支持电平转换(如 3.3V MCU 驱动 5V 总线)

- 多设备线与(Wire-AND),用于 I²C、1-Wire 等总线

- 劣势:

- 上升沿速度受上拉电阻与负载电容限制(RC 时间常数)

- 无法主动“推”高电平,驱动能力弱于推挽

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)