DDR5 vs DDR4 SI / PI 难点,一次对比看清楚

DDR5 的难点,不是“它太快”,而是“它不再容忍单点优秀”。线画得好其他凑合SI、PI、Training,缺一个,系统就不陪你玩。

·

⚔️ DDR5 vs DDR4

SI / PI 难点,一次对比看清楚

一句话先给结论:

DDR4 的难,是“线怎么画”;

DDR5 的难,是“系统怎么一起活”。DDR5 不只是更快,它是把 SI + PI + Training 全部绑在一起的一次升级。

🎯 一张总览图:DDR4 vs DDR5 的“战场变化”

先别看细节,你要先建立一个直觉👇

| 维度 | DDR4 | DDR5 |

|---|---|---|

| 设计关注点 | SI 为主 | SI + PI + Training |

| 数据结构 | 单 64bit 通道 | 双 32bit 子通道 |

| 供电 | 主板集中 | DIMM 上 PMIC |

| 容错方式 | 频率留裕量 | 靠训练兜底 |

| 工程感受 | “线对就行” | “系统级调参” |

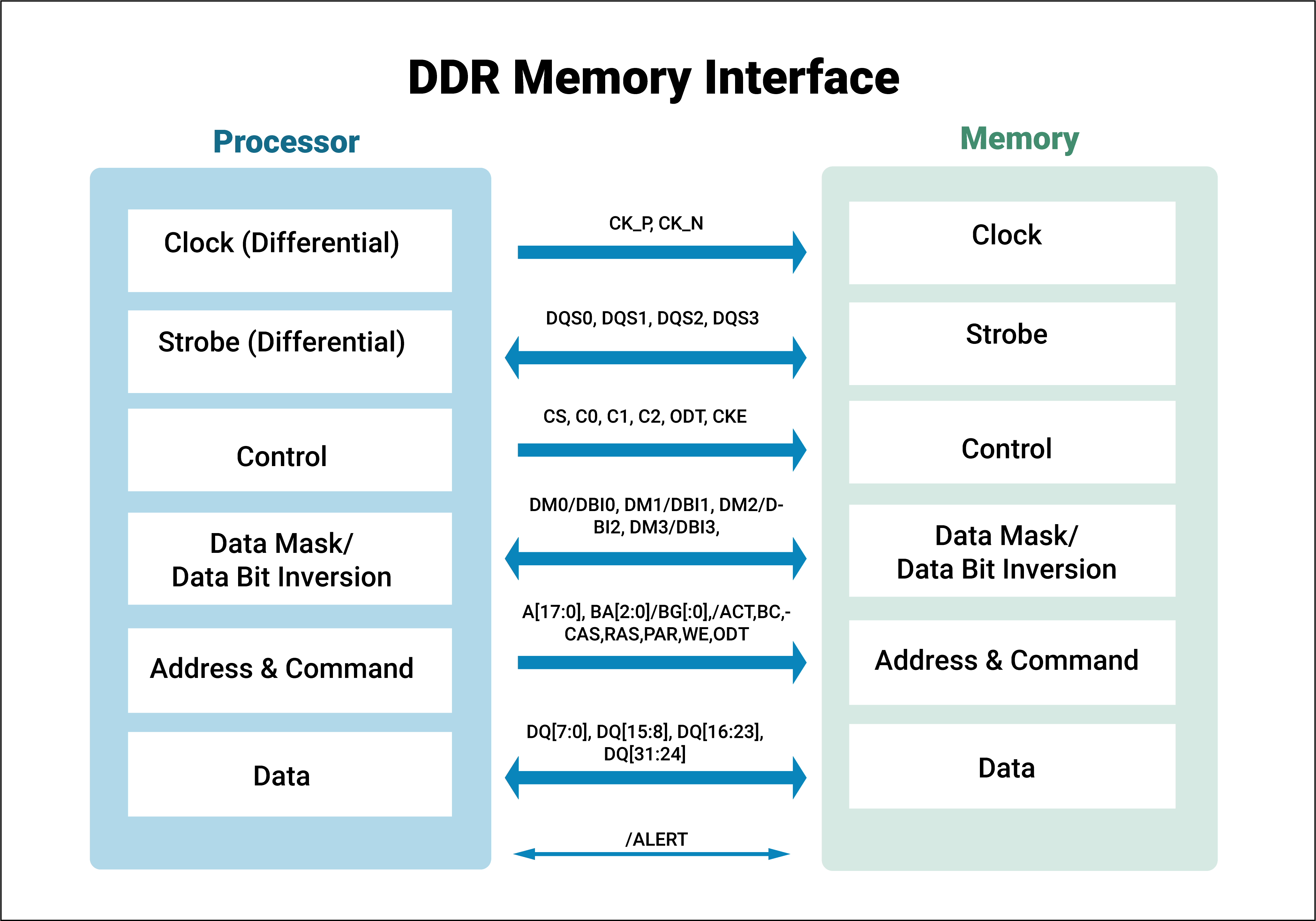

🧠 二、SI 难点对比:

DDR5 不是“更难画线”,而是“更容易踩极限”

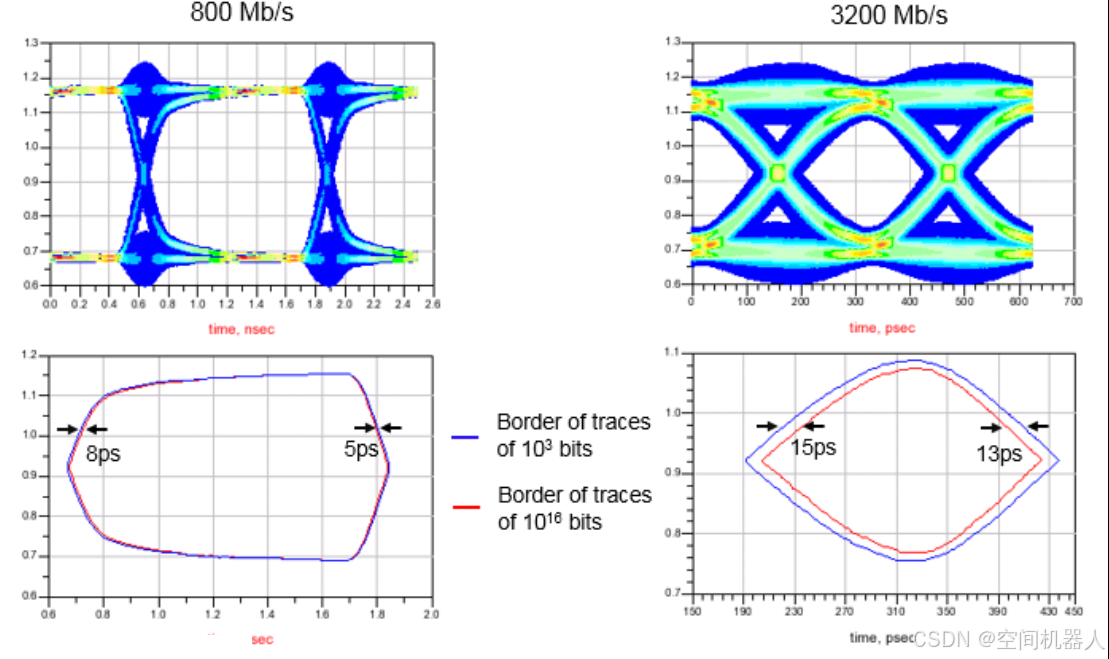

1️⃣ 频率一上来,SI 的“容错空间直接蒸发”

- DDR4 主流:

👉 2400 / 3200 MT/s - DDR5 起步:

👉 4800 MT/s 往上

📌 工程师真实感受:

DDR4 还能靠“经验 + 保守”;

DDR5 是“你有多精确,它给你多少眼图”。

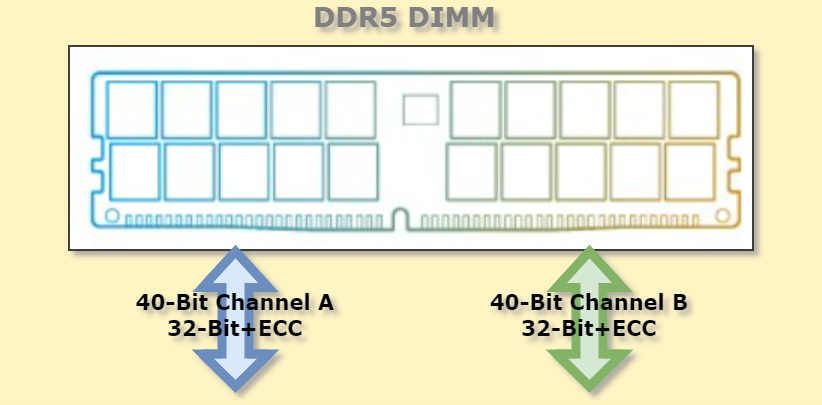

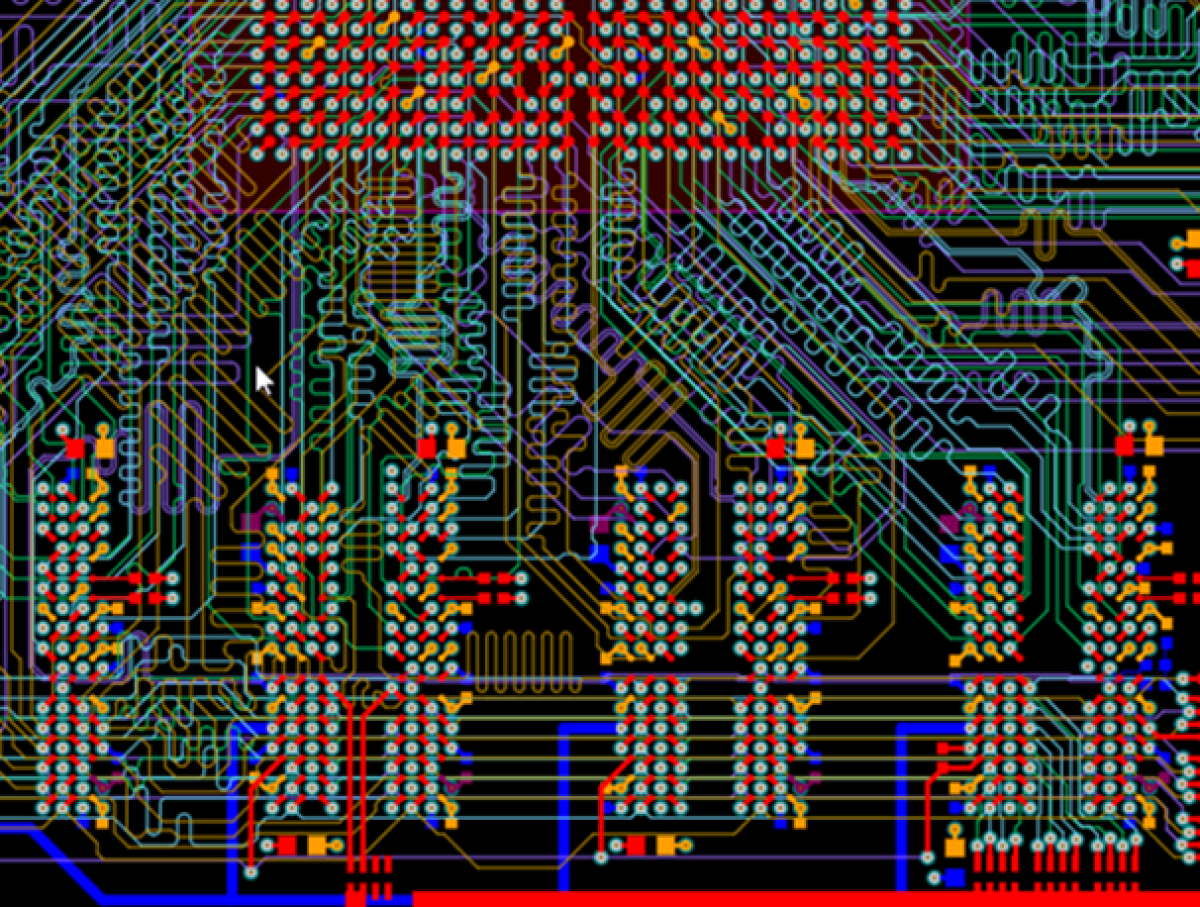

2️⃣ DDR5 的“子通道”是把双刃剑

-

好处:

- 单通道线更少

- Stub 影响相对降低

-

代价:

- 时序窗口更碎

- 任一子通道不稳 → Training 失败

👉 DDR4 是“一条线翻车”,

👉 DDR5 是“其中一条子通道翻车,整体降级”。

3️⃣ 反射不一定更大,但“踩采样点”的概率更高

在 DDR4:

- 反射只要不太夸张

- 还能靠 margin 扛

在 DDR5:

- UI 更短

- 反射更容易压到采样点

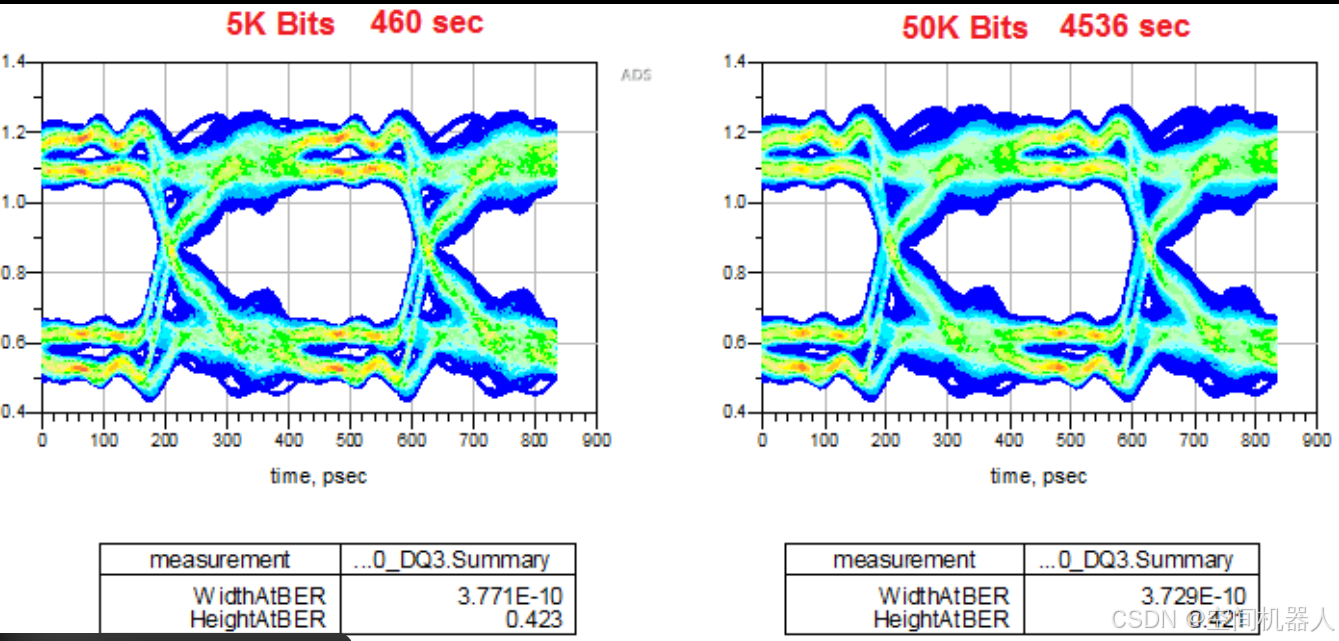

📌 你会看到这种现象👇

示波器看着“还行”,

Training 日志却疯狂报错。

⚡ 三、PI 难点对比:

DDR5 把“地狱”从主板,挪到了 DIMM

1️⃣ DDR4 的 PI 难点在哪里?

- VDD / VDDQ 来自主板

- 路径长

- 噪声和压降全在板级解决

📌 你要解决的是:

- PDN 阻抗

- 去耦

- 回流路径

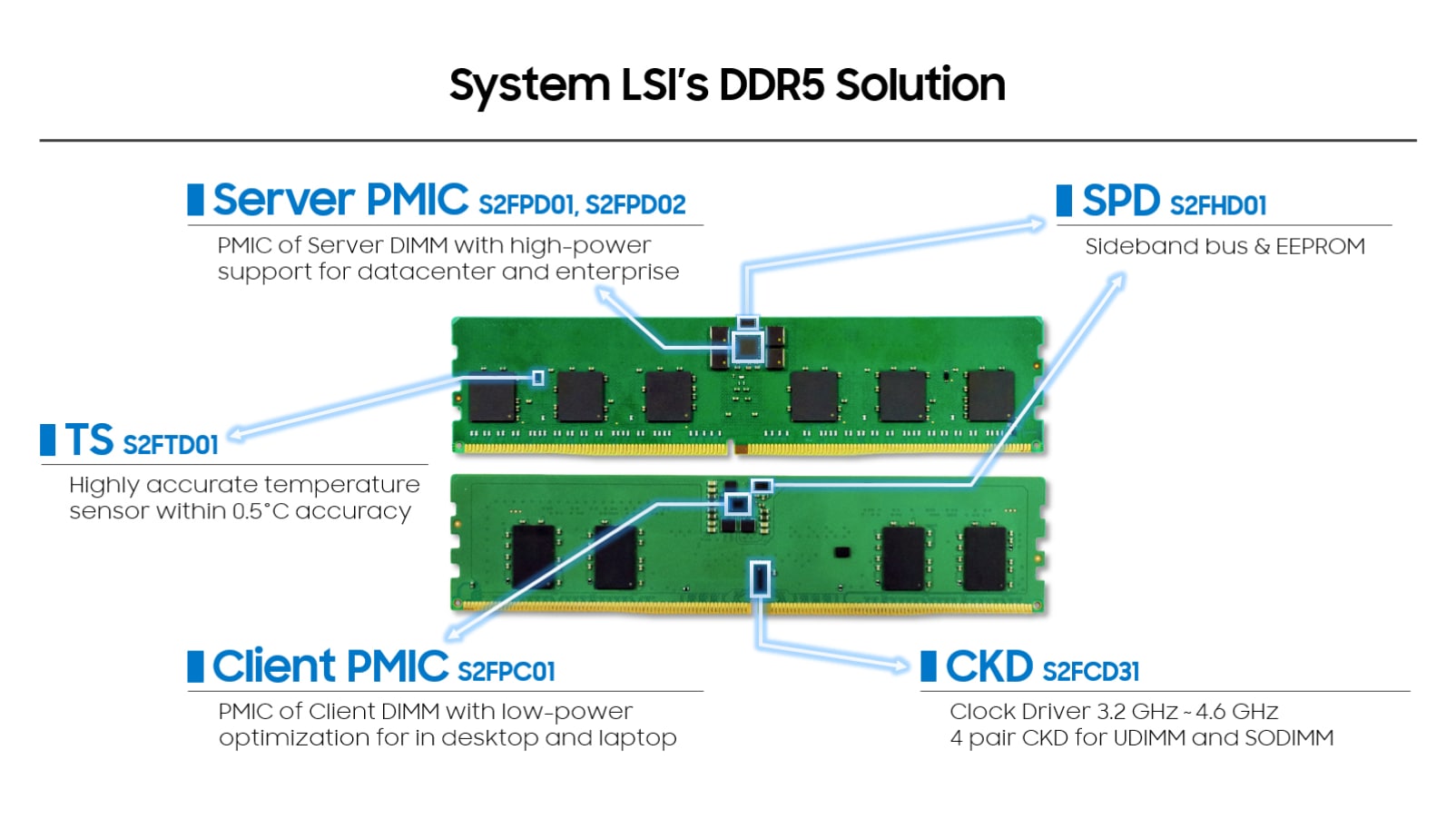

2️⃣ DDR5 的“革命”:PMIC 上 DIMM

DDR5 做了一件非常“狠”的事👇

把最敏感的电源,直接挪到内存条上。

好处:

- 高频噪声本地消化

- 主板 PI 压力下降

- 高频更容易拉

代价(工程师要命的地方):

- DIMM 成了一个高频开关电源

- 共模噪声、EMI 更难控

- DIMM 本身质量差异,直接影响系统稳定性

3️⃣ DDR5 PI 的新难点:

“不是你板子不稳,是 DIMM 在抖”

📌 真实项目里你会遇到:

- A 厂内存 OK

- B 厂同规格内存 Training 不过

- 换批次问题又不一样

👉 PI 已经不完全由你掌控了。

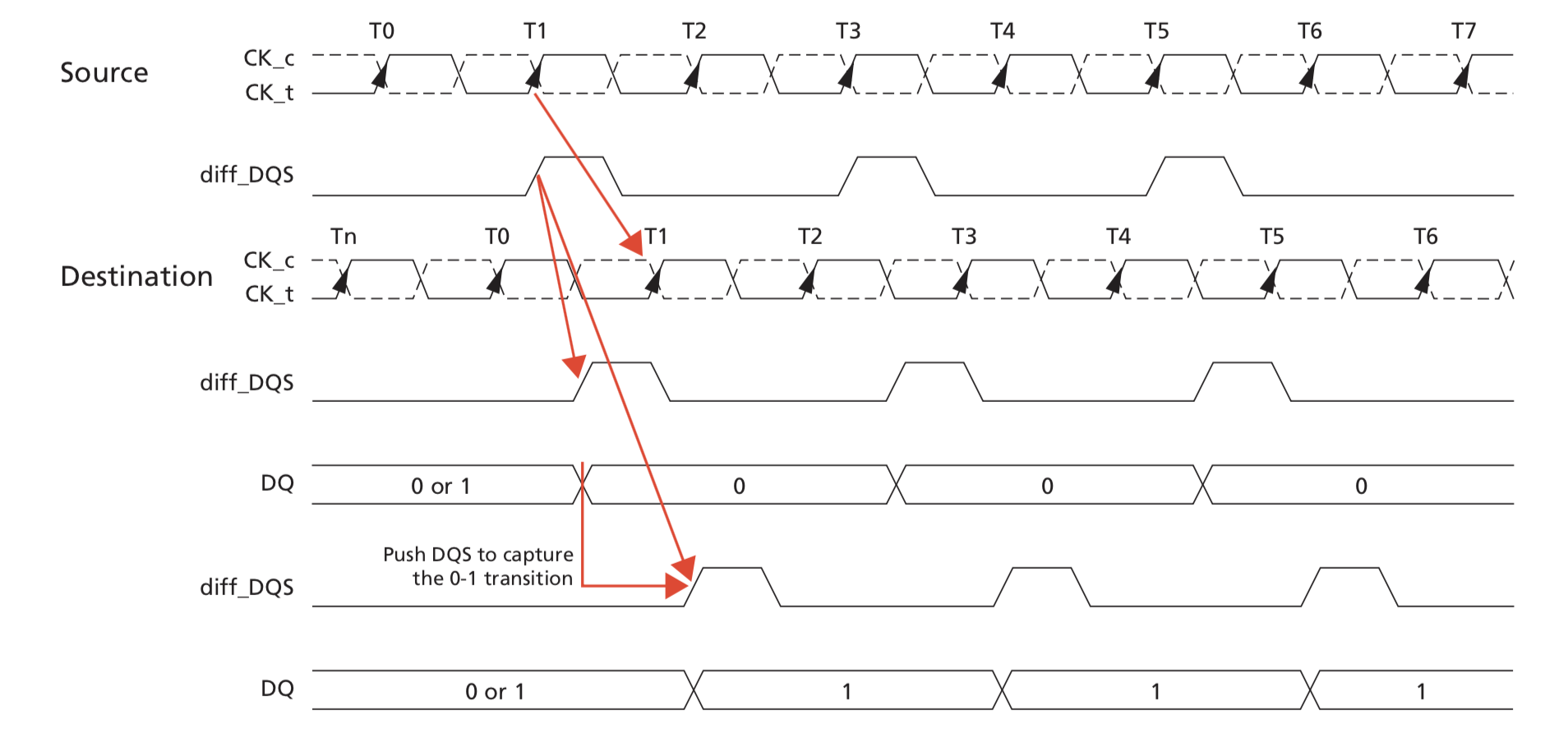

🧪 四、Training:

DDR4 是“加分项”,DDR5 是“生命线”

DDR4 的 Training 心态:

“能训更好,训不好也能跑。”

DDR5 的 Training 现实:

“训不过 = 系统直接起不来。”

原因很简单:

- UI 更短

- SI / PI 窗口更窄

- 靠静态设计已经兜不住

📌 所以 DDR5 的工程重心变成了👇

- Training 顺序

- Vref 搜索范围

- Margin 记录

- 重训策略

🚗 五、车载 / 工业场景下,DDR5 为什么更难?

因为车载环境,刚好踩在 DDR5 的“软肋”上:

- 温度跨度大

- 振动

- EMI 严苛

- 生命周期长

📌 在消费级还能靠:

“重启再训一次”

在车载:

“一次不过,就是功能失效”。

🎯 六、工程师最容易误判的 3 个点

❌ 1️⃣ “DDR5 线更短,SI 应该更容易”

错。

频率涨得更快。

❌ 2️⃣ “PI 交给 DIMM,我就省心了”

错。

DIMM 带来了新的噪声源。

❌ 3️⃣ “Training 是软件的事”

错。

Training 是 SI / PI 的镜子。

🧠 七、一句话把 DDR4 / DDR5 的工程差异说死

DDR4:画线决定成败

DDR5:系统协同决定生死

你如果:

- 只盯 SI → 不够

- 只盯 PI → 不够

- 不看 Training → 基本必翻

🔚 最后一段|总结(送你一句狠的)

DDR5 的难点,不是“它太快”,

而是“它不再容忍单点优秀”。

DDR4 时代,你可以:

- 线画得好

- 其他凑合

DDR5 时代:

SI、PI、Training,缺一个,系统就不陪你玩。

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)