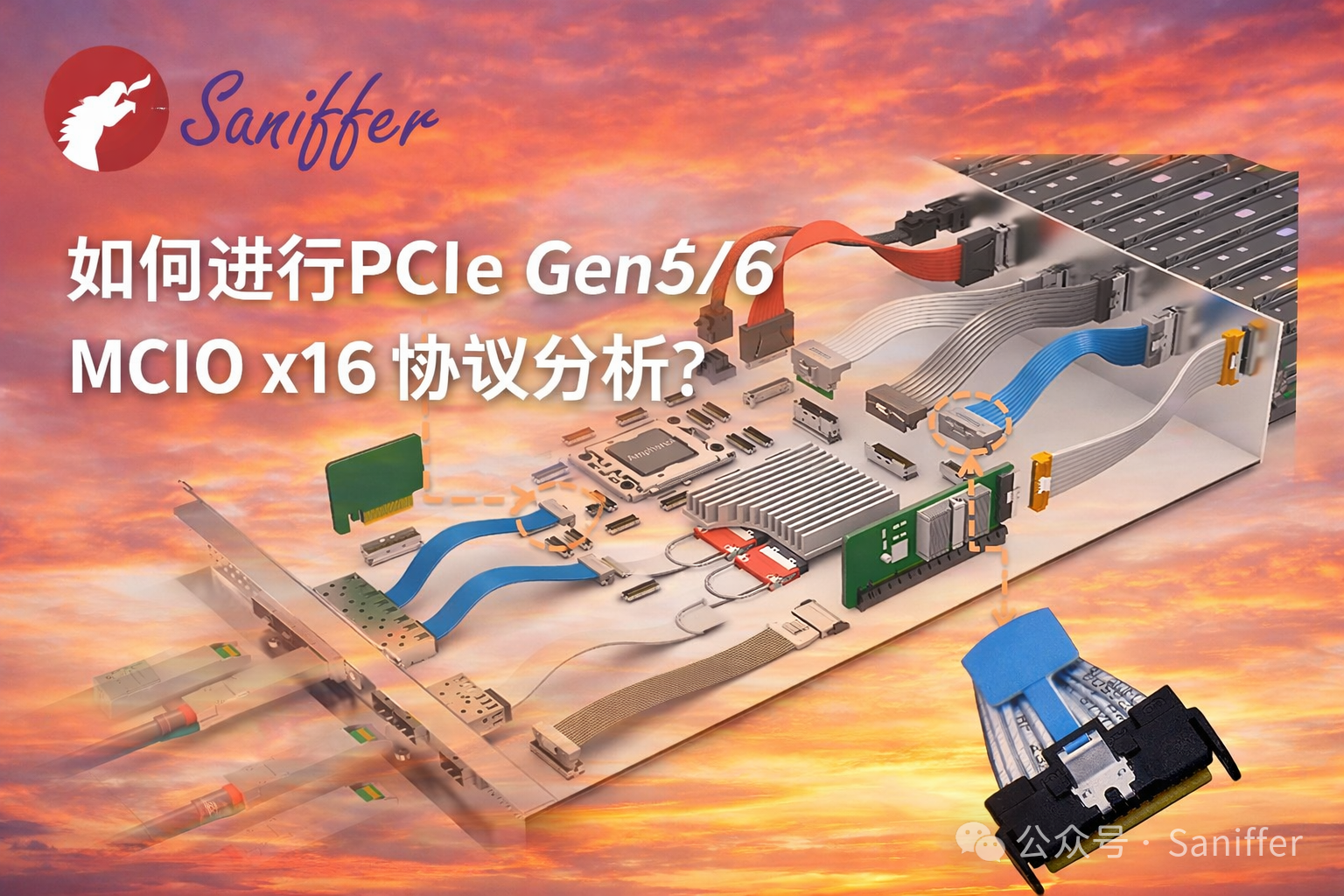

【高清视频】如何分析PCIe 5.0/6.0 x16 MCIO cable链路上的协议问题

本文介绍了SerialTek PCIe Gen5 Analyzer在MCIO接口测试中的实操应用。重点讲解了硬件组成(主机、AIC插卡、MCIO转板)的连接方法,特别强调必须正确连接时钟同步线。详细说明了带内信号、边带信号的接线逻辑及防反插设计,指出测试环境搭建中的多级转接方案。最关键的是指出了软件设置中Device Power必须设为Force High,以及必须正确配置Lane Mapping

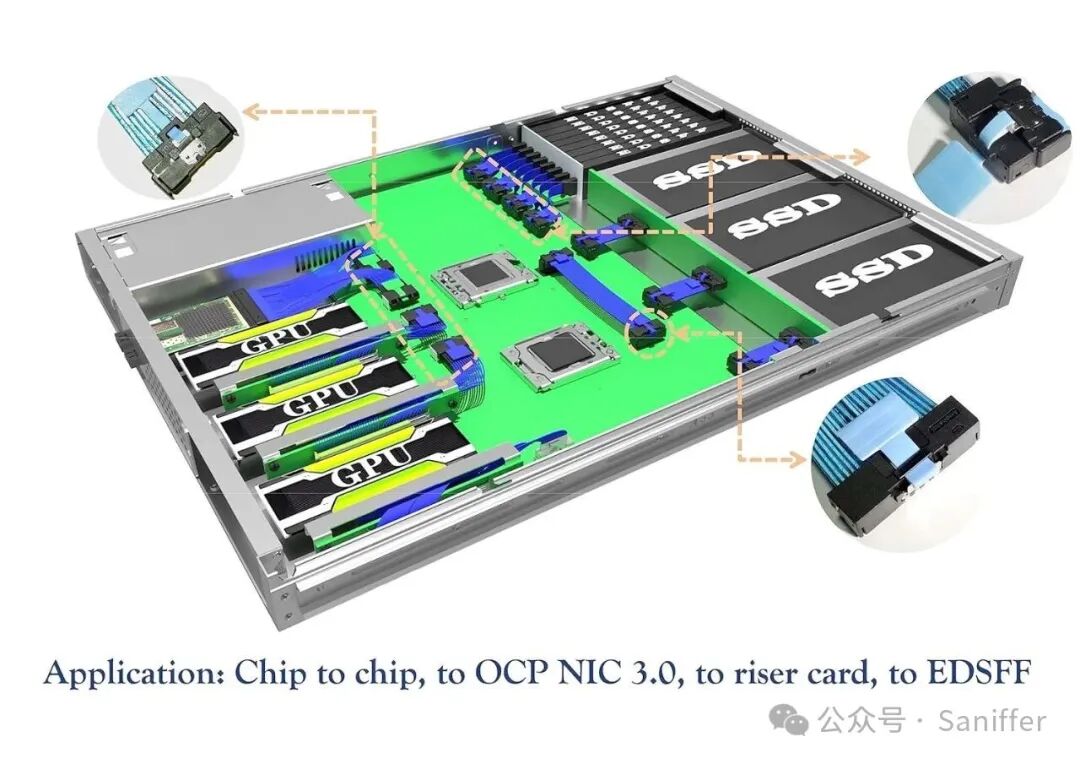

我们在当今的各类服务器和工作站上普遍看到PCIe MCIO x8或者x16 cable connector,一般都是部署在Intel 或者AMD server CPU旁边的主板上,通过2根x8 MCIO cable组成一个x16连接到前面板SSD背板的背面,或者通过RAID看的2x8 MCIO cable连接背板,然后通过背板转接到Gen5 U.2或者EDSFF SSD;当然也经常看见服务器内部不同组件中间使用PCIe MCIO x8/16 cable进行通讯连接。那么我们有的时候碰到PCIe问题的时候就需要通过将PCIe协议分析仪连接在cable中间进行抓取数据分析。很多人没有这方面的实际操作经验,今天的视频就让你或者直观感性的操作体验。

为了方便工程师观看,我们针对本期视频并处理添加了中文字幕供大家参考。如果想看高清视频建议要在电脑上打开上面的视频链接进行观看!创作不易,欢迎分享到朋友圈或者与朋友讨论!如果想搬运我们的视频请告知我们。

【高清视频】如何分析PCIe 5.0/6.0 x16 MCIO cable链路上的协议问题

下面是一份基于该视频总结报告。在忠于原始内容的基础上,对结构进行了系统化重组,方便作为内部培训资料直接使用。

SerialTek Gen5 MCIO x16 Analyzer 使用与接线演示

一、视频目的与适用场景

本视频是一份面向工程人员的实操型培训说明,核心目标是讲清楚以下三件事:

-

SerialTek PCIe Gen5 Analyzer 的基本形态与接口

-

Gen5 MCIO Interposer 的结构、用途及接线方式

-

在 MCIO 场景下,Analyzer 必须进行的关键配置项,否则无法抓取带内流量

视频内容主要服务于以下典型应用场景:

-

PCIe Gen5 / Gen6 测试环境搭建

-

MCIO 接口链路调试与验证

-

非服务器条件下,通过转接与复用方式构建测试拓扑

二、硬件组成概览

1. Analyzer 主机

-

使用的是 SerialTek PCIe Gen5 Analyzer

-

支持 Gen5 x16 带内流量与边带信号抓取

-

通过高速线缆与 Interposer 连接,而非直接插入系统主板

2. AIC x16 Interposer(基础平台)

-

视频中使用的是常见的 AIC 插卡式 x16 Interposer

-

这是一个“基础母板”,通过额外的 MCIO 转板扩展支持 MCIO 接口测试

3. MCIO 转板(Interposer 转接模块)

-

插接在 AIC x16 Interposer 的金手指槽位上

-

两侧各提供 MCIO Gen5 x8 接口

-

额外提供 一根 MCIO x4 接口,用于时钟同步

-

由于横向安装,必须通过蓝色金属支架+螺丝固定,以避免晃动和信号质量问题

三、Analyzer 与 Interposer 的接线逻辑

1. 带内高速信号(In-band Traffic)

-

使用 2 根 QDD 400G 高速线缆

-

从 Analyzer 引出,连接到 Interposer 对应端口

-

插入时需听到明显“咔哒”卡扣声,确保完全就位

-

接线方向无需担心:

-

upstream 对 upstream

-

downstream 对 downstream

-

物理结构已防反插

-

2. 边带信号(Sideband)

-

使用 2 根 Oculink x8 线缆

-

用于承载 PCIe Gen5 x16 所需的低速边带信号

-

Sideband 0 ↔ Sideband 0 Sideband 1 ↔ Sideband 1

-

同样具备防反插设计,按编号一一对应即可

3. MCIO x4 时钟同步线(关键)

-

这根 MCIO x4 Cable 必须连接

-

其唯一用途是 时钟同步

-

如果不接:

-

链路可能无法稳定训练

-

Analyzer 无法正确解码带内流量

-

四、MCIO 转板的安装与固定要点

-

MCIO 转板通过金手指插入 AIC Interposer 的 x16 插槽

-

转板为横向结构,容易因外力导致接触不稳

-

正确安装流程:

-

先松开蓝色支架上的 4 颗螺丝

-

插好转板

-

对齐螺丝孔位并重新拧紧

-

-

固定完成后,转板才具备可重复、稳定测试的条件

五、测试环境的“转接式”搭建思路

由于实验室中没有原生 MCIO 接口的服务器平台,视频中采用了“多级转接”的方式构建测试链路:

Host 侧

-

使用 Gen6 x16 PCIe Switch

-

提供 2 个 MCIO Gen6 x8 下游端口

-

通过 MCIO 延长线接入 Interposer

Device 侧

-

使用 Gen5 插卡设备

-

插在 MCIO x8 ×2 → CEM x16 转板上

-

转板本身为 Gen6 规格,用于 Gen5 测试完全没有问题

线序强调(极其重要)

-

上排:Lane 0–7

-

下排:Lane 8–15

-

绝不能混接

-

一旦将 8–15 接到 0–7,链路将无法正确工作,Analyzer 也抓不到有效数据

六、Analyzer 中“必须设置”的关键软件项

这是整段视频最容易被忽略、但后果最严重的部分。

1. Device Power 设置

-

默认状态:Follow Hardware

-

使用 MCIO Interposer 时,必须改为:Force High

-

否则结果是:

-

只能看到边带信号

-

完全抓不到上下行的带内流量(TLP/DLLP)

-

2. Lane Mapping 设置

-

Analyzer 默认 lane mapping 为 0–15 全直通

-

MCIO Interposer 场景下,必须严格按照转板定义的 lane mapping 设置

-

软件中可通过:

-

x2 / x4 / x8 / x16 翻转

-

多次点击组合

-

实现与实际物理走线一致的映射关系

-

-

除此之外,不需要在其它地方额外配置

总结一句话:

不设置 Device Power + Lane Mapping = 抓不到任何有效带内流量

七、抓包操作流程概述

-

Lock Analyzer

-

因为 Analyzer 支持多人同时访问

-

未 lock 会产生抓包冲突

-

-

点击 Start Capture

-

上电顺序(本实验环境):

-

先给 Device 上电(外接电源)

-

再打开 Host 电源

-

-

链路训练完成后:

-

Analyzer 界面可看到 Gen5 x16

-

表明链路状态正常,可开始分析

-

八、总结与实践建议

-

本视频并非讲“PCIe 协议”,而是极度偏向工程落地的实操说明

-

MCIO 场景下,Analyzer 的使用逻辑与传统 CEM 插卡存在本质差异

-

90% 的问题都不是硬件坏,而是:

-

时钟线未接

-

Lane Mapping 错误

-

Device Power 未 Force High

-

-

强烈建议:

-

初次使用时完全对照视频逐步搭建

-

不要凭经验“觉得应该可以”

-

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)