vivado综合过程中的过约束问题

摘要:本文详细解析了FPGA设计中通过set_clock_uncertainty命令实现过约束优化的方法。该方法通过在布局阶段提高时序要求(增加时钟不确定性),为布线环节预留充足时序预算,其核心优势在于不改变时钟周期和时钟关系。关键技术原理是调整时钟不确定性间接减小有效时钟周期,计算公式涉及系统抖动、离散抖动等参数。使用需遵循严格规范:仅适用于时序接近收敛(WNS在-0.5ns~0)的同步路径,约

目录

若布线完成后时序处于接近收敛的状态,往往源于布局阶段遗留的建立时间裕量不足问题。要解决这一痛点,关键在于为布线环节预留更充足的时序预算,而实现该目标的核心手段是在布局与物理优化阶段提高时序要求 —— 这一操作在FPGA设计中被称为 “过约束”。

Xilinx官方推荐通过set_clock_uncertainty命令实施过约束,其核心优势在于不会改变设计中的时钟周期、占空比参数,也不会破坏不同时钟之间已定义的时序关系,能在不影响基础时钟架构的前提下优化时序收敛。不过使用该方法时需注意两个关键前提:一是仅适用于时钟内路径或跨时钟域路径未完全收敛的场景;二是必须明确添加-setup 选项,确保约束仅作用于建立时间相关路径。

1.时钟不确定性

从技术原理来看,时钟不确定性(Clock Uncertainty)的调整直接影响时序预算分配。建立时间裕量(Setup Slack)的计算遵循特定逻辑,其核心关联公式涉及三大关键参数:建立时间需求(Setup Requirement)、数据路径延迟(Data Delay)以及时钟歪斜(Clock Skew)—— 其中时钟歪斜定义为捕获时钟延迟与发送时钟延迟的差值。当通过set_clock_uncertainty增加时钟不确定性时,实际等效于间接减小了有效时钟周期,从而为时序收敛提供更多调整空间。

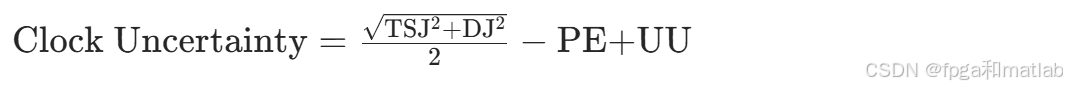

时钟不确定性(Clock Uncertainty)的计算公式如下:

TSJ: 系统抖动(Total System Jitter)

DJ: 由MMCM或PLL引入的离散抖动(Discrete Jitter)

PE: 相位误差(Phase Error)

UU: 用户定义的Uncertainty(User Uncertainty)

2.过约束

Setup Slack = 建立时间需求 - 数据延迟 - 时钟歪斜 + 时钟不确定性

当增加时钟不确定性(Clock Uncertainty)时,相当于给工具提出了更严格的时序要求(间接减小了时钟周期),工具会优先优化这些路径的延迟;布线完成后将不确定性重置为0,即可恢复真实的时序余量。

示例操作

# 布局前:对clk1和clk2→clk3路径施加过约束

set_clock_uncertainty -setup 0.3 [get_clocks clk1]

set_clock_uncertainty -setup 0.4 -from clk2 -to clk3

# 执行布局和物理优化

place_design

phys_opt_design

# 布线前:必须回滚过约束,否则会影响最终时序报告

set_clock_uncertainty -setup 0 [get_clocks clk1]

set_clock_uncertainty -setup 0 -from clk2 -to clk3

# 执行布线

route_design适用场景

仅用于时钟内路径或同步跨时钟域路径;

仅在时序接近收敛(WNS在-0.5ns~0 之间)时使用;

可辅助修复保持时间违例(需配合-hold_fix选项)。

严格限制

过约束量不得超过0.5ns(UG949明确警告,否则会导致过度优化、布线拥塞);

禁止用于异步路径/假路径(工具已忽略这些路径,过约束无效);

必须在布线前回滚,否则会掩盖真实时序问题,导致下游流程无法复现结果。

3.set_clock_uncertainty具体用法

set_clock_uncertainty是Vivado中用于描述时钟时序不确定性的约束命令,核心作用是给时钟路径增加“额外余量”,既可以用于常规时序分析(模拟时钟抖动、误差),也可以用于过约束优化(收紧时序预算)。

常规时序分析

用于模拟时钟的抖动、相位误差等物理不确定性,是设计的 “真实约束”,不需要回滚。

# 示例1:给clk1的建立时间增加0.1ns的不确定性(模拟时钟抖动)

set_clock_uncertainty -setup 0.1 [get_clocks clk1]

# 示例2:给clk2→clk3的跨时钟域路径,增加0.05ns的保持时间不确定性

set_clock_uncertainty -hold 0.05 -from [get_clocks clk2] -to [get_clocks clk3]过约束优化

仅用于布局 / 物理优化阶段,布线前必须回滚为0,是临时约束。

# 步骤1:施加过约束(针对WNS=-0.2ns的clk1路径)

set_clock_uncertainty -setup 0.3 [get_clocks clk1]

# 步骤2:执行布局/物理优化

place_design

phys_opt_design

# 步骤3:布线前回滚(恢复真实约束)

set_clock_uncertainty -setup 0 [get_clocks clk1]跨时钟域路径的精准约束

通过-from/-to指定源/目标时钟,仅对特定跨时钟域路径生效:

# 给“clk_a→clk_b”的路径,施加0.2ns的建立时间过约束

set_clock_uncertainty -setup 0.2 -from [get_clocks clk_a] -to [get_clocks clk_b]更多推荐

已为社区贡献191条内容

已为社区贡献191条内容

所有评论(0)