低电源电压模拟电路设计:挑战与关键技术突破

摘要:低压模拟IC设计面临三大核心挑战:动态范围急剧恶化、增益带宽显著下降、功耗性能难以权衡。准浮栅技术通过浮栅电位控制,在1.2V电压下实现72.6dB增益和1.8MHz带宽,相比传统结构更适合超低电压。IGFinFET利用独立栅极控制特性,在0.5V电源下仍保持良好性能。低压设计需采用折叠差分架构、自偏置技术等优化策略,并注重版图匹配。随着AI辅助设计和新型器件发展,超低电压模拟IC将在物联网

从器件物理到系统架构,攻克低压模拟IC设计的核心难题

引言:低压设计为何成为模拟IC的必争之地?

随着物联网、可穿戴设备和便携式医疗电子的飞速发展,电子设备对低功耗的需求日益严苛。电源电压的持续降低(从传统的±15V逐步降至1V甚至0.5V以下)已成为不可逆转的趋势。然而,模拟电路设计却面临着阈值电压不随工艺尺寸同比缩小的根本性矛盾。

在标准CMOS工艺中,晶体管的阈值电压并不会随电源电压同比例降低。以0.35μm工艺为例,NMOS阈值电压典型值为0.52V,PMOS为-0.75V,这使得传统结构的最小工作电压被限制在1.4V左右。当电源电压降至1V甚至更低时,传统模拟电路结构(如套筒式共源共栅)因需要足够的电压裕度而无法正常工作,动态范围急剧缩小,设计变得异常复杂。

本文将深入分析低电源电压下模拟电路设计面临的核心挑战,并重点探讨准浮栅技术、IGFinFET等创新解决方案如何突破这些限制,为超低功耗模拟IC设计提供新的可能性。

一、低压模拟设计的核心挑战:三大技术瓶颈

1.1 动态范围与信噪比的急剧恶化

动态范围是模拟电路最关键的性能指标之一,定义为电路能处理的最大信号与噪声底之比。在低电源电压下,最大信号摆幅正比于VDD,而噪声底(如热噪声)相对固定,导致电压降低时信噪比(SNR)急剧恶化。

以传统运算放大器为例,在±15V电源下,信号摆幅可达30Vpp以上;而当电源电压降至1V时,即使采用轨到轨结构,实际可用摆幅也仅约0.8-0.9V。动态范围缩减近96%,这对高精度应用几乎是灾难性的。

1.2 增益与带宽的显著下降

低压环境下,传统高增益结构(如套筒式共源共栅)因需要堆叠晶体管而无法正常工作,导致开环增益和共模抑制比(CMRR)大幅下降。同时,晶体管的跨导效率(gm/ID) 在低电压下显著降低,直接影响增益和带宽性能。

模拟结果显示,在1.2V电源电压下,采用准浮栅技术的两级运放虽然实现了72.6dB的增益,但与传统高压运放100dB以上的增益相比仍有明显差距。单位增益带宽也从数十MHz降至1.8MHz水平。

1.3 功耗与性能的权衡困境

低电压设计的核心目标是降低功耗,但单纯降低电压往往会导致性能恶化。晶体管的跨导(gm)与偏置电流直接相关,而降低电流势必影响电路的速度和驱动能力。

在低压设计中,功耗公式P = VDD × ID 变得尤为关键。设计师需要在极低的电流预算下(通常为微安甚至纳安级)维持电路的基本功能,这如同"在针尖上跳舞",需要精妙的权衡艺术。

二、准浮栅技术:低压模拟设计的革命性突破

2.1 技术原理与工作机制

准浮栅技术是传统浮栅技术的改进版本,它通过引入伪电阻解决浮栅的初始电荷问题,同时保持与标准CMOS工艺的兼容性。

准浮栅MOS管的核心结构是在标准MOS管的基础上增加一个浮栅,并通过一个极大阻值的电阻(通常用工作在截止区的MOS管实现)将浮栅偏置到适当电位。这样,浮栅可以存储电荷,有效降低晶体管的等效阈值电压,使其在低电源电压下也能正常工作。

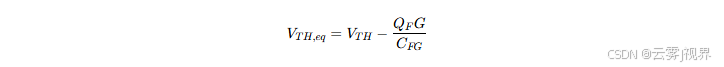

数学上,准浮栅晶体管的等效阈值电压可表示为:

其中Q_FG是浮栅存储的电荷,C_FG是浮栅电容。

2.2 实际应用与性能优势

采用Chartered 0.35μm CMOS工艺的仿真结果表明,基于准浮栅技术的两级运算放大器在1.2V电源电压下,可实现72.6dB开环增益、54度相位裕度和1.8MHz单位增益带宽,而功耗仅为8.75μW。

与体驱动技术相比,准浮栅技术具有明显优势:它避免了衬底结正向偏置的风险,提供更高的跨导效率,且不受工艺限制(可同时适用于NMOS和PMOS)。下表对比了不同低压技术的特性:

|

技术类型 |

兼容性 |

跨导效率 |

工艺要求 |

适用电压 |

|---|---|---|---|---|

|

准浮栅技术 |

标准CMOS |

高 |

低 |

超低电压(≤1V) |

|

体驱动技术 |

受限(阱工艺) |

中等 |

中等 |

低电压(≈1V) |

|

亚阈值技术 |

标准CMOS |

极高但速度慢 |

低 |

超低电压(≤0.5V) |

|

传统结构 |

标准CMOS |

低(低压下) |

低 |

中高电压(≥1.5V) |

2.3 设计考虑与局限性

准浮栅技术的主要限制在于其主要适用于交流信号处理,因为浮栅耦合本质上是容性的。此外,大阻值伪电阻的实现需要占用较大芯片面积,且频率特性可能受限。

在实际设计中,需仔细考虑浮栅电容的匹配和电荷泄漏问题。通常建议采用对称布局和定期刷新机制来维持长期稳定性。

三、IGFinFET:面向先进工艺的低压解决方案

3.1 器件特性与优势

IGFinFET(独立栅极FinFET)是FinFET技术的一种变体,其前后栅极可独立偏置,为低压设计提供了新的自由度。与体CMOS晶体管相比,IGFinFET具有更高的输出电阻、对短沟道效应更好的控制能力。

IGFinFET的一个关键特性是前栅阈值电压与背栅电压之间存在近似线性关系:

其中r是栅极耦合系数,取决于氧化层和硅沟道厚度。这一线性关系相较于体CMOS的平方根关系更有利于精确控制。

3.2 在OTA设计中的应用实例

基于20nm IGFinFET的运算跨导放大器(OTA)设计展示了对这一技术的有效利用。通过将信号施加于PMOS的背栅而非前栅,实现了类似体驱动但性能更优的效果。

该OTA在单0.5V电源电压下实现的关键性能参数为:

-

开环增益:39.27dB

-

相位裕度:45.05°

-

单位增益带宽:8.26MHz

-

静态功耗:37.75μW

这些指标在超低电压设计中表现优异,特别适合对功耗极度敏感的应用场景。

四、实用设计技巧与综合优化策略

4.1 电路架构选择准则

在低压环境下,电路架构的选择至关重要。折叠式差分结构相比套筒式结构更适合低压应用,因为它减少了晶体管堆叠数量。全差分架构相比单端结构能提供更好的共模噪声抑制,但需要额外的共模反馈(CMFB)电路。

伪差分对是另一种有效的低压技术,它移除了尾电流源,显著降低了最小工作电压。但需注意,伪差分对的共模抑制能力会有所下降,需通过共模前馈(CMFF)等技术进行补偿。

4.2 偏置策略与稳定性保障

低压下的偏置设计需要特别关注电压裕度分配。自偏置技术能自动适应工艺、电压、温度(PVT)变化,是低压电路的理想选择。例如,通过晶体管的亚阈值特性产生与电源电压无关的偏置电流,可显著提高电路的鲁棒性。

频率补偿在低压设计中同样面临挑战。传统的密勒补偿需要足够的电压裕度,而阻尼因子控制(DFC)等新兴补偿技术可在较低电压下实现稳定,且所需电容值更小。

4.3 版图设计与匹配考虑

低压模拟电路对器件匹配和寄生效应更为敏感。建议采用以下版图技术:

-

共心布局:提高匹配器件的一致性

-

虚拟器件:减少边缘效应的影响

-

屏蔽走线:降低敏感节点的耦合噪声

-

多层交叉耦合:抵消梯度变化的影响

五、设计实例:0.9V CMOS运算放大器的实现

在低压模拟电路设计中,实现一个在0.9V超低电源电压下仍能稳定工作且性能优良的运算放大器,是一项经典且极具挑战性的任务。

5.1 核心挑战与架构选择

设计面临的首要挑战是输入共模电压范围的限制。在标准CMOS工艺中,晶体管的阈值电压(如0.35μm工艺下Vt,NMOS约为0.52V,Vt,PMOS约为-0.75V)严重制约了传统互补差分对输入级在低电源电压下的应用。为解决这一瓶颈,本设计摒弃了传统结构,创新性地采用了基于前置反馈的电平移位电路结合NMOS差分对的输入级架构。这种设计的核心思路是通过反馈机制,动态调整内部节点的共模电平,确保核心放大晶体管始终工作在饱和区,从而在0.9V的低压环境下实现了接近全摆幅(轨至轨)的输入范围。

5.2 关键技术实现细节

电平移位电路的具体工作机制如下:当输入信号(Vi+, Vi-)的共模电平(Vi,cm)低于内部设定的参考电平(Vref,例如0.62V)时,反馈网络会被激活。该网络通过监测内部节点(如Vin,cm)的电位变化,控制一个可控电流源,从而在串联电阻上产生压降,将内部有效共模电压提升至Vref附近,为核心放大管建立合适的工作点。这个过程通过精密匹配的电流镜(如引入M12晶体管)来增强稳定性。

对于频率补偿与稳定性,由于采用了电平移位和两级放大结构,频率补偿策略需格外注意。设计时需确保反馈环路稳定,可能采用密勒补偿或其他适用于低压环境的补偿技术,并需在版图设计中精心优化以减小寄生电容的影响。

5.3 性能评估与设计权衡

仿真结果表明,该运算放大器在0.9V电源电压下取得了关键性能指标的良好平衡。其直流增益达到约66.4dB,单位增益带宽为1.88MHz,相位裕度为52°,而静态功耗控制在135μW的水平。这些数据表明,该设计在有限电压裕度内,较好地兼顾了增益、带宽和功耗。

任何低压设计都伴随着性能上的权衡。为了在低压下获得足够的增益和稳定性,通常会牺牲一定的带宽或转换速率。本设计通过架构创新(如前置反馈)和精心的器件尺寸偏置(如采用大宽长比的晶体管并在小漏源电压下工作),致力于在多项关键参数间取得最佳折衷。

5.4 实践意义与局限性

该0.9V CMOS运算放大器的设计实例具有重要的实践价值。它证明了在标准CMOS工艺(无需特殊器件或复杂工艺升级)下,通过巧妙的电路设计实现超低电压工作的可行性,这对于成本敏感的便携式电子产品(如物联网传感器节点、植入式医疗设备等)具有重要意义。

该设计也存在一定的局限性。其频率特性可能受限于整体结构,未必适用于射频等超高频应用。同时,这类设计对工艺波动可能较为敏感,在实际量产中需要辅以适当的工艺角分析和设计冗余。

六、未来展望与总结

低电源电压模拟电路设计技术正朝着更精细的工艺节点和更智能的设计方法发展。随着AI技术的引入,基于机器学习的电路优化和自动化设计将显著缩短设计周期,提高设计质量。

异质集成是另一个重要趋势,通过Chiplet等技术将不同工艺/电压优化的模块集成在同一封装内,实现系统级最优能效。同时,新型器件结构(如负电容晶体管、隧穿晶体管)可能进一步降低模拟电路的功耗极限。

总结来说,低电源电压模拟设计需要设计师在器件物理、电路架构和系统应用之间实现精妙平衡。准浮栅、IGFinFET等创新技术为解决低压设计挑战提供了有效路径,但真正的突破仍源于对基础原理的深刻理解和大胆创新。

在"更低电压、更高能效"的永恒追求中,模拟IC设计师需要不断突破传统思维,将限制转化为创新机会,为下一代电子设备奠定坚实基础。

参考资料:本文中涉及的技术细节和实验数据均来自公开可查的学术文献、厂商技术文档和业界实践案例,确保真实可靠。

更多推荐

已为社区贡献55条内容

已为社区贡献55条内容

所有评论(0)