时序约束-(自学)-set_input_delay

描述:

先从Vivado自带的约束语句开始学习

在Language Template>XDC>Timing Constraints>Input Delay Constraints>Source Synchronous

选择哪种约束模板来使用的话,看看哪个合适自己当前应用场景。

源同步

源同步:时钟和数据都来自外部设备,数据随路时钟一起进入FPGA芯片。

数据的改变时间是一个区间

T表示1个时钟周期

Tsu(setup time /建立时间)

Th(hold time/保持时间)

Tchange:跳变时间区间(方便自己理解)

T = Tsu + Th + Tchange

input_delay的两个参数就是Tchange这个时间区间的左侧和右侧,即最快进行数据改变的时间和最晚进行

-max(最大延迟):相对于采样时钟沿,新数据最晚到达的时间。(再晚一点的话,建立时间就无法满足)

-min(最小延迟):相对于采样时钟沿,新数据最快到达的时间。(只要过了保持时间,数据就可以改变)

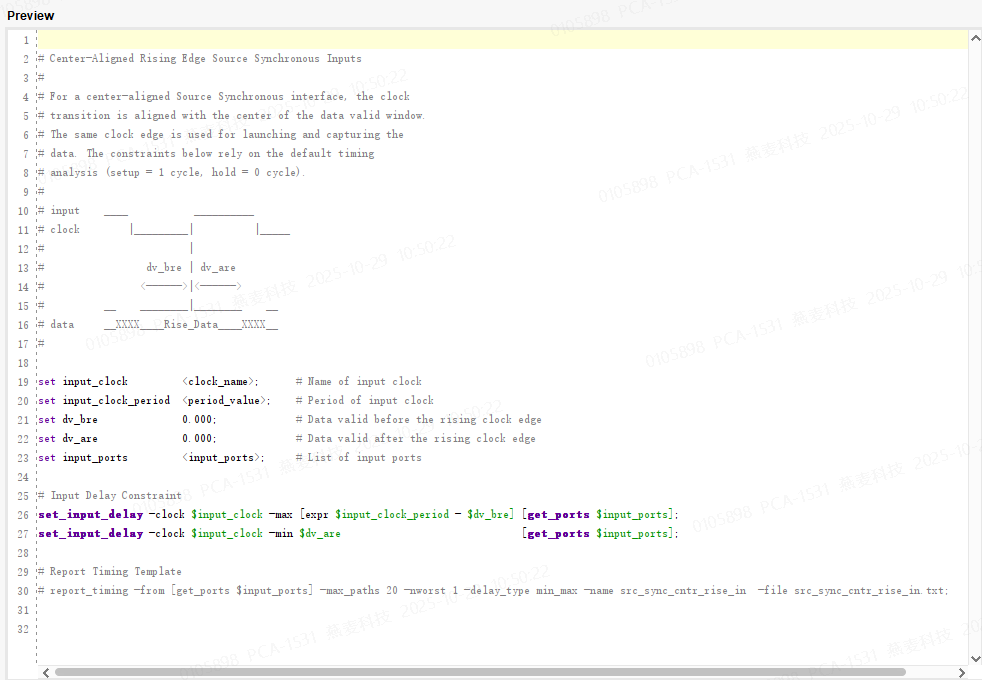

一、Center-Aligned

操作示例:中心对齐模板

假设时钟周期是10ns

dv_bre是指相对于时钟上升沿(采样沿)之前,进来的数据保持有效的最短时间(数据到达FPGA能接受的最晚的时间),也就是所需的建立时间(Tsu),假设是6ns。

dv_are是指相对于时钟上升沿(采样沿)之后,进来的数据需要保持有效的时间(Thold),假设是3ns

下面是基于时钟上升沿采样的约束示例:

#创建时钟 10ns/T

create_clocks -name CLK -period 10.000 -waveform {0.000 5.000} [get_ports {CLK}];

#设置输入约束

set_input_delay -clock CLK -max 4 [get_ports {DATA}];#10-6=4

set_input_delay -clock CLK -min 3 [get_ports {DATA}];

如果对下降沿做约束,则需要在语句后添加 -clock_fall;

#设置输入约束

set_input_delay -clock CLK -max 4 [get_ports {DATA}] -clock_fall;

set_input_delay -clock CLK -min 3 [get_ports {DATA}] -clock_fall;

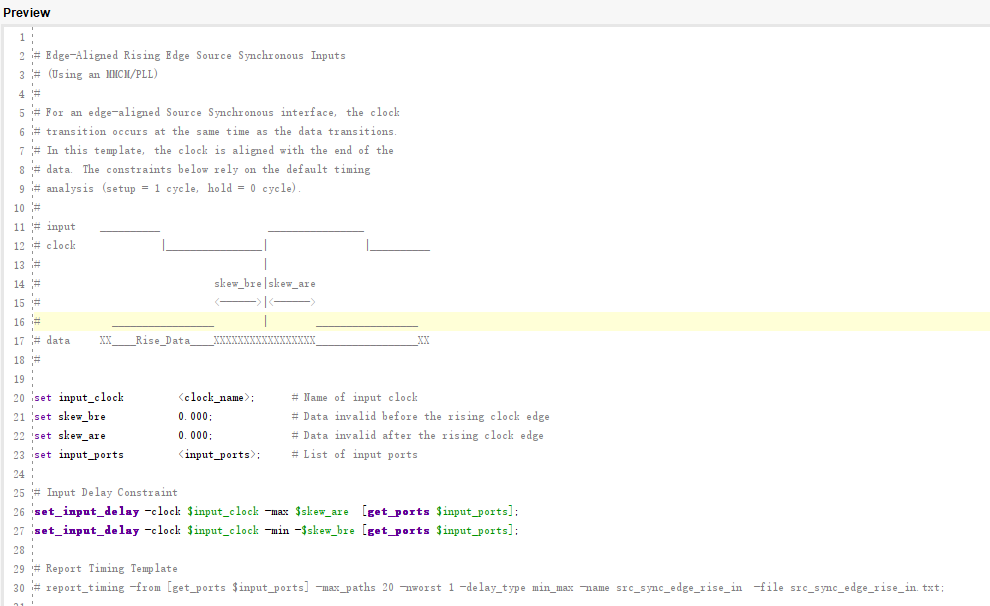

二、Edge-Aligned(Clock with MMCM)

解释:属于源同步输入的时钟和数据,是指进来的外部时钟,经过了MMCM/PLL的倍频或者其他,产生的时钟,去对输入数据做处理

如下图所示,我们只需要描述外部时钟和外部数据的到达FPGA管脚的关系。

输入Rising_Data是和输入时钟上升沿对齐的,所以这里要告诉FPGA,经过了MMCM的时钟上升沿和输入数据的关系。

所以-max(数据最晚进行改变的时间)按照上面所讲的理解,-max应该设置为skew_are的时间

如果Rising_Data是改变时间在上升沿之前,就要设置为负数,-min应该设置为(-skew_bre)的时间

如果Rising_Data是改变时间在上升沿之后,就要设置为正数,-min应该设置为skew_bre的时间

1.set_input_delay描述了外部时钟(ext_clk)和外部数据(ext_data)的关系

2.外部时钟经过MMCM,产生时钟gen_clk,这样系统也知道了gen_clk和ext_clk的关系(create_generate_clock)

3.时钟路径:ext_clk(pin) -> mmcm -> genclk -> 采样寄存器时钟端口

4.数据路径:ext_data(pin) -> 内部逻辑 - > 采样寄存器数据端口

5.执行时序分析。

三、Edge-Aligned(Clock directly to FF)

解释:属于源同步输入的时钟和数据,时钟不经过MMCM/PLL,直接使用,时钟和数据直连FF的时钟端口和数据端口。

如下图所示:我们只需要约束外部时钟和外部数据到达FPGA管脚的关系即可。

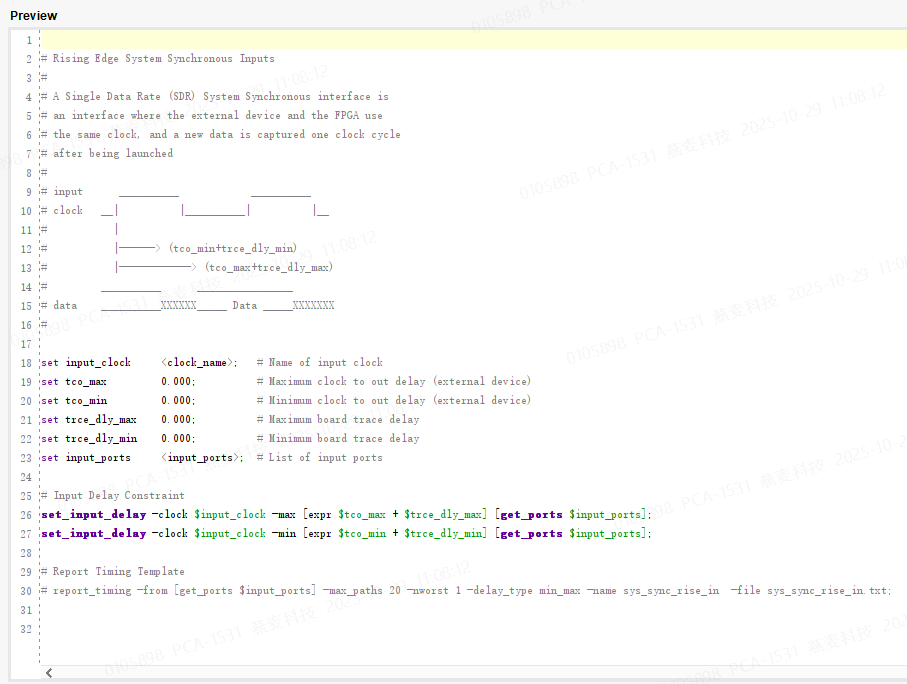

二、System Synchronous

实际上两种不同的约束模板意义是一样的。

Tco_max + Trce_dly_max代表了从芯片输出的最大延时+经过PCB板的最大延时。

Tco_min + Trce_dly_max则反之

对建立时间的约束-max ,至少需要在建立时间Tsu前保持稳定,输入延时+建立时间不能大于一个时钟周期。

Tco(芯片出来)+Tpcb(板件走线)+ Tsu(建立时间) ≤ T(时钟周期)

Tco(芯片出来)+Tpcb(板件走线) ≤ T(时钟周期)- Tsu(建立时间)

所以

-max需要设置的时间就是用T-T(setup time)

-min需要设置的时间就是用T(hold time)

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)