PCIE RX一致性测试之调试篇

简单聊聊LEQ测试中出现测试Fail的情况如何进行调试!

简单聊聊LEQ测试中出现测试Fail的情况如何进行调试!

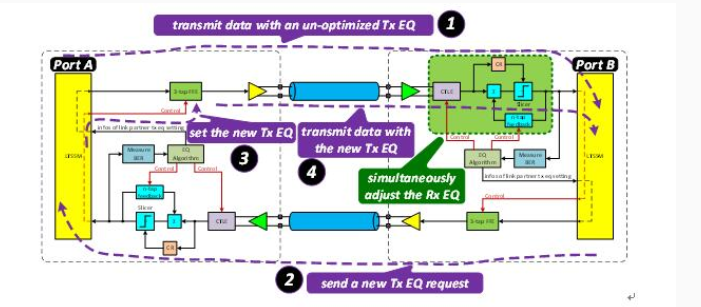

首先需要了解下,TX和RX端是如何进行协商的呢?

(1)一般在测试之初会对TX端的EQ有一个预设值,一般会为P5或者P6,发送端发送TS1/TS2序列(其中包含了TX EQ配置信息);

(2)接收端根据接收到的信号情况来判断通道的特性,以此为依据通过内部算法处理配置合适的均衡参数(CTLE/DFE),并判断处理后的信号是否满足,如果不满足则发送一个请求序列TS1,请求发送端更新EQ配置(至于内部算法是如何处理数据并进行判断和调整的,有机会再详细解释);

(3)发送端接收到请求后,调整EQ,重新发送TS1/TS2序列;

(4)发送和接收端会不断重复(1)~(3)的步骤,直到得到满足要求的发送端(FFE),接收端(CTLE/DFE)配置,或者协商时间超过最大限制时间,则退出循环,进入协议层状态机的下一个状态;

整个协商过程大致如图:

那么,协商的过程会对TX和RX所有可能得参数配置进行遍历配置嘛!从当前的测试经历来看,答案是否定的!正如我们使用IBIS-AMI模型去仿真的时候,如果将接收端设置为自适应的话,有可能自适应出来的结果并不是最优解!

那么,自适应算法的逻辑是怎么样的呢,待后续更新....,但是因曾通过手动配置得到比自适应更优的眼图仿真结果,以此推测,可能自适应算法会得到睁开的眼睛,但自适应出来的配置不一定是最优解。

重点来了,那么,如果测试Fail的话,要如何进行调试?

如果测试fail可能得原因大体可以分为两部分:协议层状态机问题和硬件方面的问题,而硬件方面的问题又可以细分为校准问题、均衡协商配置问题、DUT硬件设计问题,下面就逐一进行说明:

(1)校准问题

可以参考上一篇分享内容《PCIE4.0 接收端链路均衡测试》压力眼图校准部分,校准的时候需要关注测试点位置及所需要关注的指标是否满足协议规定的范围;

(2)均衡协商配置问题

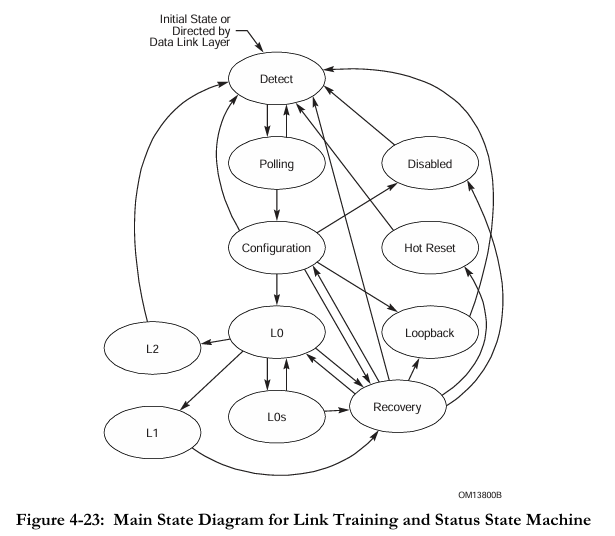

这首先要关注的就是,当你的硬件测试环境准备就绪之后,是否可以通过软件配置让设备能够按照已有的逻辑规则正确的运转起来(我理解这个就是前面一直描述的状态机),而均衡协商的过程所涉及的状态机就是链路训练和状态转换状态机即LTSSM如下图:

LTSSM所涉及的比较关键的几个状态:

-

Detect(检测状态):设备持续检测对端是否连接了一个接收器。

-

Polling(轮询状态):一旦检测到对端设备,双方开始交换训练序列(TS1/TS2有序集),协商共同的链路速度和电气参数。

-

Configuration(配置状态):协商并确定链路最终使用的通道数

-

L0(正常工作状态):这是链路的全功能活动状态。所有正常的数据包(TLP、DLLP)都在此状态下传输。

-

低功耗状态(L0s, L1, L2):L0s:一种极快的低功耗状态,可以快速进入和退出,用于在数据流短暂空闲时节省功耗;L1:比L0s更深的节能状态,唤醒时间稍长;L2/L3 Ready:更深的睡眠状态,涉及主电源的关闭。

-

Recovery(恢复状态):当链路需要动态改变某些参数时(例如,改变链路速度、通道宽度,或者重新进行位锁定/符号锁定),就会进入此状态。它也是从低功耗状态(如L1)恢复到的状态。而该状态又含有四个子状态:phase0/1/2/3,其中,Phase 0:决策与准备阶段;Phase 1:速度切换阶段;Phase 2:重新轮询与配置阶段;Phase 3:恢复完成阶段

-

Loopback(环回状态)、Hot Reset(热复位状态)等:链路调试、测试或强制复位。

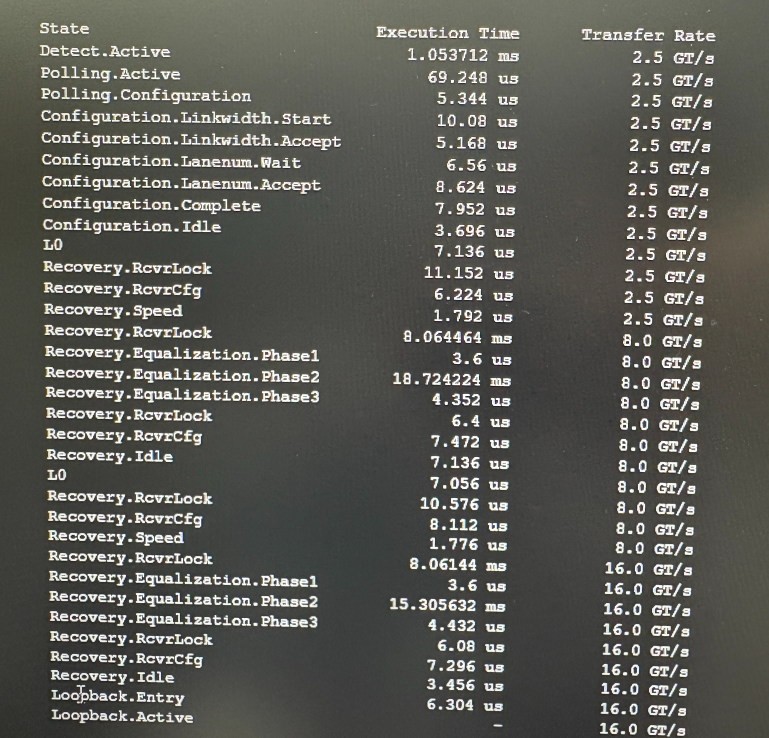

如下为实际测试中的log文件,可以比较直观的观察到整个状态机转换的过程:

一旦出现状态软换问题就会在相应的环节退出或者报错,很容易定位到是哪个状态出现了问题,但是如何去调通整个状态就涉及软件能力了,小编也是没有更多能力给出解决思路了;

(3)DUT硬件问题

如果整个状态流转比较完整,但不能跑到相应速率,就极有可能是硬件设计上的问题,可以分别从以下几个角度来尝试调试:

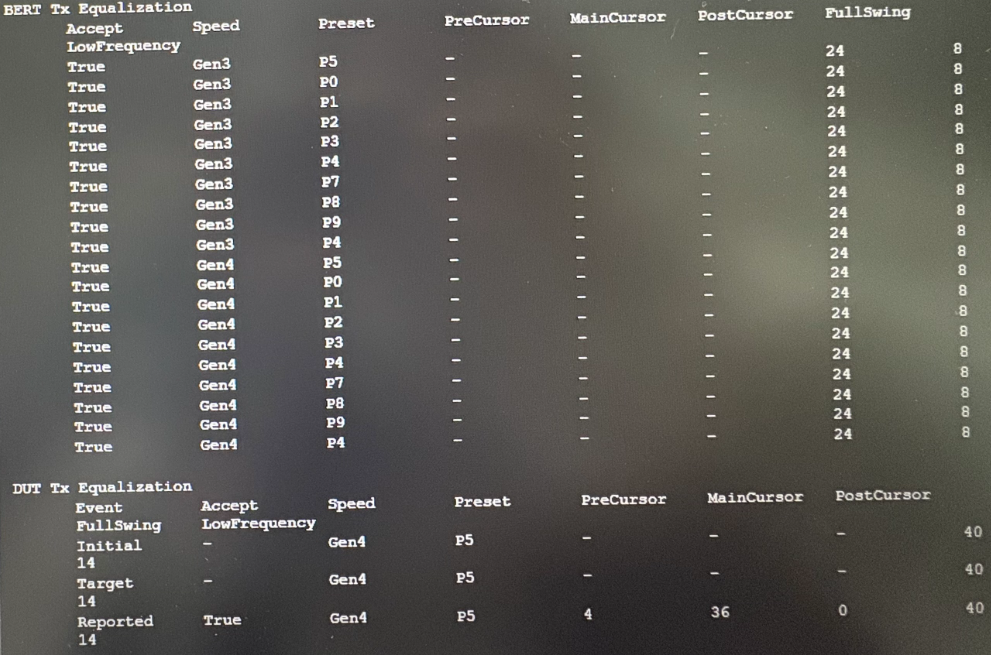

●回环路径DUT TX的EQ配置是否能够保证回环路径不会引入新的误码,可以通过手动在测试软件上调整preset来实现,可以优先尝试P7或者P8;

●通过Log文件查看BER TX EQ是否已经遍历所有preset,如果没有的话,也有可能是BER TX EQ不是最优配置,可以通过一致性软件上手动配置仿真中最佳的preset来验证;

●小步进调整ISI板通道,逐步减小链路插损,如果大的ISI通道 FAIL,小插损通道PASS,则可能是DUT通道插损超标导致,当然也可能是芯片本身的能力不足导致,但一般芯片能力我们很难决定,只能从板级做调整优化,所以即使是芯片能力不足,也只能从板级设计上去给芯片留出更多裕量来解决问题;

●测试TDR,查看DUT设计是否有明显阻抗不连续点导致链路反射严重,抖动超标;

一般后两个问题,如果提前在DUT的芯片引脚附近有测试点,通过测试插损或者眼图的方式会更直观定位,但一般在产品中并不会有这样的预留,所以只能通过以上方法来粗略推断;

---------------------------------------------------------------------------------------------------------------------

个人理解,仅供参考,如有不严谨,请多多指教!

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)