【SI 思维升级】PCB CCL材料到顶? 如何提升损耗限制? 一文搞懂Retimer!

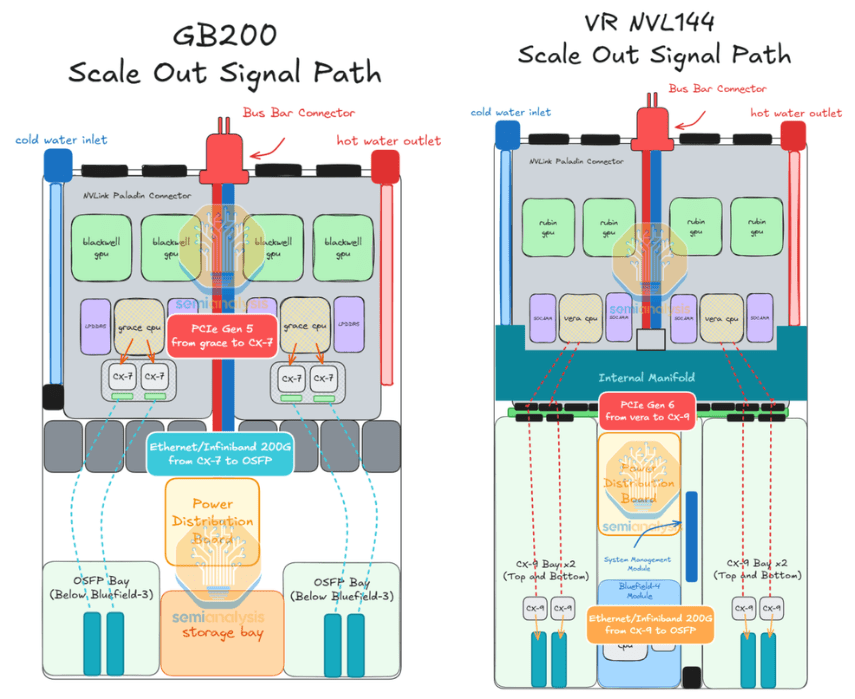

最近nVIDIA下一世代Vera Rubin架构开始热烈地被讨论,由于取消Internal Flyover Cable的关系,预计会使用到最新的PCB材料,例如石英布。也听到有人在讨论说,没有Cable来降低损耗,是否会使用到Retimer?再加上AWS明年的新ASIC – Trainium 3会使用到大量的PCIe Retimer/Switch,让PCIe Retimer界的霸主 – Aster

最近nVIDIA下一世代Vera Rubin架构开始热烈地被讨论,由于取消Internal Flyover Cable的关系,预计会使用到最新的PCB材料,例如石英布。 也听到有人在讨论说,没有Cable来降低损耗,是否会使用到Retimer? 再加上AWS明年的新ASIC – Trainium 3会使用到大量的PCIe Retimer/Switch,让PCIe Retimer界的霸主 – Astera Labs开始被很多人关注,不如,我们来聊聊Retimer跟他的弟弟Redriver吧!

高速通道损耗规格影响是否使用Redriver or Retimer

我想我们在之前的文章:

AI Rack架构高速互连的挑战:损耗设计与信号完整性的设计框架

800G → 1.6T:PCB CCL 材料如何影响信号完整性与市场走向?

就已经有简单聊过损耗对于SI的影响,基本上损耗越大,SI就会越差,这个趋势基本保持不变,所以在高频高速的应用上,我们才会一直探索是否有更新的材料或设计可以进一步降低损耗!

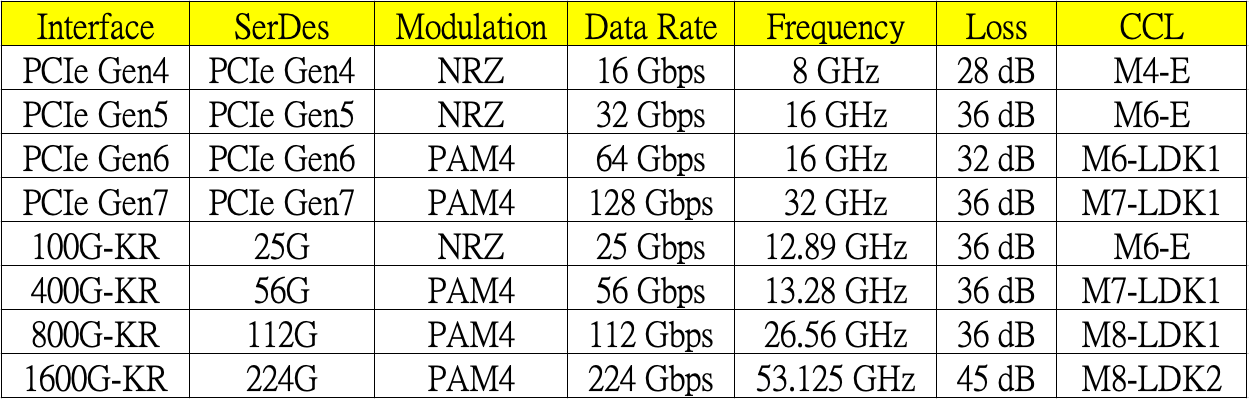

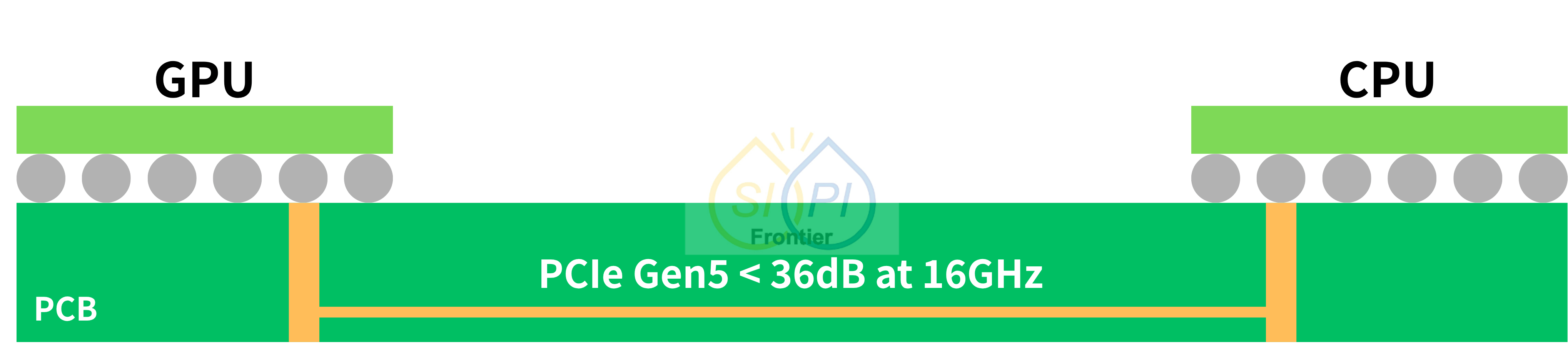

我们在看损耗的时候,会需要考虑各种高速接口,不同的高速接口会有不同的损耗极限,且Nyquist Frequency也不同。 例如PCIe Gen5的频率是16GHz,Silicon-Siicon(或者说Bump-Bump)的损耗极限为36dB,意思是超过36dB SI就会很差; 而现在正如火如荼展开的1.6T,则是要在53.125GHz时,损耗要保持小于45dB。 这些是基于理想状况下(考虑无反射、无信号或是电源干扰)能接受的结果,一般而言设计者还会自行保留一些损耗值当作设计Margin。

如果高速通道的Bump-Bump Loss已经来到极限,那要怎么办?

何时使用Redriver or Retimer

首先我们先对高速系统设计有些基本的认识,一般而言高速SerDes系统(例如PCIe、112G/224G)都是所谓点对点的拓璞架构(Point-Point Topology),这两点可以是GPU-ASIC、CPU-GPU、CPU-NVMe等等。 有别于很多低速逻辑讯号在用的Fly-By或是星状拓朴,这种架构的SI一定是最好的,因为它不会出现很夸张的开路残段Open Stub(还记得我们在讯号完整性不好吗? 3大案例告诉您开路谐振如何搅局高速讯号设计有谈到,开路残段是损害SI的杀手)。

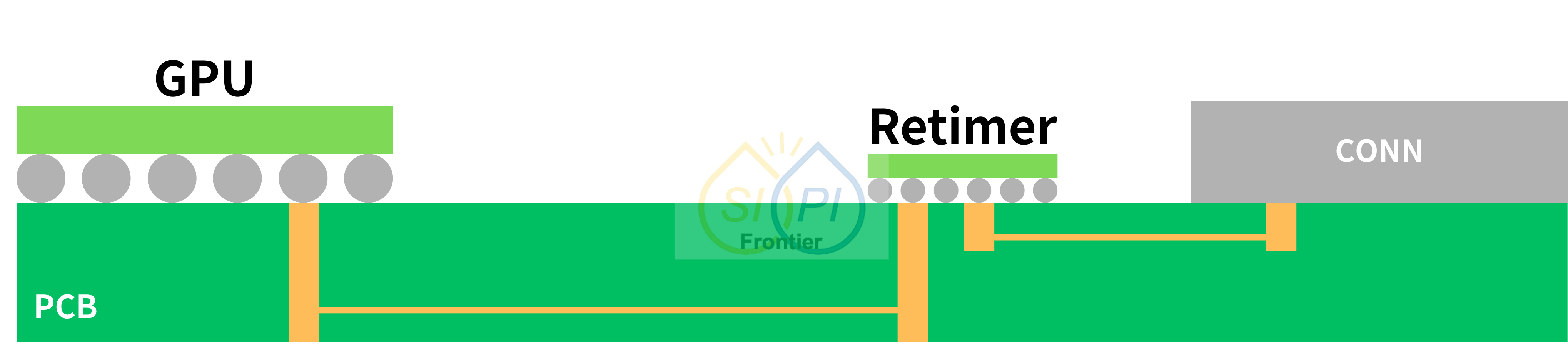

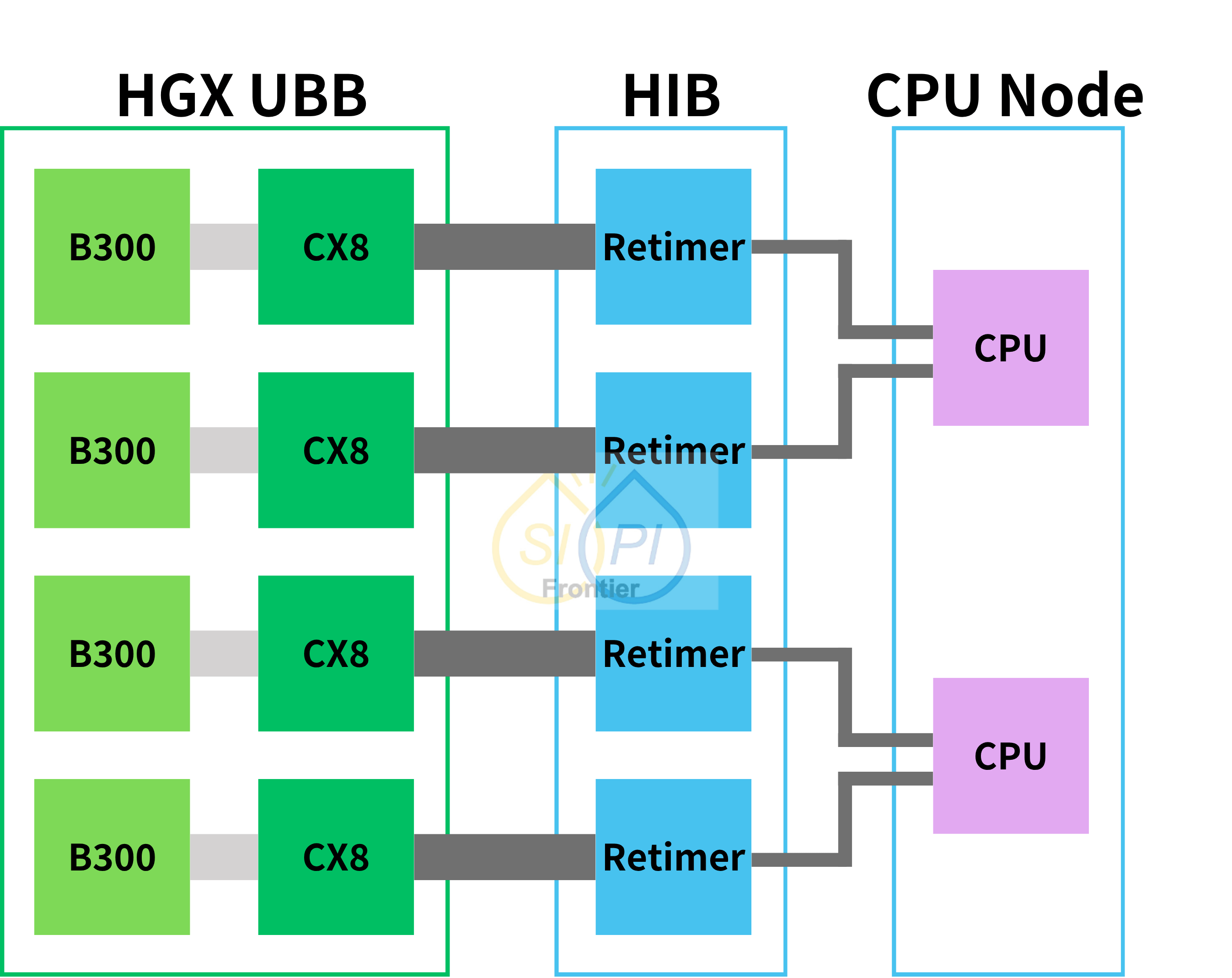

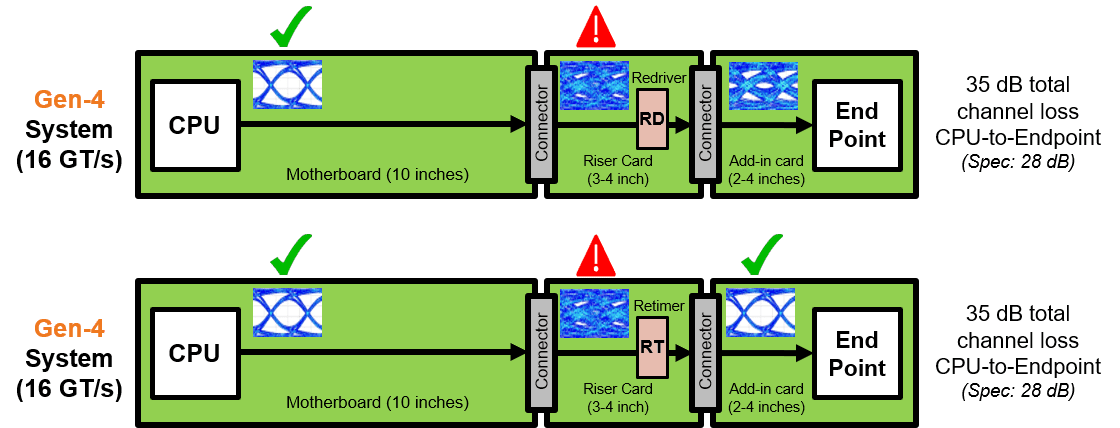

就像下面这张PCIe架构图,点对点拓朴可以是GPU-PCIe Switch、GPU-Retimer、Retimer-PCIe Switch、CPU-Retimer,族繁不及备载。

继续以PCIe Gen5为例,点对点拓朴的两点间损耗必须在16GHz时小于36dB:

如果两个芯片之间有以下的情况,则损耗很可能会爆表导致SI有问题:

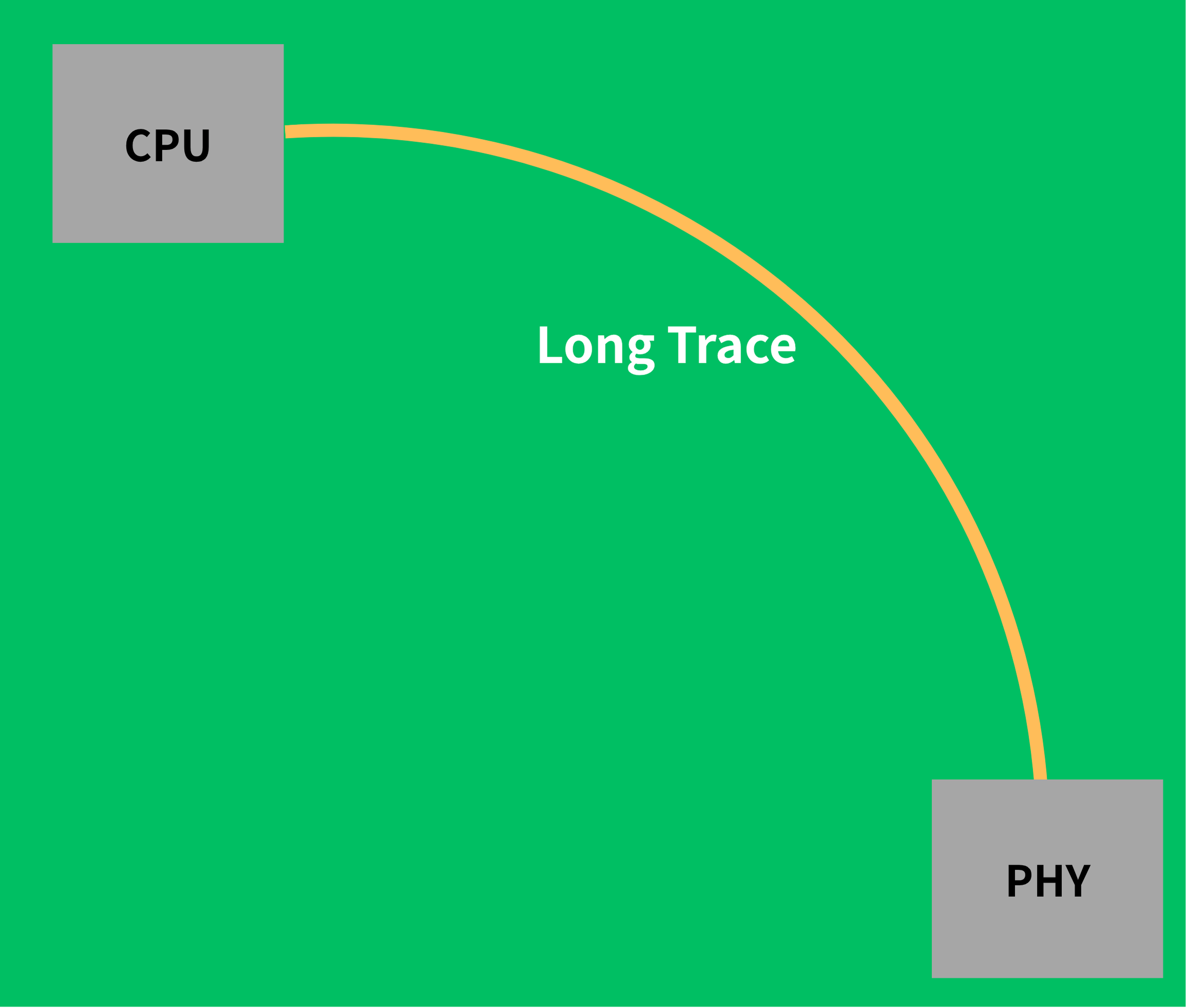

- 某芯片被放在PCB的角落,走线要走非常远才能到达:

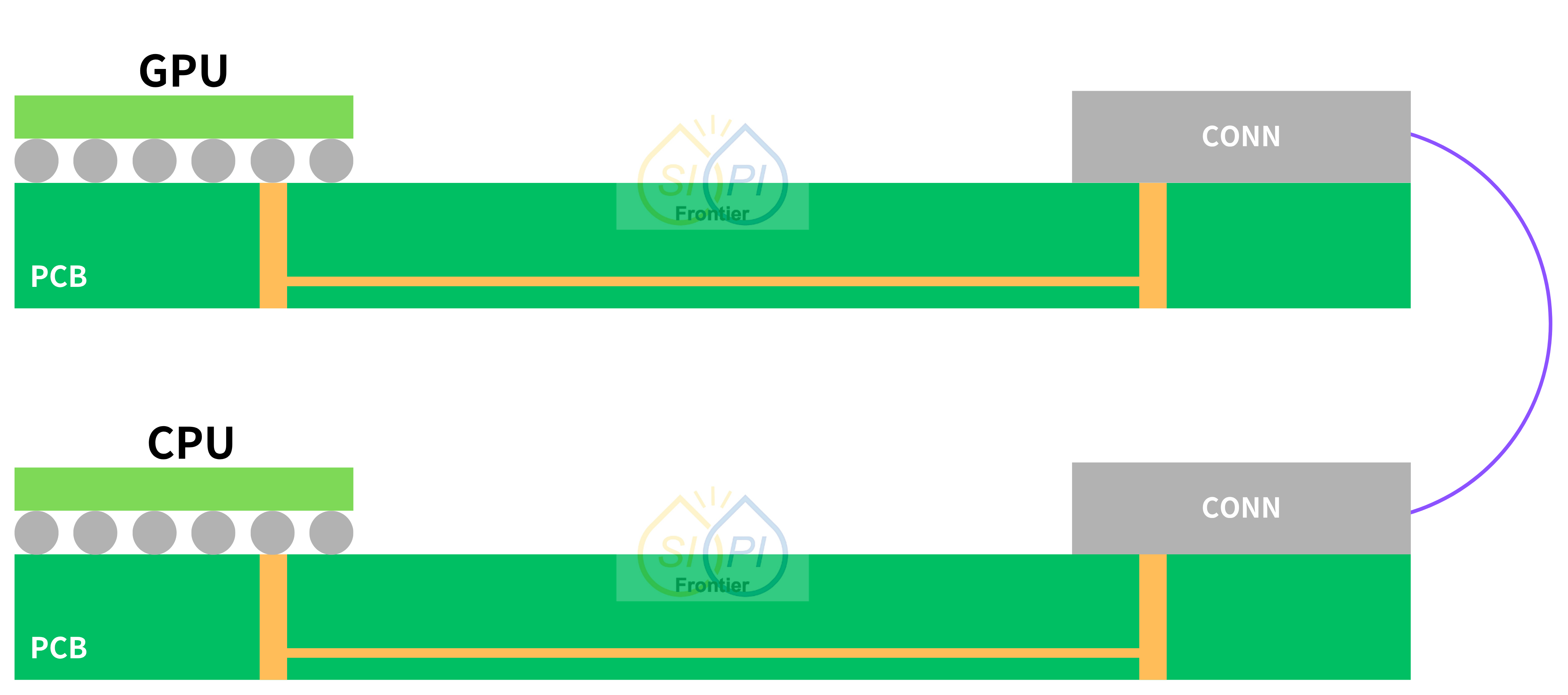

- 使用额外的连接器,芯片被分开在两张甚至三张板子上:

- 芯片散落在不同机柜,中间连接距离过远:

当有这些情况发生,我们就会需要一个信号的中继站,将已经被衰减到很小的信号先整流,再放大,重新发送出去,而这个东西就叫做Redriver(信号中继器)或是Retimer(重定时器)。

Redriver和Retimer在高速通道的放置上又有分几种型式:

- 与主芯片放在同张板子上:

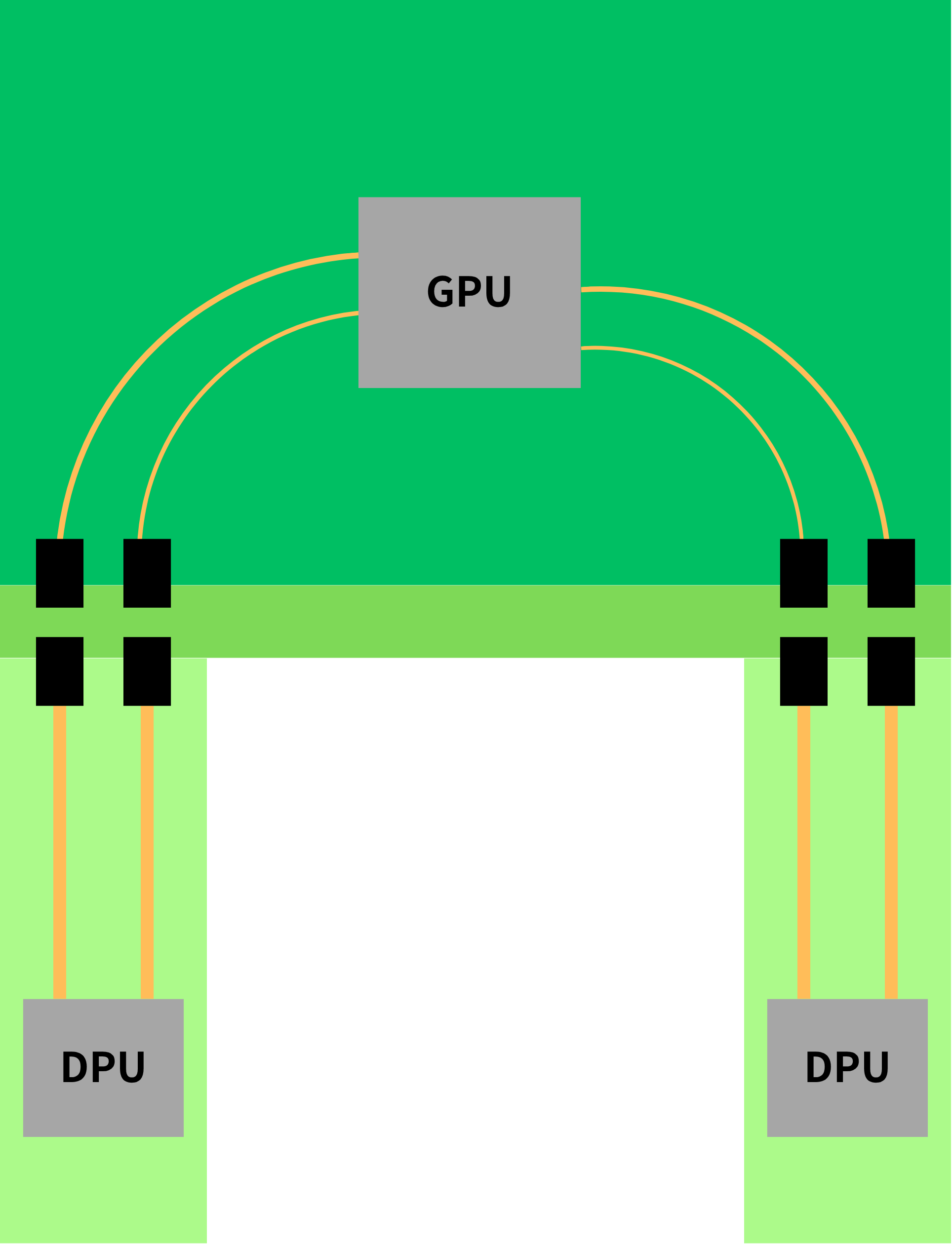

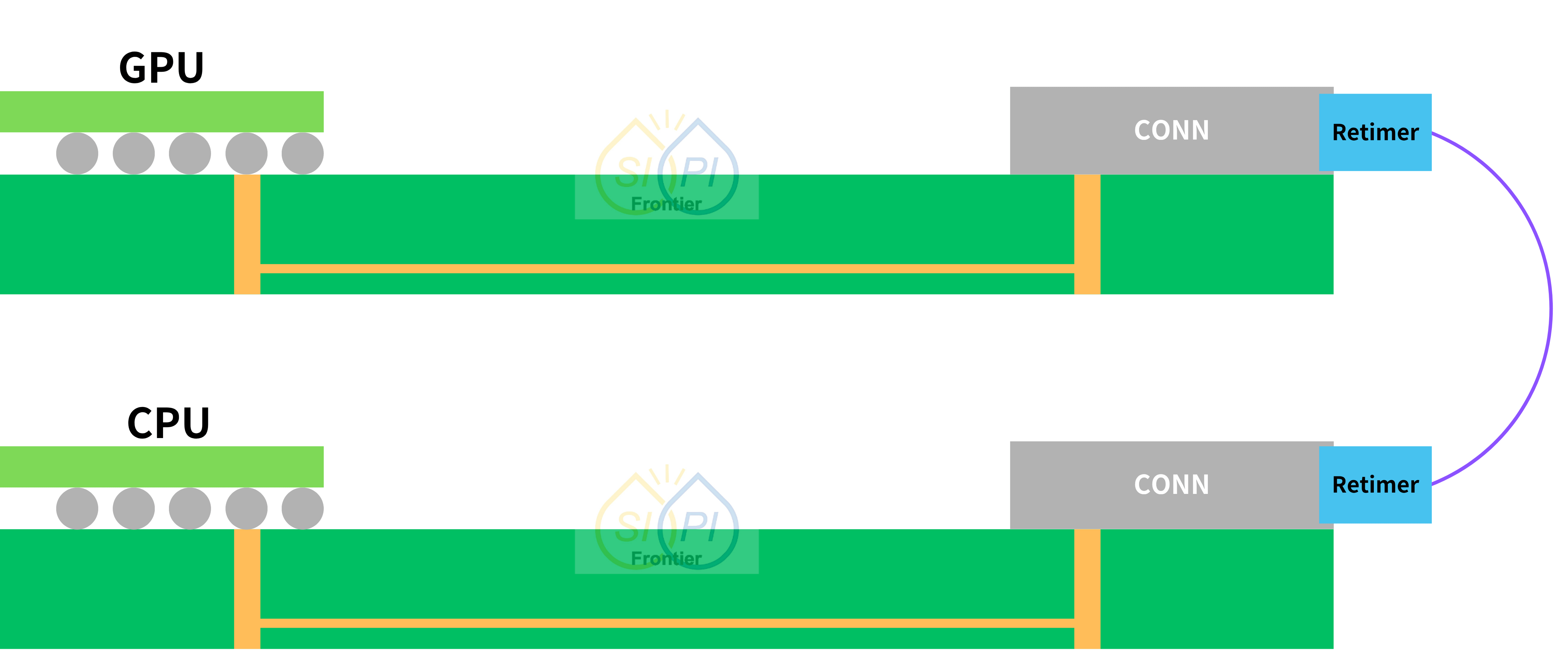

- 一张PCIe Board,上面的主要芯片都是Retimer(或是PCIe Switch),用来作为整个系统数据连接用,例如此图里的HIB(Host-Interface-Board),这板子在很多8卡的系统架构里很常用,上面放4-8颗的PCIe Retimer/Switch,以作讯号整流放大之用, 并桥接至远端的CPU至另一个机壳里的CPU:

- AEC:将Retimer整合进Cable里头,也就是所谓的主动式铜缆。 由于被动式铜缆在800G的数据传输速率下只能拉2米长,如果要再更长,就得使用这种AEC,目前看到最长可以到7米。

Redriver & Retimer – 信号的中继站

高速讯号的中继站主要有两种,Redriver and Retimer,有些人又会特别提Repeater,这里可能得来澄清一下,我们觉得这算是产业的混用,因为Repeater其实在很多地方都有用到,尤其是电信领域,要把微小的RF能量再放大打出去,能做到这种行为的被称作Repeater。 而在高速SI领域,Repeater可以切分成Redriver and Retimer。

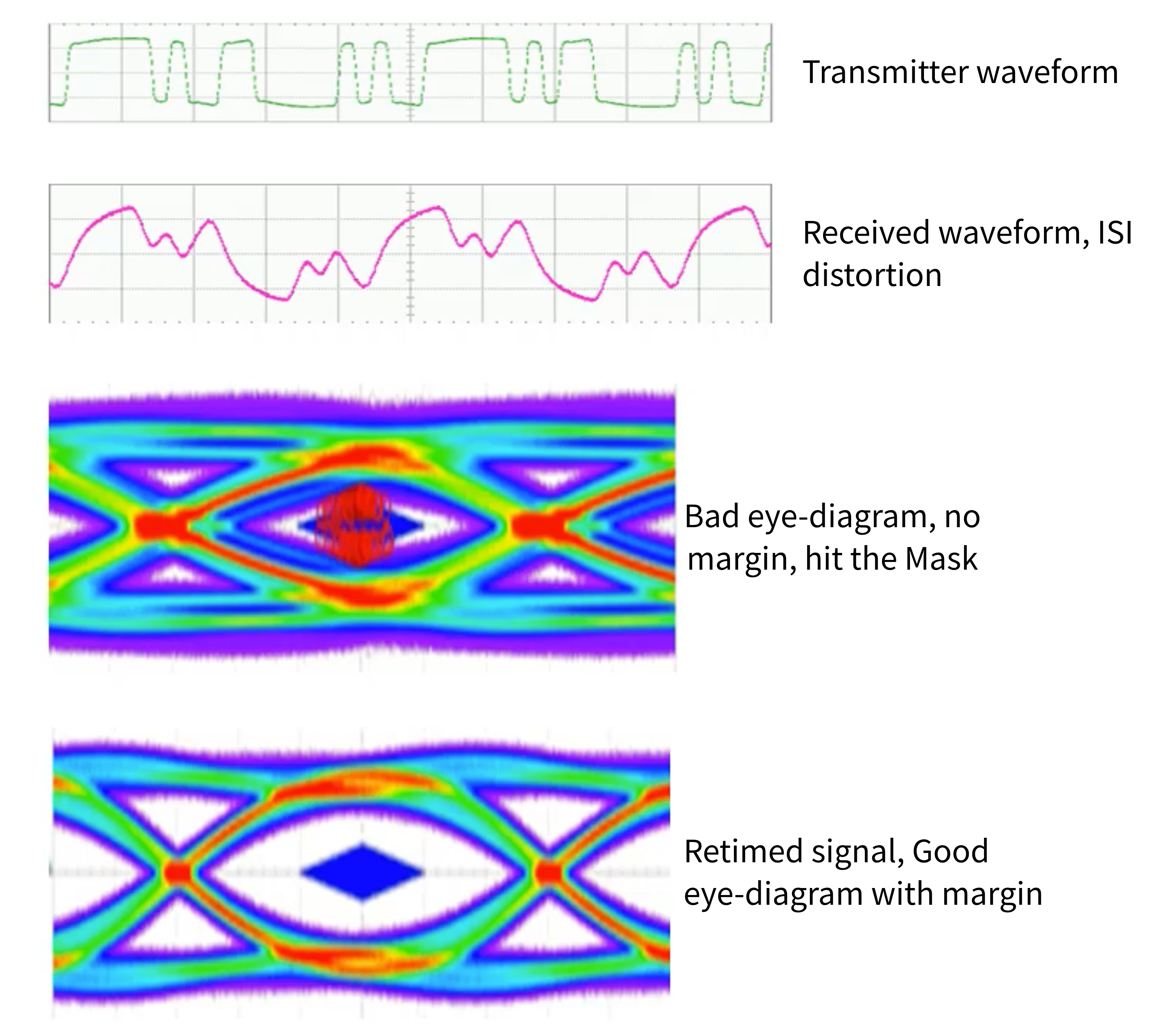

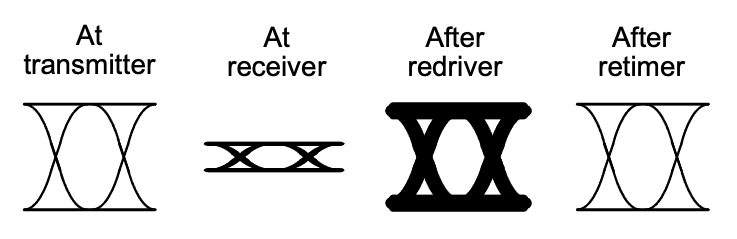

Retimer可以将能量被衰减到很小的讯号做还原:

Redriver

Redriver可以通过CTLE、Gain Amplifier、TX FIR/FFE将高速信号本身先进行整流再放大,这样即使损耗超过规格,还是可以将其救回来。

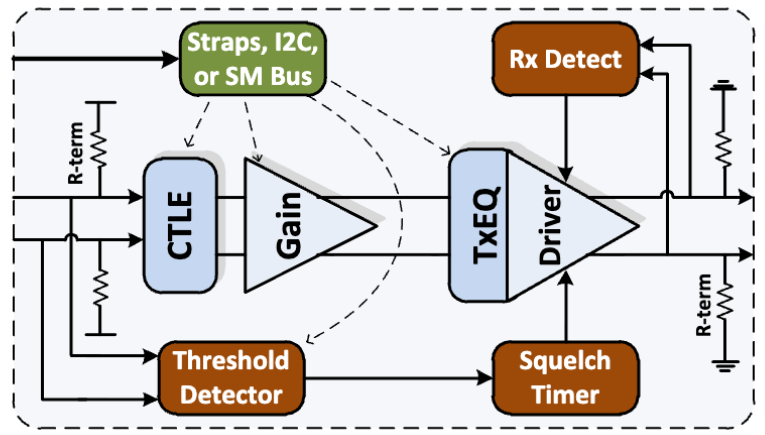

Redriver的架构:

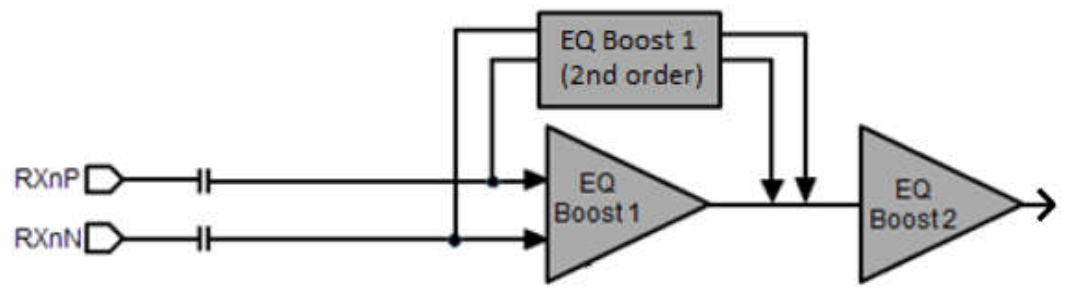

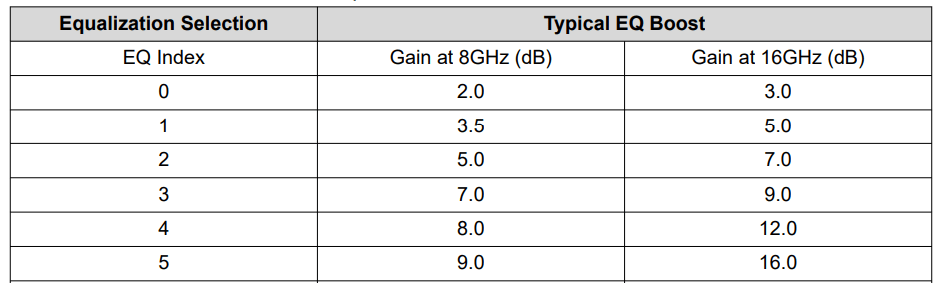

Redriver架构的核心非CTLE + Gain Amplifier莫属,有些Redriver会称其为Boost Amplifier,通过不同的Boost能力,这个Boost Amplifier可以针对不同损耗做讯号的补偿。

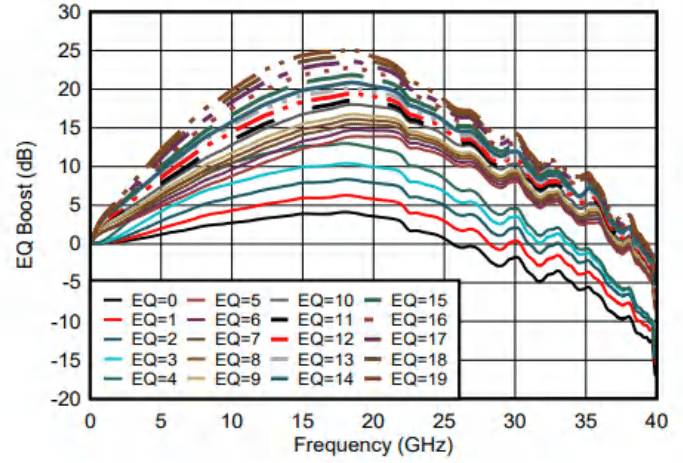

不同EQ Level,每一个都有其对应的最佳补偿损耗:

Boost Amplifier架构:

通常Datasheet会给对应的损耗表:

不过Redriver还是有几个缺点需要注意:

- 无法当成断点:其实Redriver比较像是主动式的Pass-Thru组件,并没有相对应的反馈机制,主芯片给我什么,我就照着这个讯号响应给出对应的输出。 并无法参与协议,无法当作一个断点,也没有内建功能可以判断Redriver的接收信号特性(例如Eye monitor、Pattern generator等等),所以当使用Redriver的通道有问题时,无法将通道切成前后Debug,在问题排除上会比较困难。

- 劣化系统Jitter:如果主芯片的讯号输出较差,或是通道设计较为紧张,导致有较大的Jitter的话,Redriver本身无法重置Jitter,甚至由于讯号放大的特性,还会放大Jitter。 如果Redriver本身贡献的热噪声过大,还会将其叠加至讯号上,使Jitter更为严峻。

- 没有DFE:Redriver的架构并不会有DFE(Decision-Feedback Equalizer)的出现,使得一些反射与Crosstalk无法被消除。

- 无法消除Input讯号的Skew:高速差动对的PN skew的要求是非常高的,通常走线越长,Skew就越大,会使用到Redriver/Retimer的高速通道一定是长通道,PN Skew会很难控制,Redriver并没有补偿机制,甚至其封装的不对称,还可能恶化PN Skew。

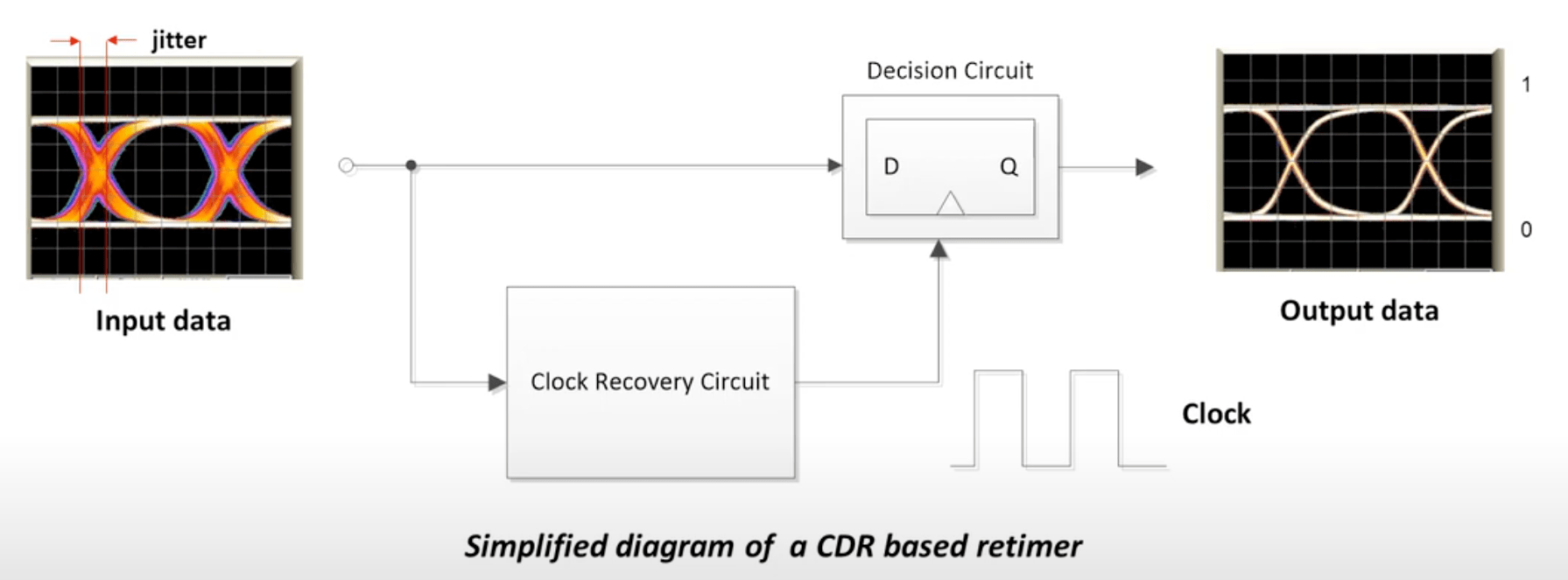

- Clock and Data Recovery(CDR):任何的Data都需要Clock当作基准将藏在讯号里的资料正确提取出来,如果芯片本身具有CDR功能,可以将已经变得很脏的、Jitter很大的Clock给恢复,由于有干净的Clock,因此Data可以更准确被采样,眼图会更干净。 而Redriver... 没有!

过补偿Over-Equalization:不是说把Redriver的档次调到最高就是最好,因为不同的EQ对应的补偿损耗是不一样的,如果没调整好,那会有过补偿的问题,有可能眼睛变两颗,也有可能会有振幅过大的问题

Retimer

可以解决以上列举出的所有Redriver使用上的问题,具有CDR、可以当作讯号的断点、可以侦测眼图、具有DFE,由于种种优势,在PCIe Gen5以上的资料速度,已经很少看到Redriver!

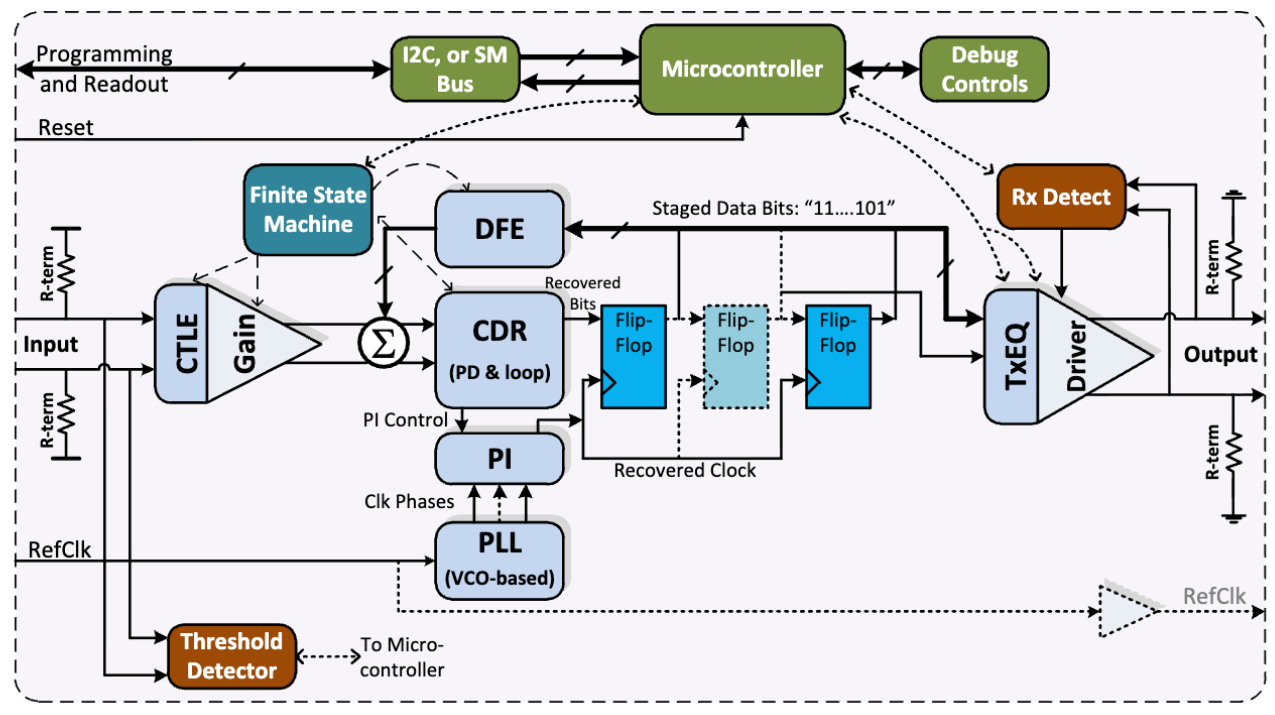

Retimer的架构,有没有发现比Redriver复杂多了,还有关键的CDR:

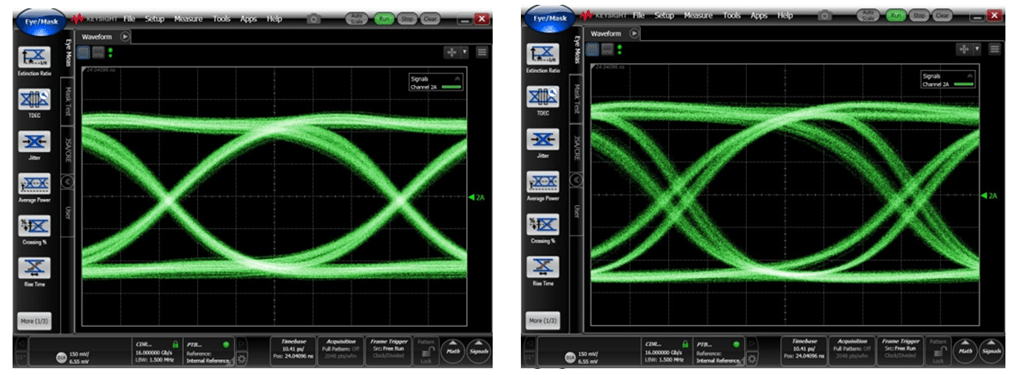

Retimer的眼睛就是特别清晰漂亮:

使用Redriver and Retimer的Risk and Challenge

虽然Redriver和Retimer有延长通道长度的优势,可以保证信号完整性在一个优秀的水平,可是在使用上还是有很多的风险与挑战需要考量:

- Cost:多了这些组件,一定会多出一些成本,不单单只有Redriver and Retimer的成本,你总是要上电,这些电源零件也是钱~

- Power:尤其是Retimer,功耗不算小喔,目前有看到单颗高档的料25W的,对于电源设计与零件选用上要相当小心

- Placement:使用这类型元件,还有一个问题是要摆哪里? 靠近主芯片还是靠近尾巴? 这就有赖完整的信号完整性分析,你摆得太靠近主芯片,那就很浪费Retimer在CTLE、DFE上的优势,摆得太远,说不定连输入讯号都侦测不好,更不用谈讯号要补偿。

- Latency:以前我们提过,AI对于低延迟的要求非常严格,Retimer本身会增加不少延迟,这点也是架构设计者会首要考量的地方。

种种设计上的挑战,所以站在系统考量,Retimer还是能不用就不用,当然现在的AI数据中心架构,很多会仰赖Retimer或是PCIe Switch去布置通道链,那又是另一个课题了~~

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)