解决Vivado:MMCM/PLL CLK_OUT所需频率值无法达到

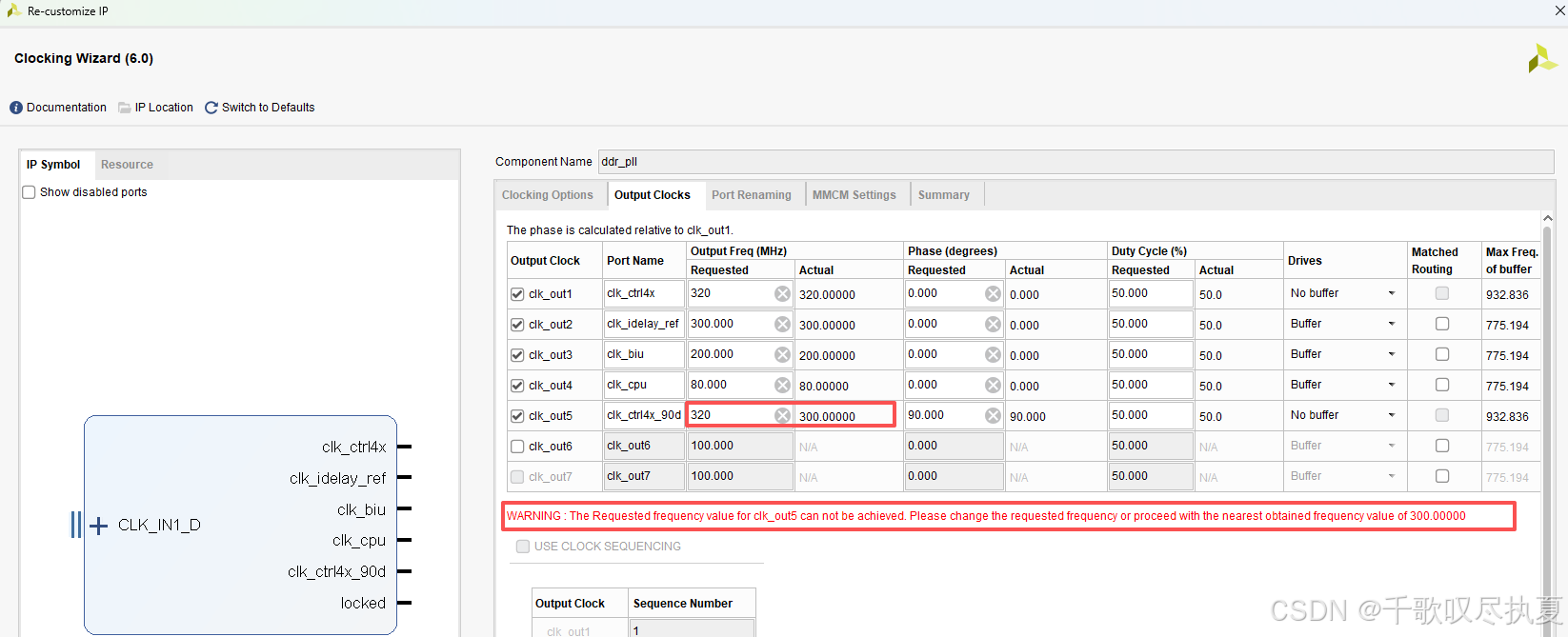

WARNING : The Requested frequency value for clk_out5 can not be achieved.Please change the requested freguency or proceed with the nearest obtained freguency value of 300.00000使用clk_out1和5改成400M反而可以,

问题:

WARNING : The Requested frequency value for clk_out5 can not be achieved.Please change the requested freguency or proceed with the nearest obtained freguency value of 300.00000

使用clk_out1和5改成400M反而可以,320M,以及250M都出现这种情况。

解决过程:

1、想着调整一下,几个不同频率的输出顺序,能不能搞定,结果发现,没用;(还看了一下XDC时序约束,跟XDC关系也不大)

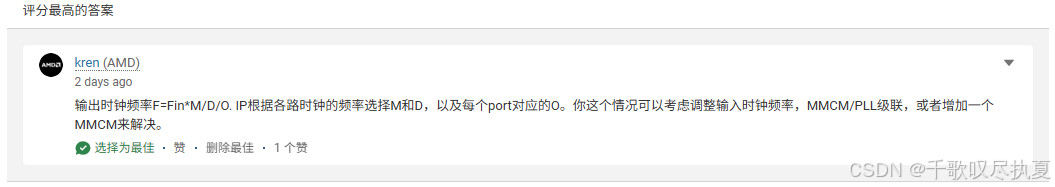

2、问了一下,官方FAE,得到如下回复:

输出时钟频率F=Fin*M/D/O. IP根据各路时钟的频率选择M和D,以及每个port对应的O。你这个情况可以考虑调整输入时钟频率,MMCM/PLL级联,或者增加一个MMCM来解决。

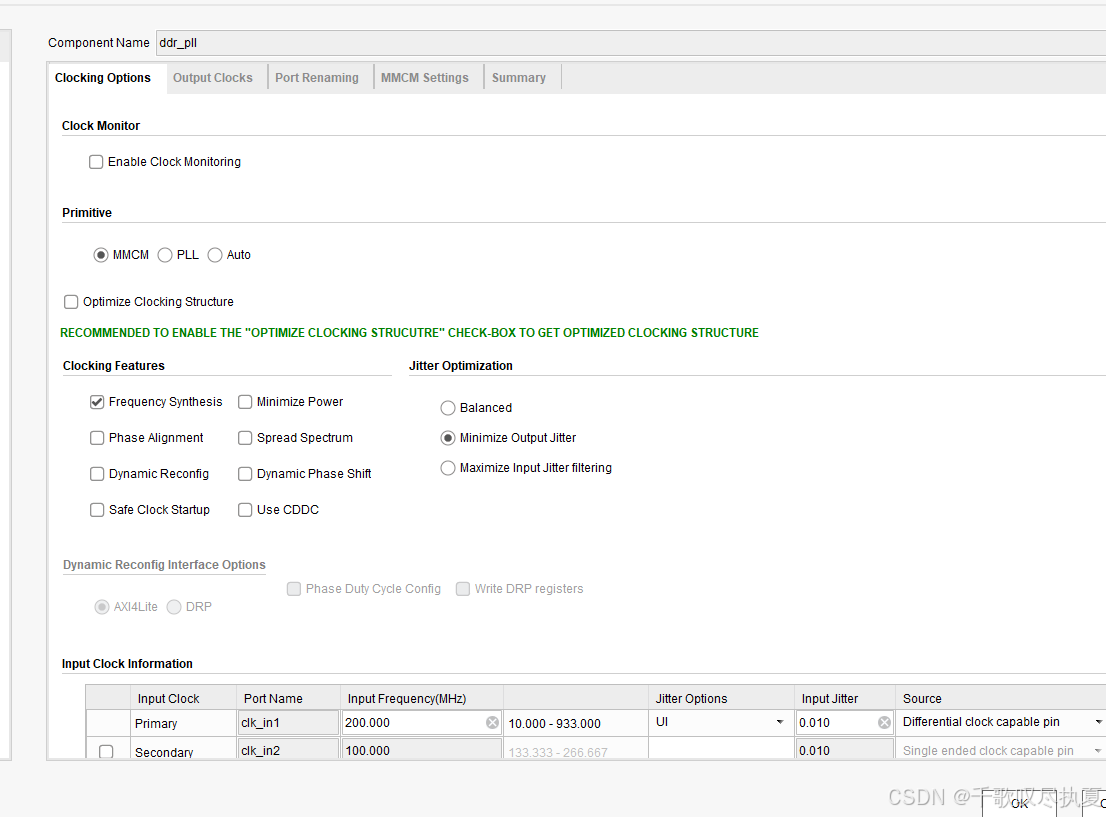

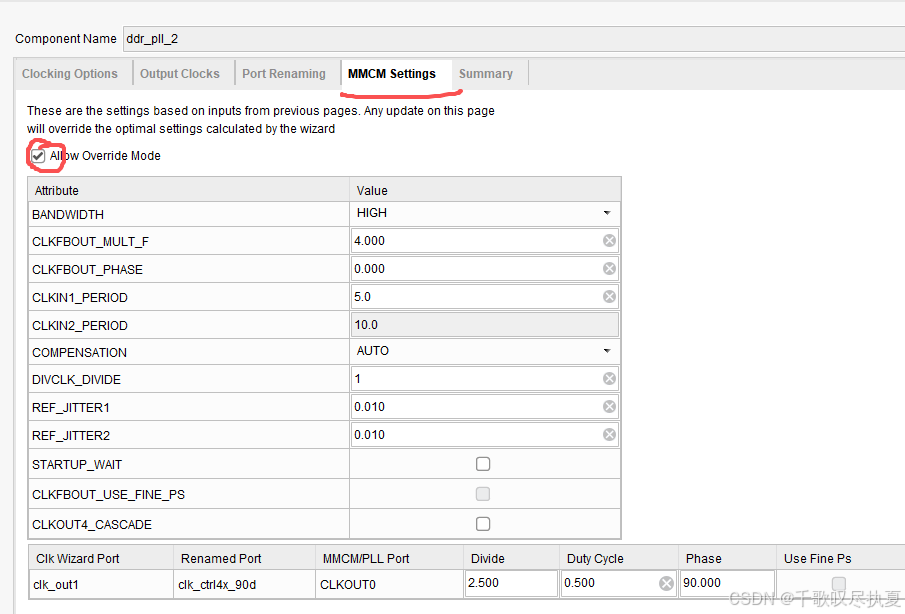

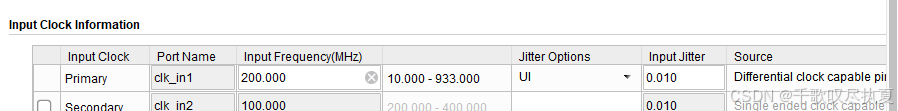

第一个方式,没有尝试,直接往第二个快的去验证,如果想试第一种的,除了调用原语,还可以在UI实现:

MMCM Settings一项,有参数可以调。

解决:

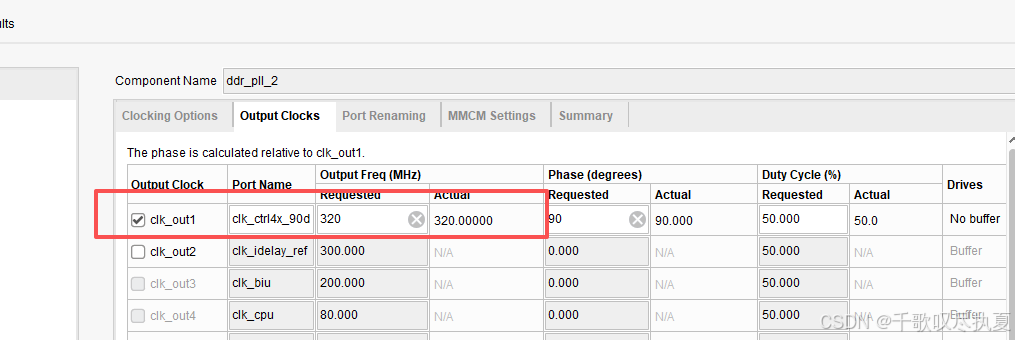

用第二种,再例化一个MMCM IP;

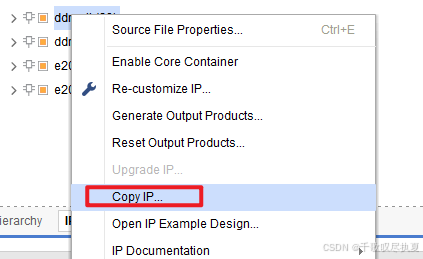

觉得麻烦的,可以直接在原IP右键选:Copy IP就好了,然后删掉前面4个,保留那个无法输出的;

这里,大家可能有疑问,新的MMCM/PLL用什么输入?答案:还是你原来IP的差分时钟输入就行了。

然后可能有其他问题,比如器件比较低级,没有那么多MMCM(理论上应该不会有这个问题),那你就修整参数吧。

意外发现:

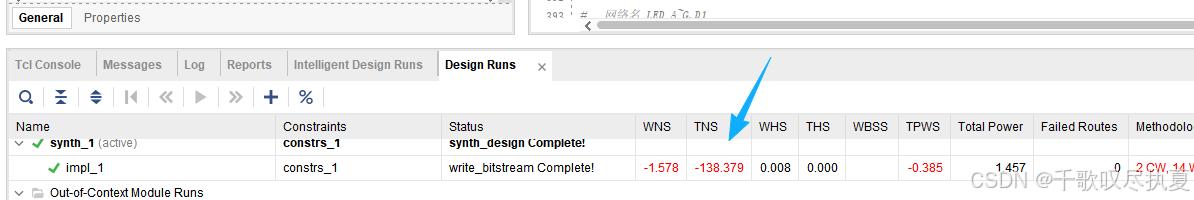

增加一个MMCM发现还能缓解时序紧张,并且不影响功能;

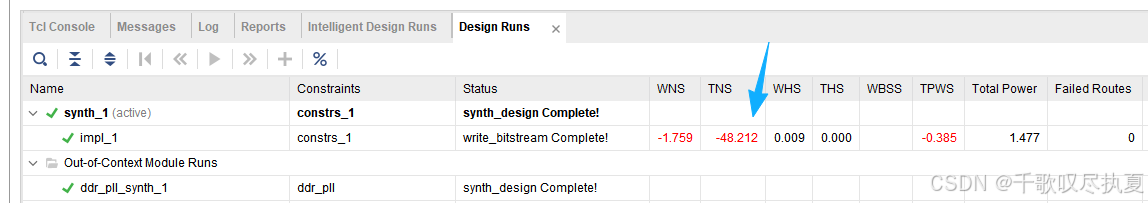

原本时序违例TNS有-138ns:

增加MMCM后,只有-48ns了。

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)