FPGA日益增益的依赖与商业应用

FPGA在五大领域的创新应用 本文系统阐述了现场可编程门阵列(FPGA)在航空航天、超级计算、视频处理、数据加密和网络安全五大领域的关键应用。在航空航天领域,FPGA作为高可靠控制核心,实现毫秒级姿态控制和星载数据处理;在超级计算中,其并行架构显著提升科学计算和AI训练效率;视频处理方面,FPGA提供4K/8K实时编解码解决方案;数据加密领域实现400Gbps高吞吐量加密;网络安全方面构建100G

目录

现场可编程门阵列(FPGA)是一种基于可编程逻辑单元(LUT)、触发器、数字信号处理(DSP)模块及存储单元的半定制集成电路,其核心优势在于硬件可重构性——可通过硬件描述语言(HDL,如 Verilog、VHDL)或高级综合工具(HLS)灵活定义电路功能,兼顾专用集成电路(ASIC)的高并行性、低延迟优势与通用处理器(CPU)的灵活性,因此在对实时性、并行度、可靠性要求严苛的场景中被广泛应用。

1.航空航天用FPGA——极端环境下高可靠控制核心

1.1 核心控制与导航系统

航天器(卫星、火箭、探测器)的姿态控制、轨道修正、导航解算等任务需实时响应(毫秒级甚至微秒级延迟),且不能依赖易受干扰的软件逻辑。FPGA可通过硬件电路直接实现以下功能:

姿态传感器数据融合:将陀螺仪、加速度计、磁强计的模拟信号经FPGA内置的ADC模块转换为数字信号,通过硬件化的卡尔曼滤波算法(避免软件迭代延迟)实时解算航天器姿态角(滚转、俯仰、偏航),控制推进器或动量轮调整姿态;

轨道导航解算:对于依赖星载GPS/北斗的航天器,FPGA可硬件加速伪距计算、载波相位跟踪等导航算法,确保轨道定位误差小于1米;对于深空探测器(如火星车),FPGA还可实现自主导航的图像匹配(如基于SIFT算法的地形匹配),避免地面控制信号延迟导致的风险。

典型案例:美国NASA的“毅力号”火星车采用Xilinx(现AMD)的XQ7Z020抗辐射FPGA,用于实时处理火星表面的地形图像、控制机械臂运动,其抗单粒子翻转(SEU)能力通过硬件冗余设计(如三模冗余TMR)提升,确保在强辐射环境下无故障运行。

1.2 星载数据处理与传输

卫星(尤其是遥感卫星、通信卫星)需处理海量数据:遥感卫星单日可产生数十 TB的地表图像数据,通信卫星需实时转发多频段射频信号,传统CPU难以满足“高吞吐 + 低延迟”需求。FPGA 的并行架构可实现:

数据压缩与滤波:通过硬件化的JPEG2000或CCSDS(空间数据系统咨询委员会)压缩标准,对遥感图像进行实时压缩(压缩比可达10:1,且保真度高),减少星地传输带宽占用;同时,FPGA 可硬件实现自适应滤波算法,滤除宇宙噪声对图像信号的干扰;

射频信号处理:在通信卫星中,FPGA可直接集成数字下变频器(DDC)、数字上变频器(DUC)功能,将射频信号转换为数字基带信号后,通过硬件逻辑完成信号调制解调(如QPSK、8PSK),避免使用专用射频芯片导致的体积与功耗增加。

航空航天用FPGA多为抗辐射加固型号(如Xilinx的Q系列、Microchip的RTG4系列),通过工艺优化(如SOI绝缘体上硅工艺)、电路设计(TMR冗余、错误检测与纠正EDAC)降低辐射导致的电路翻转风险;同时采用低功耗工艺(如28nm、40nm),单芯片功耗可低至1W以下,适配航天器能源限制。

1.3 测试与验证环节

在航空航天设备研发阶段,FPGA可作为 “硬件原型验证平台”:通过搭建与目标芯片(如专用星载处理器)功能一致的FPGA原型,提前验证控制算法、数据处理逻辑的正确性,避免直接流片 ASIC的高成本与高风险。例如,欧洲航天局(ESA)在“欧几里得”空间望远镜的研发中,采用 Altera(现Intel)的Stratix系列FPGA搭建原型,验证了光谱仪数据处理电路的可靠性,缩短了研发周期约30%。

2.超级计算用FPGA——通用计算的“并行加速引擎”

超级计算的核心需求是峰值算力与能效比—— 传统CPU基于冯・诺依曼架构,串行执行指令,在密集型计算(如矩阵运算、流体力学模拟)中能效比低;GPU虽擅长并行计算,但通用性受限于SIMD(单指令多数据)架构。FPGA凭借 “可定制并行电路” 特性,成为超级计算系统的 “异构加速单元”,可针对特定算法优化硬件结构,实现 “算力按需分配”。

2.1 科学计算加速

在气象预测、量子化学、天体物理等领域,超级计算机需处理大规模数值计算(如有限元分析、分子动力学模拟),FPGA可通过以下方式加速:

硬件化计算核设计:针对科学计算中的核心算子(如矩阵乘法、FFT快速傅里叶变换),设计专用硬件计算核 —— 例如,将矩阵乘法拆解为多个并行的乘法 - 累加(MAC)单元,通过流水线设计(每个时钟周期输出一个计算结果),使算力密度(每瓦算力)达到CPU的5~10倍。以FFT为例,FPGA实现的64点FFT延迟可低至100ns,而CPU需约1μs;

异构计算架构整合:超级计算系统通常采用“CPU+FPGA”架构(如美国橡树岭国家实验室的 “Summit”超算部分节点集成Xilinx FPGA),CPU负责任务调度、逻辑控制,FPGA专注于密集型计算,通过PCIe 4.0/5.0接口实现低延迟数据交互(数据传输带宽可达32GB/s)。

典型案例:中国“天河二号”超算曾引入Altera FPGA加速模块,用于流体力学模拟中的Lattice Boltzmann方法计算,将单节点计算效率提升40%,同时降低能耗25%;美国能源部的“CORAL”超算计划中,FPGA被用于加速量子蒙特卡洛模拟,助力材料科学领域的新型电池研发。

2.2 大数据与AI训练加速

随着超级计算与AI的融合,FPGA在大规模深度学习训练中展现出独特优势:

灵活适配多模型:与GPU固定的Tensor Core不同,FPGA可根据模型结构(如 CNN、Transformer)定制计算单元 —— 例如,针对Transformer的自注意力机制,设计专用的硬件注意力核,减少数据在存储与计算单元间的搬运延迟;

低精度计算优化:在AI训练中,可通过FPGA实现低精度量化(如FP16、BF16、INT8),在保证模型精度损失小于1%的前提下,将计算吞吐量提升2~4倍。例如,Xilinx的Alveo U280 FPGA支持BF16精度的矩阵乘法,吞吐量可达19.2 TFLOPS,能效比(TFLOPS/W)是GPU的1.5倍。

2.3 技术优势

超级计算用FPGA的核心竞争力在于高能效比(通常为10~20TFLOPS/W,而GPU约为5~10 TFLOPS/W,CPU仅为1~2 TFLOPS/W),可降低超算中心的电力消耗与散热成本;同时,FPGA 支持“模块化扩展”—— 通过多芯片互联(如Xilinx的Super Logic Region技术)构建大规模计算集群,按需扩展算力,避免 GPU 集群的高成本投入。

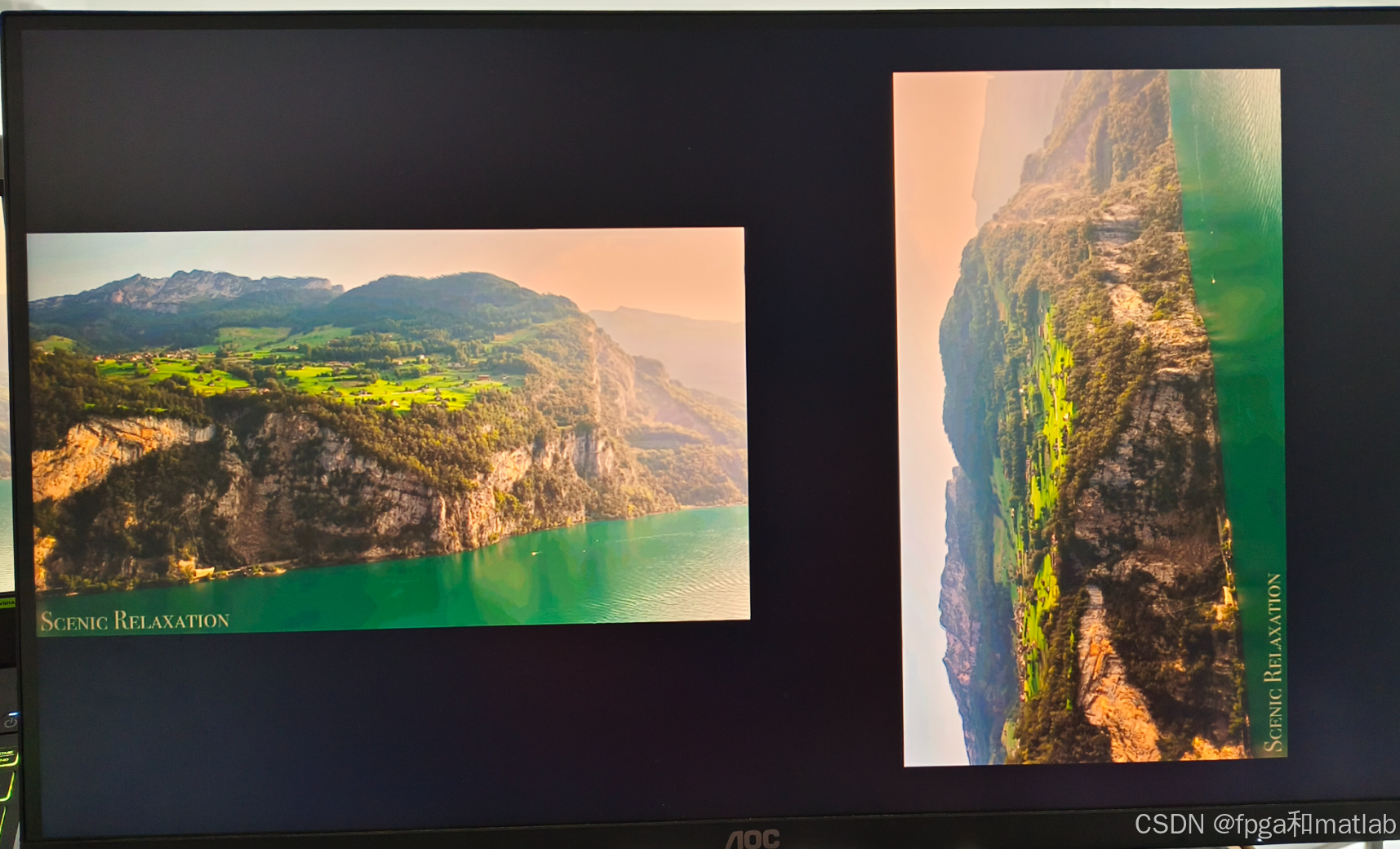

3.视频用FPGA——高分辨率、低延迟的实时处理中枢

视频处理领域(如安防监控、广播电视、自动驾驶车载影像)对“实时性”(如4K/8K视频需60fps帧率,单帧处理延迟需小于1ms)、“并行性”(如同时处理多路视频流)要求严苛。FPGA的硬件并行架构可直接处理视频像素流,避免软件处理的指令排队延迟,成为视频处理的核心载体。

3.1 视频编解码

4K/8K超高清视频的编解码(如H.265/HEVC、AV1标准)需处理海量像素数据(4K视频单帧约830万像素,8K约3300万像素),FPGA可通过以下方式实现实时编解码:

流水线化编解码核:将编解码流程(帧内预测、变换编码、熵编码)拆解为多个硬件流水线阶段,每个阶段并行处理不同帧的像素数据 —— 例如,当第1帧进行熵编码时,第2帧可同时进行变换编码,第3帧进行帧内预测,实现“帧级并行”;

多标准兼容:FPGA可通过重构硬件逻辑,同时支持H.264、H.265、AV1等多编码标准,而专用编解码芯片(如 ASIC)仅支持固定标准,灵活性不足。

典型应用:安防监控系统中,采用 FPGA 的视频服务器可同时处理32路1080P视频流的H.265编码,单路编码延迟小于500μs,且功耗仅为CPU方案的1/3;广播电视领域,FPGA用于8K超高清视频的实时转码,确保直播信号无延迟传输。

3.2 视频图像增强与分析

在自动驾驶、工业视觉等场景中,视频流需实时进行图像增强(如降噪、锐化)与内容分析,FPGA可实现 “处理-分析一体化”:

硬件化图像增强算法:针对车载摄像头的低光噪声、工业相机的运动模糊,FPGA可硬件实现自适应高斯滤波、运动补偿算法,将图像信噪比(SNR)提升20dB以上,处理延迟小于100μs;

实时目标检测:将深度学习目标检测算法(如YOLOv5)的卷积层、池化层通过HLS工具转化为硬件电路,实现对视频流中行人、车辆的实时检测(检测帧率可达60fps,延迟小于1ms),满足自动驾驶的 “毫秒级决策” 需求。

技术特点:视频用FPGA通常集成高速视频接口(如MIPI CSI-2、HDMI 2.1、SDI),可直接对接摄像头或显示设备,减少数据在接口转换中的延迟;同时内置大容量Block RAM,用于缓存视频帧数据,避免外部存储访问的延迟。

4.高吞吐量加密用FPGA——数据安全的“硬件屏障”

随着5G、云计算、金融交易的发展,数据传输与存储的 “高吞吐量加密” 需求激增(如金融核心系统需处理每秒数十万笔交易的加密,数据中心需加密TB级流量)。传统软件加密(如CPU运行AES、RSA算法)受限于串行指令执行,吞吐量难以突破10Gbps;FPGA可通过硬件并行架构实现 “指令级+数据级” 双重并行,成为高吞吐量加密的首选方案。

4.1 对称加密加速(AES、SM4)

对称加密算法(如AES-256、国密SM4)运算逻辑固定,适合FPGA硬件实现:

并行加密核阵列:在FPGA中搭建多个独立的AES加密核(如128个),每个加密核处理一路数据流,同时支持ECB、CBC、GCM等多种加密模式。以AES-256-GCM为例,单个Xilinx Alveo U250 FPGA可实现400Gbps的加密吞吐量,是CPU方案(约10Gbps)的40倍;

低延迟优化:通过流水线设计,将AES的轮变换(如SubBytes、ShiftRows、MixColumns)拆解为硬件流水线,每个时钟周期完成一轮变换,AES-256的加密延迟可低至10ns,满足金融交易的 “微秒级响应” 需求。

4.2 非对称加密加速(RSA、ECC)

非对称加密算法(如RSA-2048、ECC P-256)核心是大整数模幂运算,计算复杂度高,FPGA可通过专用硬件模块加速:

大整数运算单元:设计64位或128位的硬件乘法器、加法器,通过Booth编码优化乘法运算,将 RSA-2048的模幂运算时间缩短至1μs以内(CPU需约100μs);

椭圆曲线加密(ECC)优化:针对ECC的有限域运算(如GF(p)、GF(2^m)),设计专用硬件运算核,使ECC P-256的签名生成吞吐量达到10万次/秒,满足物联网设备的身份认证需求。

4.3 典型应用场景

金融交易加密:银行核心系统采用FPGA实现AES-256加密,确保每秒50万笔转账交易的数据包实时加密,同时通过硬件化的SHA-256哈希算法生成交易摘要,防止数据篡改;

数据中心流量加密:云服务商(如AWS、阿里云)在数据中心网关部署FPGA,实现400Gbps的 TLS 1.3加密卸载(将CPU从加密任务中解放),提升服务器的业务处理能力;

国密标准适配:中国金融、政务领域需符合国密标准(SM4、SM2、SM3),FPGA可通过重构硬件逻辑快速适配国密算法,而ASIC需重新流片,成本高、周期长。

5.入侵检测及防范用FPGA——网络安全的“实时防御壁垒”

网络入侵检测与防范(IDS/IPS)系统需实时分析网络流量(如100Gbps骨干网流量),识别异常数据包(如DDoS攻击、SQL注入、恶意代码),传统软件IDS/IPS受限于CPU处理能力,在高流量场景下易出现“丢包” 或 “检测延迟”。FPGA 凭借“线速处理”(处理速率与网络带宽匹配)能力,成为IDS/IPS的核心加速单元。

5.1 网络流量实时捕获与解析

FPGA可直接对接高速网络接口(如100Gbps Ethernet、400Gbps InfiniBand),实现“零丢包”流量捕获与解析:

硬件化流量过滤:通过FPGA的CAM(内容可寻址存储器)或TCAM(三态内容可寻址存储器),实现基于IP地址、端口号、协议类型的快速过滤,仅将疑似攻击的数据包发送至CPU进一步分析,减少CPU负载;

深度包解析(DPI):硬件化解析TCP/IP协议栈(从L2到L7层),提取数据包的应用层数据(如 HTTP请求、DNS查询),识别异常字段(如SQL注入的“OR 1=1”语句),解析延迟小于100ns,确保100Gbps流量无丢包。

5.2 攻击模式匹配与检测

IDS/IPS的核心是“攻击特征匹配”(如基于Snort规则库),FPGA可通过硬件化的模式匹配算法实现高速检测:

并行字符串匹配:采用硬件化的Aho-Corasick多模式匹配算法,在FPGA中搭建并行匹配引擎,同时匹配数千条攻击特征(如DDoS攻击的特征码、恶意软件的签名)。例如,针对1000条Snort规则,FPGA的匹配吞吐量可达100Gbps,是CPU方案的5~10倍;

异常行为检测:通过硬件化的统计分析算法(如滑动窗口计数、熵值计算),实时监测网络流量的异常波动(如某IP的数据包发送频率突增10倍,可能是DDoS攻击),检测延迟小于1ms,可提前触发防御策略。

5.3 实时防御响应

FPGA不仅能检测入侵,还可直接实现防御动作,避免 “检测 - 响应” 的延迟:

硬件化访问控制:当检测到恶意IP时,FPGA可直接更新访问控制列表(ACL),阻断该IP的后续数据包,响应延迟小于100ns;

流量清洗:在DDoS攻击场景中,FPGA可通过硬件化的流量分流算法,将正常流量与攻击流量分离,仅将正常流量转发至服务器,确保业务不中断。

典型案例:华为的USG6000E系列防火墙采用FPGA加速模块,实现100Gbps流量的实时IDS/IPS 检测,攻击特征匹配延迟小于50ns,可防御SYN Flood、UDP Flood等DDoS攻击,误报率低于 0.1%;美国Palo Alto Networks的下一代防火墙也集成FPGA,用于高速网络流量的恶意代码检测。

更多推荐

已为社区贡献184条内容

已为社区贡献184条内容

所有评论(0)