Latch-up 栓锁效应的防控之道

本文探讨了电子器件中的栓锁效应(Latch-up Effect)及其危害与防控策略。栓锁效应是CMOS器件中由过电、过流或外部干扰触发的寄生可控硅结构导致的失效现象,具有触发不可逆、电流激增和环境敏感等特征。该效应在航天、汽车、医疗等关键领域可能引发严重事故和经济损失。防控策略需贯穿芯片设计(物理隔离、电源域分区)、制造工艺(掺杂浓度优化)、封装测试(ESD防护)及终端应用(外围电路防护)全生命周

在航天卫星的 CMOS 控制电路中,一次高能粒子撞击引发的电压波动,竟让价值千万的载荷瞬间瘫痪;汽车发动机舱内,高温环境下的 MCU 芯片因突发栓锁,导致车辆动力系统骤停;消费电子工厂里,某批次智能手机充电 IC 因未通过栓锁测试,上市后引发大规模主板烧毁召回 —— 这些看似偶然的电子故障,都指向同一个技术隐患:栓锁效应(Latch-up Effect)。作为集成电路可靠性的 “隐形杀手”,栓锁效应在纳米级工艺、高功率应用、极端环境场景下的威胁愈发凸显。

定义与核心特征

在 JEDEC JESD78A 标准中被明确定义为:“集成电路中因过电、过流或外部干扰触发寄生可控硅(SCR)结构,形成电源到地的低阻通路,且该通路在触发条件消失后仍持续存在的失效现象”。其核心载体是 CMOS(互补金属氧化物半导体)器件,这一结构因固有寄生特性,成为栓锁效应的 “重灾区”。

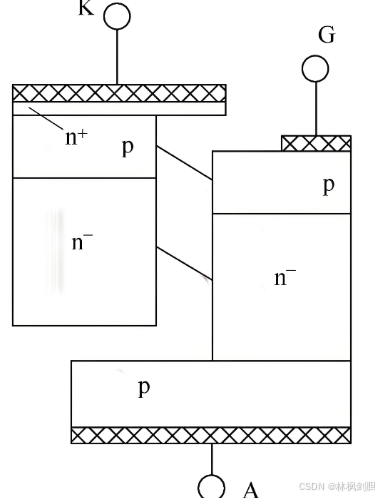

从结构本质来看,CMOS 器件的栓锁效应源于寄生双极晶体管(BJT)构成的晶闸管回路。在 P 型衬底上制作 N 沟道 MOS 管时,会形成 NPN 寄生晶体管(发射极:N + 源区,基极:P 型衬底,集电极:N 阱);而在 N 阱内制作 P 沟道 MOS 管时,又会形成 PNP 寄生晶体管(发射极:P + 源区,基极:N 阱,集电极:P 型衬底)。这两个寄生晶体管相互耦合,便构成了 “PNP-NPN” 四层晶闸管结构,如同在芯片内部埋下了一个 “隐形开关”,一旦被触发,就会形成 “电源→PNP 管→NPN 管→地” 的持续短路回路

栓锁效应具有三大核心特征:

- 触发不可逆性:触发条件(如电压尖峰、静电放电)消失后,短路状态仍持续,需切断电源才能恢复,部分严重案例会直接导致器件永久损坏;

- 电流激增特性:触发后回路电阻骤降,电流密度可达正常工作状态的 100-1000 倍,短时间内产生的焦耳热足以熔断金属互连线;

- 环境敏感性:温度每升高 10℃,栓锁触发阈值电流可能下降 8%-12%,高温(如汽车引擎舱 85℃+、工业控制 125℃)、高辐射(航天场景)环境会显著提升栓锁风险。

根据 JEDEC 标准,电子器件栓锁效应分为两大等级:

等级 A要求器件在室温及最高额定温度下,能承受 ±100mA 的正向 / 负向触发电流而不进入栓锁状态,适用于汽车、医疗等关键领域;

等级 B允许供应商根据器件功能(如低功耗 MCU、高压功率 IC)自定义触发阈值,多用于消费电子非核心电路。某 28nm 工艺 CMOS 芯片测试数据显示,等级 A 器件的栓锁免疫能力比等级 B 高 3-5 倍,在极端环境下的可靠性优势尤为明显。

失效机理:从寄生回路触发到热失控的全过程

栓锁效应的失效,是 “寄生回路激活→正反馈强化→热失控损坏” 的连锁过程,其核心在于寄生晶闸管的导通与维持,不同触发源会导致差异化的失效路径。

1. 触发阶段:寄生晶体管的 “激活开关”

栓锁效应的触发本质是寄生晶体管基极电流的异常注入,常见触发源可分为三类:

- 电压异常触发:输入引脚过压(如电源浪涌、静电放电)导致 PN 结击穿,注入的载流子使寄生晶体管基极电位偏移。例如,手机充电时的 220V 市电浪涌,可能让充电 IC 的输入引脚电压瞬间升至 30V,击穿栅氧层的同时,为寄生 PNP 管基极注入大量空穴,直接激活晶闸管回路;

- 电流扰动触发:电源域切换(如多电源芯片的上电顺序错误)产生的瞬时电流,或负载突变(如电机驱动 IC 的瞬间过载)引发的电流冲击,会改变寄生晶体管的偏置状态。某工业 PLC 的模拟量输入模块,因传感器突然断电产生的反向电流,使内部 ADC 芯片寄生 NPN 管导通,触发栓锁;

- 辐射粒子触发:航天、核工业场景中,高能粒子(如质子、重离子)撞击芯片衬底,会产生电子 - 空穴对,这些载流子在电场作用下聚集到寄生晶体管基极,形成触发电流。NASA 数据显示,近地轨道卫星中,单粒子闩锁(SEL)导致的器件失效占比达 15%,是航天器在轨故障的主要诱因之一。

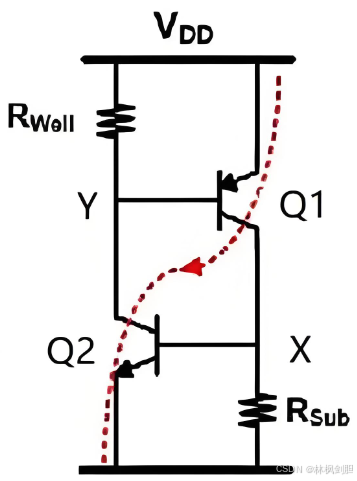

当寄生 NPN 与 PNP 晶体管的电流增益乘积(hFE1×hFE2)大于 1 时,满足栓锁维持条件 ——PNP 管集电极电流流入 NPN 管基极,使 NPN 管电流增大,而 NPN 管集电极电流又反过来注入 PNP 管基极,形成正反馈循环。此时即便移除触发源,回路电流仍会持续增大,进入 “自我维持” 的低阻状态。

2. 恶化阶段:从电流激增到热失控

栓锁触发后,回路电阻可从正常工作时的数千欧降至几十欧甚至更低,电源电压几乎全部加在寄生回路两端,根据欧姆定律,电流会急剧攀升。以某 5V 供电的 CMOS 逻辑芯片为例,正常工作电流约 10mA,栓锁触发后电流可飙升至 500mA 以上,功率损耗从 50mW 增至 2.5W,短时间内产生大量焦耳热。

温度升高又会进一步加剧栓锁恶化:

一方面,温度升高使半导体材料载流子迁移率提升,寄生晶体管电流增益(hFE)增大,正反馈效应更强;

另一方面,金属互连线电阻随温度升高而增大,局部发热集中,当温度超过铝线熔点(660℃)或铜线熔点(1083℃)时,会发生金属熔断,导致器件永久开路;若热量无法及时扩散,还可能引发芯片衬底开裂,彻底摧毁器件结构。某失效分析案例显示,一款未做栓锁防护的汽车 MCU,栓锁触发后仅 0.8 秒,芯片核心区域温度就从常温升至 420℃,铝互连线完全熔断。

栓锁效应的危害

栓锁效应在电子领域的危害具有层级传导性,从单个器件失效,逐步扩散至模块、系统,最终引发经济损失与安全风险,尤其在汽车、医疗、航天等关键领域,后果更为严重。

更严峻的是,汽车电子的栓锁失效可能引发连锁反应。例如,自动驾驶系统的激光雷达信号处理芯片若发生栓锁,会导致感知模块宕机,车辆失去环境识别能力,极易引发碰撞事故。据 AEC-Q100 标准统计,未做栓锁防护的汽车电子器件,在全生命周期内的失效概率是防护器件的 8-10 倍。

产业经济:成本失控与效率损耗

从产业链视角看,栓锁效应的经济损失贯穿设计、制造、应用全环节:

- 设计端:若流片后才发现芯片存在栓锁风险,需重新修改版图、再次流片,7nm 工艺下单次流片成本超 5000 万美元,延误上市周期可能导致市场份额被抢占;

- 制造端:出厂前未通过闩锁测试的器件流入下游,会导致客户端产品良率下降,某 PCB 厂商曾因采购的逻辑芯片存在栓锁隐患,导致整批次主板报废,损失超 2000 万元;

- 应用端:终端产品因栓锁问题召回,不仅涉及维修、赔偿成本,还会影响品牌信誉,某家电企业测算显示,一次栓锁相关的召回事件,会使后续 6 个月的产品销量下降 8%-15%。

栓锁效应的全周期预防策略

栓锁效应的防控,需贯穿 “芯片设计→制造工艺→封装测试→终端应用” 全生命周期,通过技术优化与规范管控,从源头阻断栓锁触发路径。

1. 芯片设计:从结构上 “瓦解” 寄生回路

设计阶段是防控栓锁的核心环节,关键在于通过结构优化削弱或切断寄生晶闸管回路:

- 物理隔离技术:采用深沟隔离(Deep Trench Isolation,DTI)在 N 阱与 P 衬底之间构建氧化硅隔离墙,阻断寄生晶体管的基极电流通路。某 65nm 工艺数据显示,采用 DTI 技术后,芯片的栓锁触发电流阈值提升 3 倍,寄生电容降低 25%;

- P + 护栏与 N + 衬底接触:在 N 阱边缘植入高浓度 P + 掺杂区(P+ Guard Ring),作为 minority carrier 收集层,将寄生 PNP 管基极的空穴导出;同时在 P 衬底中增加 N + 接触孔,缩短衬底电流路径,降低寄生 NPN 管基极电阻(见图 3:P + 护栏与 N + 衬底接触设计示意图);

- 电源域分区与隔离:对于多电源芯片(如 SoC),将模拟电路、数字电路、功率电路的电源域独立划分,通过限流电阻、TVS 管(瞬态电压抑制器)实现域间隔离,避免某一域的电压波动触发其他域的栓锁。例如,手机 SoC 的射频模块与基带模块之间,需串联 10Ω 限流电阻与 18V TVS 管,防止射频端的高压脉冲传导至基带。

2. 制造工艺:控制寄生参数的稳定性

制造环节需通过工艺管控,降低寄生晶体管的电流增益,确保栓锁防护设计落地:

- 衬底掺杂浓度优化:提高 P 衬底的硼掺杂浓度(从 1×10¹⁵/cm³ 提升至 5×10¹⁵/cm³),可降低寄生 NPN 管的基极电阻,减少电流增益;同时控制 N 阱的磷掺杂浓度,避免 PNP 管基区过薄导致增益过高;

- 氧化层质量管控:栅氧层的击穿电压直接影响栓锁触发风险,制造过程中需通过高温退火(1050℃,30 分钟)减少氧化层缺陷,确保栅氧击穿电压≥10V(对于 5V 供电芯片),避免过压击穿引发载流子注入;

- 金属互连线可靠性:采用铜 - 低 k 介质工艺时,需优化金属线宽与间距,避免栓锁触发时电流过大导致金属熔断。例如,电源总线的线宽应≥2μm,且每隔 50μm 设置一个冗余连接点,提升电流承载能力。

3. 封装与测试:阻断外部触发路径

封装与测试环节需通过防护设计与严格筛查,拦截潜在风险:

- 封装级 ESD 防护:在芯片封装引脚处集成片外 TVS 管或压敏电阻,吸收外部静电放电能量。例如,汽车电子芯片采用 QFP 封装时,电源引脚与地引脚之间需并联 15V/1000A 的 TVS 管,可将静电放电能量从 1000V 降至安全范围;

- 出厂闩锁测试:所有芯片需按照 JEDEC JESD78A 标准完成闩锁测试,高温环境(如 125℃)下的测试覆盖率需达 100%,剔除触发阈值不达标的器件。某芯片厂商通过自动化测试系统,可在 30 秒内完成一颗芯片的电流测试(±100mA)与电压测试(1.2 倍额定电压)。

4. 终端应用:规范使用与运维管控

下游应用端需通过电路设计与使用规范,降低栓锁触发概率:

- 外围电路防护:在芯片电源端串联自恢复保险丝(PTC),当栓锁触发电流超过阈值(如 100mA)时,PTC 迅速熔断,切断电源;输入输出引脚串联限流电阻(如 50Ω),限制外部干扰电流注入;

- 环境温度控制:对于高温应用场景(如汽车引擎舱),需为芯片配备散热片或导热垫,将芯片温度控制在栓锁风险阈值以下(如≤85℃)。某汽车 ECU 设计中,功率 IC 通过导热硅胶与铝合金壳体连接,散热效率提升 40%;

- 定期运维监测:对于关键设备(如医疗监护仪、工业 PLC),需定期(如每季度)进行栓锁风险检测,通过施加小幅电压波动,观察芯片电流变化,提前识别潜在隐患。

栓锁效应的标准化测试方案

栓锁效应的测试是验证防护效果、拦截风险器件的关键,电子领域已形成以 JEDEC 标准为核心,结合行业特殊需求的测试体系,确保测试结果的准确性与可比性。

1. 基础测试标准:JEDEC JESD78A

JEDEC JESD78A 是电子领域栓锁测试的 “通用准则”,明确了测试条件、流程与判据:

- 测试环境:分为室温(25℃±5℃,分类 I)与最高额定温度(如 125℃,分类 II),后者更贴近极端应用场景,需在恒温箱中完成;

- 测试类型:

- 电流测试(I-test):向芯片输入 / 输出引脚、电源引脚施加 ±100mA(等级 A)或自定义电流(等级 B)的脉冲(持续时间 100ms,脉冲间隔 1s),监测电源电流(Isupply)变化。若 Isupply 超过标称值 5 倍且持续 10ms 以上,判定为栓锁;

- 电压测试(V-test):向电源引脚施加 1.2 倍额定电压的脉冲(持续时间 500ms),同样监测 Isupply,判断标准与电流测试一致;

- 测试准备:芯片需处于正常工作状态(施加额定电压、时钟信号),输入引脚预置逻辑高 / 低电平,“空脚” 开路,避免测试状态与实际应用脱节。

2. 行业特殊测试标准

- 汽车电子(AEC-Q100):要求芯片在 - 40℃~125℃温度循环中完成栓锁测试,且需模拟电源波动(如 12V 系统瞬态电压 40V),确保高温、高电压下的可靠性;

3. 先进测试技术与设备

随着芯片工艺升级,栓锁测试技术也在不断革新:

- 动态闩锁测试:针对高速芯片(如 5G 射频 IC),需施加实际工作时钟信号(如 1GHz),在动态工作状态下测试栓锁风险,避免静态测试遗漏隐患;

- 三维测试系统:对于 3D IC 堆叠芯片,需通过探针台同时测试不同堆叠层的电源电流,识别层间耦合引发的栓锁问题;

- AI 辅助测试:利用机器学习分析海量测试数据,建立 “温度 - 电压 - 电流” 三维风险模型,快速定位高风险器件,某芯片厂商通过该技术将测试效率提升 50%,误判率降低至 0.1%。

先进工艺下的栓锁防控新挑战与新方案

随着电子器件向 “更先进工艺、更高功率、更极端环境” 发展,栓锁效应防控面临新挑战,同时也催生了创新技术方案。

1. 先进工艺(7nm 及以下)的挑战与应对

7nm 及以下工艺中,器件尺寸缩小导致寄生参数更敏感:一方面,N 阱与 P 衬底间距缩短,寄生晶体管基区变薄,电流增益(hFE)增大,栓锁阈值下降;另一方面,3D FinFET 结构的引入,使寄生回路更复杂,传统隔离技术效果减弱。

应对方案包括:采用全环绕栅极(GAA)结构减少寄生电容;引入异质衬底(如 SiGe) 降低寄生晶体管的电流增益;通过片上智能电源管理单元(PMU) 实现实时电流监测,一旦检测到异常电流,10ns 内切断电源。

2. 功率电子器件的栓锁防控

功率半导体(如 IGBT、SiC MOSFET)因工作电压高(数百伏)、电流大(数百安),栓锁风险更突出。针对这类器件,需采用栅极电压钳位技术,避免过压触发寄生回路;同时在芯片内部集成过流保护(OCP)模块,当检测到电流超过额定值 1.5 倍时,迅速关断器件。

3. AI 驱动的预测性防控

未来,栓锁防控将从 “被动测试” 转向 “主动预测”:通过在芯片内部植入微型传感器(监测温度、电流、电压),实时采集运行数据;结合云端 AI 模型,分析数据趋势,提前预测栓锁风险(如温度升高 10℃且电流波动超过 5% 时,发出预警),实现 “未失效先防护”。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)