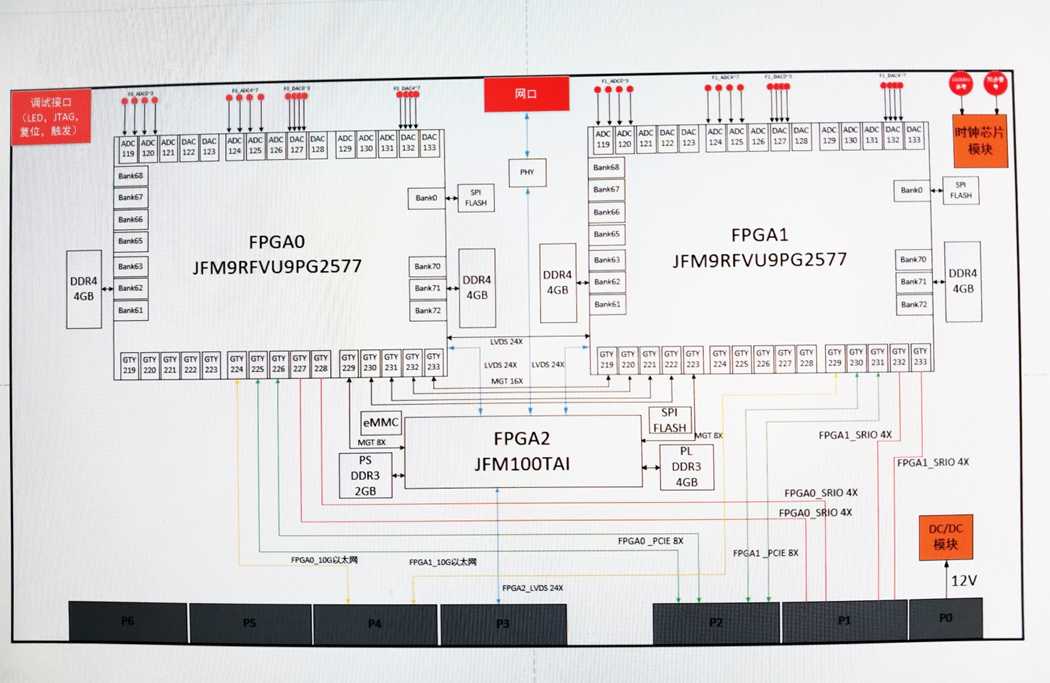

国产双复旦微VU9P+ZYNQ7100-6U VPX板卡

基于VU9P的全国产高性能处理板,主芯片由2片复旦微的 RFSOC 芯片 JFMSRFVU9PG2577和1片复旦微的SOC芯片:JFM100TAI组成。基于 VPX6U 架构的全国产化军温设计。

简介

基于VU9P的全国产高性能处理板,主芯片由2片复旦微的 RFSOC 芯片 JFMSRFVU9PG2577和1片复旦微的SOC芯片:JFM100TAI组成。基于 VPX6U 架构的全国产化军温设计。

技术规格:

(1)基于 VPX6U 架构;

(2)全国产化军温设计;

(3)扳载3片FPGA 处理器:2片复旦微的 RFSOC 芯片 JFMSRFVU9PG2577,1片复旦微的SOC芯片:JFM100TAI;

(4)处理器 JFM9RFVU9PG2577

每片 RFSOC外接2组DDR4 SDRAM,每组容量4GB,速率2400MT/S;

每片 RFSOC 对外引出8路ADC和8路DAC,ADC采样率最大支持5GSPS,量化位数14bit, DAC采样率最大支持6.5GSPS,量化位数14bit;

每片 RFSOC支持SPI程序记载模式,容量2Gb;

(5)处理器 JFM100TAI

PS外接 DDR3 SDRAM动态存储器,容量1GB,速率1333MT/S;

PS外接 eMMC存储器,容量不低于32Gb;

PL外接 DDR3 SDRAM动态存储器,容量 2GB,速率1333MT/S;

FPGA加载模式SPl flash,容量不低于256Mb;

(6)板内通信2片 RFSOC之间通过4路4X高速串口MGT连接,单个lane速率最高支持 20Gbps;

2片 RFSOC之间通过24对差分信号互联;

每片 RFSOC与JFM100TAI之间通过4X的高速串口MGT连接,单个lane速率最高支持10Gbps;

每片 RFSOC与JFM100TAI之间通过2路4X的高速串口MGT连接,单个lane速率最高支持10Gbps; (7)前面板调试接口

前面板一个HU301-55ZKw连接器,集成3片 FPGA的JTAG 调试接口,2片RFSOC串联,JFM1OOTAI的PS和PL JTAG独立连接;连接器集成1路 JFMIOOTAI 的 RS232通信接口;

连接器集成2路TTL输入和2路TTL输出信号;

连接器集成1路千兆以太网,连接到JFM1O0TAI;

(8)前面板模拟信号接口

前面板支持16路ADC和16DAC信号,连接器类型为SMP,输入输出阻抗为50欧;前面板支持1路100MH2 参考时钟连接器,用于板内ADC 和 DAC 采样时钟的参考;

(9)前面板LED指示灯

前面板支持8路指示灯,1个板卡上电正常信号,3个 FPGA处理器的加载完成指示信号,3个FPGA处理器的输出调试指示灯;

(10)VPX连接器

PO:2路I2C通信接口连接到JFM100TAI,物理地址识别信号连接到JFM100TAI,复位信号连接到3片 FPGA;

P1:2片 RFSOC 分别引出2路4X SRIO接口;

P2:2片 RFSOC分别引出2路8X PCie3.0接口;

P3:JFM100TAI引出24路 IVDS信号;

P4: 2片 RFSOC分别引出1路10G以太网SGMII接口;

(11)供电:12V@15A;

(12)健康管理:具有检测电流、温度和12V电压的能力。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)