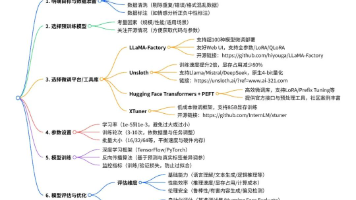

高带宽的L2 Cache的诀窍

高带宽L2 Cache设计的核心在于并行性、低延迟和高效互连,同时需权衡功耗与面积。关键窍门包括多端口、多银行、宽总线、高效一致性协议以及先进工艺的结合。针对具体应用场景(如GPU、CPU或AI加速器),需进一步定制优化。

·

-

多端口设计:

- 多读写端口:通过增加缓存的读写端口(如多银行设计),支持并行访问,提升带宽。每个银行可以独立处理请求,减少冲突。

- 交叉访问:采用交叉存取(bank interleaving)技术,将数据分布到多个银行,通过地址映射降低访问冲突。

- 非阻塞设计:确保缓存支持多个未完成请求(outstanding requests),通过流水线化操作提高吞吐量。

-

高频率与低延迟:

- 优化时钟频率:选择高性能的SRAM单元(如6T或8T SRAM),并优化读写电路设计,以支持更高的工作频率。

- 减少访问延迟:通过缩小缓存阵列的物理尺寸或采用更先进的工艺节点(如7nm、5nm)来降低信号传播延迟。

- 预取技术:通过智能预取算法,提前将可能需要的数据加载到L2 Cache,减少miss率,从而间接提升带宽利用率。

-

宽数据通路:

- 增加数据位宽:设计更宽的总线(如256位或512位),以在单次访问中传输更多数据。

- 突发传输(Burst Transfer):支持连续数据块的快速传输,减少总线切换开销。

-

高效的互连设计:

- 片上网络(NoC)优化:L2 Cache通常作为多核处理器之间的共享缓存,需通过高效的NoC连接到核心和其他缓存层,确保低延迟和高带宽。

- 优先级仲裁:在多核竞争访问L2 Cache时,设计高效的仲裁机制(如基于优先级的调度),避免瓶颈。

-

缓存一致性管理:

- 优化一致性协议:采用高效的缓存一致性协议(如MESI或MOESI的改进版本),减少一致性维护带来的带宽开销。

- 目录缓存:对于大型多核系统,使用基于目录的缓存一致性机制,降低广播开销。

-

功耗与面积优化:

- 动态电压频率调整(DVFS):根据负载动态调整缓存的工作频率和电压,平衡性能与功耗。

- 分区缓存:将L2 Cache划分为多个较小的子块,仅激活需要的部分,降低动态功耗。

- 高效的替换策略:优化缓存替换算法(如LRU或伪LRU),减少不必要的写回操作,提升带宽效率。

-

错误检测与容错:

- ECC支持:在高带宽场景下,数据完整性至关重要。加入错误检测与纠正(ECC)机制,确保高速传输的可靠性。

- 冗余设计:在关键路径上加入冗余单元,防止单点故障影响带宽。

-

先进工艺与3D堆叠:

- 采用先进工艺:利用3nm或更先进的制程技术,缩小晶体管尺寸,提升密度和速度。

- 3D缓存堆叠:通过TSV(硅通孔)技术将L2 Cache与处理器核心堆叠,缩短互连距离,显著提高带宽。

-

仿真与验证:

- 精准建模:在设计阶段使用高保真仿真工具(如SPICE或架构级模拟器)分析带宽瓶颈,优化关键路径。

- 实际负载测试:针对目标工作负载(如AI、HPC或游戏)进行优化,确保设计满足特定场景的高带宽需求。

总结:

高带宽L2 Cache设计的核心在于并行性、低延迟和高效互连,同时需权衡功耗与面积。关键窍门包括多端口、多bank、宽总线、高效一致性协议以及先进工艺的结合。针对具体应用场景(如GPU、CPU或AI加速器),需进一步定制优化。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)