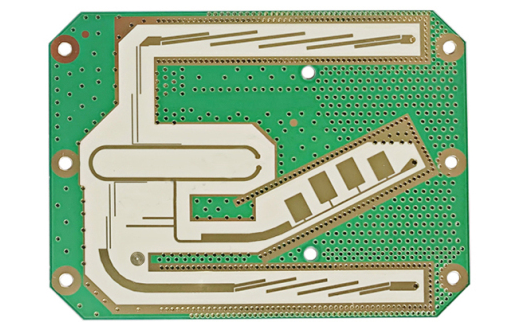

分享不同应用场景下PCB阻抗计算与仿真策略

高速数字PCB(服务器/AI芯片)需精准控制阻抗(单端50Ω±5Ω,差分100Ω±10Ω),通过高频阻抗计算和TDR仿真确保信号完整性;射频PCB(5G/WiFi7)要求50Ω阻抗在全频段波动≤±3%,需选用高频基材并仿真辐射和温度影响;电源PCB(服务器/新能源)需平衡低阻抗(DCR≤10mΩ)与散热,通过电流分布和热-电协同仿真优化设计。跨场景设备(如智能汽车)需分区布局并协同仿真数字、射频和

一、高速数字 PCB:聚焦信号完整性的阻抗设计

高速数字 PCB(如服务器主板、AI 芯片载板)的核心需求是控制信号反射与时延,信号速率多在 10Gbps 以上(如 PCIe5.0 达 32Gbps),阻抗设计需围绕 “一致性” 与 “稳定性” 展开:

(一)场景特性与阻抗要求

-

信号特点

高速数字信号上升沿极短(如 32Gbps 信号上升沿≤10ps),对阻抗突变敏感;差分信号占比高(如 DDR5、USB4),需同时控制差分阻抗(Zdiff=100±10Ω)与共模阻抗(Zcm≥300Ω)。

-

关键阻抗指标

-

特性阻抗:单端线 50±5Ω,差分线 100±10Ω(部分场景如 SATA 为 100±5Ω)。

-

阻抗一致性:同一网络不同区域的阻抗波动≤±5%(如传输线从芯片端到连接器端,Z0 需稳定在 48-52Ω)。

-

时延匹配:差分对的阻抗差异导致时延差(skew),需控制在 5ps 以内(避免时序偏移)。

(二)计算与仿真策略

-

计算要点

-

考虑趋肤效应:高频下电流集中在铜箔表面(趋肤深度 δ=√(ρ/(πfμ)),10GHz 时铜的 δ≈0.6μm),需选用 “高频阻抗公式”,或在计算中加入铜箔粗糙度修正(如粗糙度 0.8μm,需增加 5% 的阻抗补偿)。

-

差分线耦合:计算 Zdiff 时需考虑线间耦合(耦合越强,Zdiff 越低),避免用单端阻抗乘以 2 的简化方法(如单端 Z0=50Ω,Zdiff 并非 100Ω,需用耦合微带线公式)。

-

仿真重点

-

时域仿真:通过 TDR 曲线检查过孔、连接器处的阻抗突变(如过孔导致 Z0 从 50Ω 跳至 65Ω,需优化过孔结构:增加反焊盘、缩短 stub 长度至 0.5mm 以下)。

-

眼图分析:将阻抗仿真结果与芯片 IBIS 模型结合,生成眼图,判断阻抗不匹配是否导致眼图张开度不足(如眼高需≥0.4V,眼宽需≥20ps)。

-

多线串扰:仿真多根平行传输线的串扰(如相邻 DDR5 差分对的串扰需≤-25dB),避免因线距过近导致阻抗受干扰。

二、射频 PCB:高频下的阻抗稳定性设计

射频 PCB(如 5G 基站模块、WiFi 7 路由器)的信号频率多在 1GHz 以上(5G 毫米波达 28/39GHz),核心需求是控制阻抗稳定性、插入损耗与辐射干扰,阻抗设计需 “对抗高频效应”:

(一)场景特性与阻抗要求

-

信号特点

射频信号为正弦波,对介电常数的频率特性、寄生参数(如电感、电容)敏感;多采用微带线、共面波导结构,阻抗突变易导致功率反射与 EMC 问题。

-

关键阻抗指标

-

特性阻抗:射频信号线多为 50Ω(同轴电缆匹配),天线馈线可能为 75Ω;阻抗随频率的波动需≤±3%(如 28GHz 毫米波场景)。

-

插入损耗:10GHz 时每厘米传输线损耗≤0.3dB(含介质损耗与趋肤损耗)。

-

回波损耗:S11≤-20dB(反射功率≤1%)。

(二)计算与仿真策略

-

计算要点

-

介质材料选择:优先用高频低损耗基材(如罗杰斯 RO4350、泰康利 TLY-5),其 εr 频率稳定性好(如 RO4350 在 1-40GHz 内 εr 波动≤0.5%),减少阻抗随频率的变化。

-

寄生参数计算:射频线的寄生电感(L≈1nH/mm)与电容(C≈0.1pF/mm)需纳入计算,避免因寄生参数导致阻抗偏移(如长距离传输线需考虑分布参数影响)。

-

仿真重点

-

频域阻抗扫描:仿真 1-40GHz 内的 Z0 变化,确保全频段波动≤±3%(如 5G 毫米波 28GHz 频段,Z0 需稳定在 48.5-51.5Ω)。

-

电磁场辐射仿真:通过近场扫描观察是否存在电磁场泄漏(如辐射场强≤10mV/m,符合 EMC 标准),避免因阻抗不匹配导致辐射超标。

-

温度影响仿真:射频模块工作温度可达 85℃,需仿真温度对 εr 的影响(如 FR-4 温度每升高 10℃,εr 降低 0.1),确保高温下阻抗仍达标。

-

案例:5G 毫米波 PCB 阻抗设计

某 28GHz 毫米波模块采用罗杰斯 RO4350 基材(εr=3.48,tanδ=0.004),微带线参数:线宽 0.15mm、介质厚度 0.1mm、铜箔厚度 0.017mm(0.5oz)。计算 Z0≈50.2Ω;仿真 20-35GHz 频段,Z0 波动范围 49.5-50.8Ω(≤±3%),S11≤-22dB,插入损耗每厘米 0.25dB,满足 5G 基站要求。

三、电源 PCB:低阻抗与电流分布的平衡设计

电源 PCB(如服务器电源、新能源汽车 BMS)的核心需求是降低电源阻抗(减少电压跌落),同时避免大电流导致的热问题,阻抗设计需 “兼顾低阻与散热”:

(一)场景特性与阻抗要求

-

信号特点

电源信号为直流或低频交流(如开关电源频率 500kHz-2MHz),电流大(如服务器电源可达 100A),阻抗主要由铜箔电阻(直流阻抗)与寄生电感(交流阻抗)构成。

-

关键阻抗指标

-

直流阻抗(DCR):电源平面 DCR 需≤10mΩ(避免大电流下电压跌落超过 1V)。

-

交流阻抗(ACR):开关频率下的 ACR 需≤50mΩ(减少纹波电压)。

-

阻抗均匀性:电源平面各区域阻抗差异≤20%(避免电流集中导致局部过热)。

(二)计算与仿真策略

-

计算要点

-

直流阻抗计算:DCR=ρL/(WT)(ρ 为铜电阻率,20℃时 1.72×10^-8 Ω・m),如 10cm×20cm 的电源平面(铜箔 3oz,T=0.105mm),DCR≈1.72e-8×0.1/(0.2×0.000105)≈8.1×10^-5 Ω=0.081mΩ,符合要求。

-

交流阻抗计算:考虑寄生电感(电源平面的电感 L≈0.1nH/cm²),ACR=2πfL,如 2MHz 时 L=1nH,ACR≈2×3.14×2e6×1e-9≈12.56mΩ。

-

仿真重点

-

电流分布仿真:模拟大电流下的电流密度(需≤30A/mm²,避免铜箔烧毁),优化电源平面形状(如增加铜皮宽度、减少开槽)。

-

热 - 电协同仿真:阻抗导致的功耗(P=I²R)会产生热量,需结合热仿真判断温度是否超过基材耐温(如 FR-4 长期耐温 130℃),避免因温度升高导致铜箔电阻增大(温度每升高 1℃,铜电阻增加 0.4%)。

-

纹波仿真:将电源阻抗与负载模型结合,仿真输出纹波(如要求纹波≤50mV),判断是否需增加电容补偿(如并联 MLCC 降低 ACR)。

-

案例:新能源汽车 BMS PCB 阻抗设计

某 BMS PCB 需承载 50A 电流,电源平面采用 2oz 铜箔(T=0.07mm),面积 15cm×10cm。计算 DCR≈1.72e-8×0.15/(0.1×0.00007)≈3.69×10^-5 Ω=0.0369mΩ;仿真 50A 电流下,电流密度最大 25A/mm²(≤30A/mm²),温度升高 15℃(从 25℃至 40℃),ACR 在 1MHz 时≈8mΩ,纹波≤30mV,满足要求。

四、跨场景 PCB 的阻抗协同设计

部分设备(如智能汽车、工业物联网网关)同时包含高速数字、射频、电源模块,需协同设计阻抗:

-

分区布局

将高速数字区(DDR、PCIe)、射频区(4G/5G 模块)、电源区(DC-DC)分开布局,避免射频信号干扰数字信号阻抗,电源区铜皮与数字区参考平面隔离(减少地弹噪声)。

-

阻抗匹配协同

数字区与射频区的接口(如 SPI 通信)需统一阻抗(如 50Ω),避免接口处阻抗突变;电源区与数字区的供电接口需控制阻抗(如供电线 DCR≤5mΩ),减少电压波动对数字信号的影响。

-

仿真协同

采用多物理场仿真工具(如 ANSYS Multiphysics),同时仿真数字信号阻抗、射频阻抗、电源阻抗,分析三者的相互影响(如电源纹波是否导致数字信号阻抗波动),实现全局优化。

更多推荐

已为社区贡献18条内容

已为社区贡献18条内容

所有评论(0)