芯片验证工程师入门的学习路线

芯片验证工程师入门学习路线摘要 本文系统介绍了芯片验证工程师的核心学习路径,分为两大阶段: 基础准备(3-4个月): 掌握数字电路基础(逻辑门、时序电路) 理解验证原理(测试点提取、覆盖率分析) 精通SystemVerilog(重点学习OOP和约束随机) UVM方法学(3-5个月): 理解UVM核心组件(Driver、Monitor、Agent等)的协作机制 通过实践搭建完整验证平台 重点掌握工厂

芯片验证工程师入门的学习路线

一、前置基础

:先搞懂“为什么要学UVM”(1-2个月)

UVM是工具,但工具是为了解决问题而存在的。在学习之前,必须先理解“芯片验证的核心目标”和“UVM解决的痛点”,否则容易学成“只会敲代码,不懂为什么这么写”。

1. 数字电路基础(1-2周)—— 理解芯片的“硬件逻辑”

目标:搞懂DUT(被测设计,比如一个寄存器模块、UART控制器)的基本工作原理,知道验证平台要测什么。

核心内容:

•

基础逻辑:与门、或门、触发器(Flip-Flop)、寄存器(Register)——这些是芯片的最小单元。

•

时序逻辑:理解“时钟信号”如何控制数据的存储和传递(例如:D触发器在时钟上升沿锁存输入数据)。

•

简单模块:寄存器(读写操作)、计数器(递增/递减)、有限状态机(FSM,比如“空闲→接收数据→发送数据”的状态切换)。

•

总线协议基础:APB(简单外设总线)、AXI(高性能总线)的读写信号(如APB的PCLK时钟、PADDR地址、PWDATA写数据、PRDATA读数据)。

学习步骤:

看书/看视频:

•

推荐书籍:《数字电子技术基础》(阎石)前6章(重点看“逻辑门”“触发器”“时序分析”)。

•

免费替代:B站搜索“数字电路入门”(推荐“硬件茶谈”或“小梅哥”的数字电路基础课)。

2.

动手画图:拿纸笔画一个简单的寄存器模块(比如8位寄存器,有时钟、复位、写使能、数据输入/输出),思考它的功能(复位时输出全0,写使能有效时把输入数据存到寄存器里)。

3.

验证思维启蒙:问自己——“如果我要验证这个寄存器,需要测哪些场景?”(比如:复位后输出是否为0?写使能有效时数据是否正确写入?连续写多个数据是否都能保存?)

2. 芯片验证基础(2-3周)

—— 明确“验证工程师的职责”

目标:理解验证的目标(不是写代码,而是“证明芯片功能正确”)、验证的流程(从需求到最终覆盖率达标),以及为什么传统方法不够用(引出UVM的必要性)。

核心内容:

•

验证的本质:通过仿真(Simulation)运行DUT(被测设计),输入各种激励(测试用例),检查输出是否符合预期(比如:给寄存器写0x55,读出来是不是0x55?)。

•

验证流程:

1.

需求分析:芯片的功能说明书(比如“寄存器支持8位读写,复位后值为0”)。

2.

测试点提取:从需求中拆解出需要验证的具体场景(例如:正常读写、复位功能、边界值(写0xFF和0x00))。

3.

测试平台搭建:用代码模拟DUT的输入(激励),监测输出(结果),并判断是否正确。

4.

仿真与调试:运行仿真,发现DUT的bug(比如:写使能有效时数据没写入)。

•

传统验证的问题:直接写“定向测试”(比如固定输入0x01,0x02…),覆盖不全且难以维护;UVM通过“随机激励+标准化组件”解决这些问题。

学习步骤:

看书:《芯片验证漫游指南》(刘斌)第1-3章(用生活例子比喻验证,比如“验证就像测试手机功能——你要测打电话、拍照、充电,而不是只测开机”)。

2.

思考练习:找一个简单DUT(比如网上找的8位寄存器Verilog代码),尝试自己列出测试点(至少写5条,比如“复位后输出为0”“写0xAA后读出0xAA”)。

3. SystemVerilog语言(4-6周,重中之重!)—— UVM的“地基”

目标:掌握SystemVerilog的核心语法(尤其是面向对象编程OOP和约束随机),因为UVM是基于SystemVerilog的验证方法学。

核心内容:

•

基础语法(1周):变量类型(logic/bit)、模块(module)、任务(task)和函数(function)、条件语句(if-else/case)。

•

面向对象编程(OOP,3周):这是UVM的核心!必须熟练掌握:

•

类(class):定义对象的模板(比如“激励事务类transaction”可以包含地址、数据、读写标志)。

•

对象(object):类的实例(比如生成一个具体的transaction对象,地址=0x10,数据=0x55)。

•

继承(inheritance):子类继承父类的属性和方法(比如“读事务”继承“事务基类”,并增加读标志位)。

•

多态(virtual function):父类指针可以指向子类对象,运行时调用子类的方法(UVM中通过多态实现灵活的Driver处理不同事务)。

•

约束随机(constraint random):自动生成符合规则的随机数据(比如“生成0~255的随机数据”“地址必须对齐4字节”),比手动写固定测试更全面。

•

**

验证平台组件(2周):

**

•

接口(interface):封装DUT的信号(比如APB的时钟、地址、数据信号),避免在多个模块中重复定义。

•

虚拟接口(virtual interface):在Testbench中通过指针将接口传递给各个组件(比如Driver需要访问APB接口的信号)。

•

测试平台结构:Test(顶层控制)、Generator(生成激励)、Driver(驱动DUT)、Monitor(监测DUT输出)、Scoreboard(比对结果)。

学习步骤:

系统学习语法:

•

必看书籍:《SystemVerilog验证(原书第3版)》(Chris Spear)第1-5章(重点看类、继承、约束随机)。

•

免费替代:B站搜索“SystemVerilog验证教程”(推荐“路科验证”的SystemVerilog基础课)。

2.

小实验练手:

•

实验1(基础语法):写一个简单的SystemVerilog模块(比如加法器),用定向测试(固定输入1+1,2+3…)验证输出。

•

实验2(OOP):定义一个“transaction类”(包含addr, data, is_write三个变量),并创建它的对象。

•

实验3(约束随机):给transaction类添加约束(例如:constraint addr_align { addr % 4 == 0; } // 地址必须是4的倍数),生成100个随机事务并打印,观察地址是否符合规则。

3.

常见问题:

•

问题:“class和module有什么区别?” → module是硬件描述(对应实际电路),class是软件对象(用于描述激励和验证逻辑)。

•

问题:“约束随机不生效?” → 检查是否在生成对象时调用了randomize()方法(例如:if (!txn.randomize()) $error(“随机失败”);)。

二、UVM核心方法学:从“是什么”到“怎么用”(3-5个月)

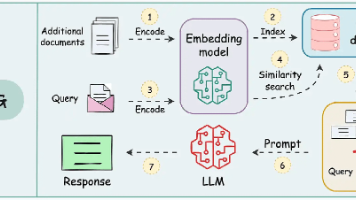

UVM是一套标准化的验证框架,核心是通过“组件化+层次化”让验证平台更易维护和复用。此阶段要理解UVM的每个组件“做什么”,并通过代码实践掌握它们的协作流程。

1. UVM基础概念(2-3周)—— 认识UVM的“全家桶”

目标:理解为什么需要UVM,以及UVM的核心组件(如Driver、Sequencer、Agent等)如何分工协作。

核心内容:

•

为什么需要UVM?:传统Testbench的问题(代码复用性差、难以扩展、维护困难)→ UVM通过标准化组件和工厂模式解决(比如同一个Driver可以适配不同协议,只需修改少量代码)。

•

UVM的核心组件(重点!):

组件 作用 类比

Driver 根据transaction生成DUT需要的信号(比如APB的PADDR、PWDATA) “快递员”:把transaction里的地址和数据变成DUT能理解的时序信号

Monitor 监测DUT的输出信号(比如PRDATA),并转换成transaction上报 “摄像头”:记录DUT的输出并打包成数据对象

Sequencer 生成并调度transaction序列(决定先发什么激励) “调度中心”:管理一堆待发送的“任务”(transaction)

Agent 封装Driver+Monitor+Sequencer(一个Agent对应DUT的一个接口,比如APB接口) “接口团队”:包含和该接口相关的所有验证逻辑

Environment 整合多个Agent(比如APB Agent + UART Agent) “项目管理组”:协调所有接口的验证工作

Test 顶层控制(选择哪个Sequence运行、设置全局参数) “总导演”:决定验证的策略和目标

•

UVM的基石机制:

•

工厂模式(uvm_factory):通过配置动态替换组件(比如用Mock Driver替换真实Driver做故障测试)。

•

虚接口(virtual interface):在Testbench中把DUT的接口信号(如APB的时钟、地址线)传递给Driver/Monitor。

•

配置数据库(uvm_config_db):全局共享数据(比如把DUT的接口句柄传给Driver,把测试参数传给Sequence)。

•

TLM通信(Transaction-Level Modeling):Sequencer和Driver通过put/get端口交互(Driver从Sequencer获取transaction)。

学习步骤:

看书/看视频:

•

必看书籍:《UVM实战》(张强)第1-5章(中文讲解最易懂,结合代码示例)。

•

视频:B站搜索“UVM实战 张强”(推荐第1-10讲,讲清楚UVM组件的作用)。

2.

画图理解:拿纸笔画一个简单的UVM平台架构图(比如验证APB寄存器,包含1个APB Agent,Agent里有Driver/Monitor/Sequencer,连接到Environment,再接到Test)。

3.

关键问题思考:

•

“Sequencer和Driver是怎么配合的?” → Sequencer生成transaction,Driver通过TLM端口(get_next_item())获取transaction,然后转换成DUT的时序信号。

•

“为什么要用uvm_config_db?” → 避免硬编码(比如Driver需要知道DUT的接口地址,通过配置数据库动态传递,而不是在代码里直接写死)。

2. UVM组件开发与TLM通信(4-6周)—— 亲手搭一个验证平台

目标:从0开始手写一个完整的UVM验证平台(比如验证一个简单的8位寄存器模块),熟悉各组件的代码实现和协作流程。

核心内容:

•

步骤1:准备DUT(1周):找一个简单的Verilog模块(比如8位寄存器,有时钟clk、复位rst_n、写使能we、地址addr、写数据wdata、读数据rdata)。

•

步骤2:定义Transaction类(1周):描述激励的数据结构(例如:class apb_transaction; logic [3:0] addr; logic [7:0] data; bit we; endclass)。

•

步骤3:实现UVM组件(3-4周):

•

Driver:从Sequencer获取transaction,根据we信号生成APB的时序(例如:复位后拉低PENABLE,写使能有效时在PCLK上升沿锁存PADDR和PWDATA)。

•

Monitor:监测DUT的输入(PADDR, PWDATA, PWE)和输出(PRDATA),转换成transaction并上报给Scoreboard。

•

Sequencer:生成并调度transaction序列(例如:先发一个写事务,再发一个读事务验证数据一致性)。

•

Agent:整合Driver/Monitor/Sequencer(通过参数配置是主动Agent(驱动DUT)还是被动Agent(监测DUT))。

•

Test:创建Sequencer和Driver,启动Sequence(例如:调用一个“写-读验证序列”)。

•

关键代码示例(简化版):

// 1. Transaction类(定义激励数据结构)

class apb_transaction extends uvm_sequence_item;

rand logic [3:0] addr; // 4位地址

rand logic [7:0] data; // 8位数据

rand bit we; // 写使能(1=写,0=读)

`uvm_object_utils_begin(apb_transaction)

`uvm_field_int(addr, UVM_DEFAULT)

`uvm_field_int(data, UVM_DEFAULT)

`uvm_field_int(we, UVM_DEFAULT)

`uvm_object_utils_end

function new(string name="apb_transaction");

super.new(name);

endfunction

endclass

// 2. Driver(将transaction转为DUT的时序信号)

class apb_driver extends uvm_driver #(apb_transaction);

virtual apb_interface vif; // 虚接口(连接到DUT的APB信号)

task run_phase(uvm_phase phase);

forever begin

seq_item_port.get_next_item(req); // 从Sequencer获取transaction

// 生成APB写时序(假设协议:PSEL拉高→PADDR/PWDATA有效→PENABLE拉高→等待时钟上升沿→PENABLE拉低)

vif.psel <= 1'b1;

vif.paddr <= req.addr;

vif.pwdata <= req.data;

vif.pwrite <= req.we;

@(posedge vif.pclk);

vif.penable <= 1'b1;

@(posedge vif.pclk);

vif.penable <= 1'b0;

vif.psel <= 1'b0;

seq_item_port.item_done(); // 通知Sequencer当前transaction完成

end

endtask

endclass

•

步骤4:仿真验证(1周):用ModelSim/QuestaSim运行仿真,观察波形(比如APB的PADDR、PWDATA是否按预期变化),检查DUT的输出(rdata)是否正确。

3. 功能覆盖与断言(2-3周)—— 确保验证的“完备性”

目标:通过功能覆盖(Functional Coverage)和断言(Assertion)发现验证盲区,避免漏测关键场景。

核心内容:

•

功能覆盖:定义需要覆盖的场景(例如:寄存器的所有地址是否被读写过?写操作是否覆盖了全0和全1的数据?),通过covergroup统计覆盖率。

class apb_coverage extends uvm_subscriber #(apb_transaction);

covergroup addr_data_cg @(posedge vif.pclk);

coverpoint req.addr { bins addr_bins[] = {[0:15]}; } // 覆盖所有8位地址(0~15)

coverpoint req.data { bins data_bins[] = {[0:255]}; } // 覆盖所有8位数据

coverpoint req.we { bins write = {1}; bins read = {0}; } // 覆盖读写操作

endgroup

function new();

addr_data_cg = new();

endfunction

endclass

•

断言:在DUT内部或Monitor中插入时序检查(例如:“写使能有效时,数据必须在时钟上升沿稳定”)。

// 在DUT的Verilog代码中插入断言(检查写数据稳定性)

property write_data_stable;

@(posedge clk) (we && penable) |-> $stable(wdata);

endproperty

assert_write_data_stable: assert property (write_data_stable) else $error("写数据在使能期间不稳定!");

学习步骤:

在之前的验证平台中添加覆盖组:在Monitor或Environment中实例化covergroup,统计关键场景(如地址覆盖、数据覆盖)。

2.

运行仿真并查看覆盖率报告:仿真结束后,通过工具(如QuestaSim的Coverage Browser)查看覆盖率是否达标(目标通常是功能覆盖率达到90%+)。

3.

添加断言:在DUT的关键路径(如复位逻辑、数据握手)插入断言,检查时序违规。

三、工业级实战与进阶(2-4个月)

通过真实协议验证和复杂场景练习,掌握UVM的高级用法,并了解团队协作流程。

1. 复杂协议验证项目(4-6周)—— 挑战AXI/I2C等协议

目标:选择一个工业常用协议(如AXI-Lite、I2C),从0搭建验证平台,覆盖协议的所有关键场景(正常操作+异常处理)。

推荐协议:

•

AXI-Lite(简单版AXI,适合入门):包含读写通道(AW/AWVALID, W/WVALID, B/BVALID, AR/ARVALID, R/RVALID),重点验证地址对齐、突发传输、错误响应。

•

I2C(串行总线):包含SCL时钟线、SDA数据线,重点验证起始/停止条件、ACK/NACK信号、主从设备通信。

实施步骤:

学协议规范:下载官方协议文档(如ARM的AXI协议规范),重点看“读写时序”“信号定义”“错误场景”。

2.

设计测试点:例如AXI-Lite的测试点包括:

•

正常读写(地址对齐4字节,数据宽度32bit);

•

错误响应(写无效地址,DUT返回SLVERR);

•

突发传输(连续读写多个数据);

•

复位功能(复位后所有通道无效)。

3.

开发验证平台:复用UVM组件(Agent/Driver/Monitor),但需根据协议调整Driver的时序逻辑(例如AXI的写通道需要先发地址(AW),再发数据(W),最后收响应(B))。

2. UVM高级特性(2-3周)—— 提升平台灵活性

核心内容:

•

分层Sequence(Virtual Sequence):协调多个子Sequence的执行顺序(例如:先初始化寄存器,再执行功能测试)。

class init_sequence extends uvm_sequence #(apb_transaction);

task body();

// 发送写事务初始化寄存器

repeat(5) begin

`uvm_do_with(req, { req.we == 1; req.addr inside {[0:3]}; })

end

endtask

endclass

class func_test_sequence extends uvm_sequence #(apb_transaction);

task body();

// 发送读事务验证数据

repeat(5) begin

`uvm_do_with(req, { req.we == 0; req.addr inside {[0:3]}; })

end

endtask

endclass

class top_virtual_sequence extends uvm_sequence;

task body();

init_sequence init_seq = init_sequence::type_id::create();

func_test_sequence func_seq = func_test_sequence::type_id::create();

init_seq.start(null); // 先执行初始化

func_seq.start(null); // 再执行功能测试

endtask

endclass

•

Factory Override:动态替换组件(例如用Mock Driver模拟DUT故障,测试验证平台的容错能力)。

•

寄存器模型(uvm_reg):自动生成寄存器的读写测试序列(避免手动写每个地址的测试)。

3. 团队协作与流程(1-2周)—— 了解工业环境

•

学习内容:

•

验证计划:如何根据芯片需求制定验证策略(比如优先验证核心功能,再覆盖边界条件)。

•

回归测试:如何通过脚本自动运行所有测试用例(例如用Makefile或Jenkins)。

•

覆盖率收敛:如何通过增量仿真逐步提高覆盖率(比如先测功能,再补边界场景)。

•

工具实践:学习使用Git管理代码版本,用Shell/Python写仿真脚本(例如一键运行仿真并收集覆盖率)。

四、关键学习建议

1.

动手>理论:每学一个概念(如Sequencer),立刻手写对应的SystemVerilog代码(哪怕先抄例子再改)。

2.

从简单到复杂:先做无协议的模块验证(如计数器),再逐步挑战AXI/I2C等复杂协议。

3.

查文档:遇到UVM报错(比如“uvm_error: component not found”),学会阅读仿真日志和UVM官方手册(uvm_user_guide.pdf)。

4.

加入社区:关注“路科验证”“芯司机”公众号,或加入芯片验证交流群(如EETOP论坛的验证板块),遇到问题及时提问。

按照这个详细路线坚持实践,6按照这个详细路线坚持实践,6-12个月后你将具备独立搭建UVM验证平台的能力,能够应对企业级芯片验证岗位的需求!@TOC

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)