GaN-on-Si材料外延生长工艺

文章简要介绍了GaN-on-Si材料外延基本工艺和部分需要考虑的问题

ⅠGaN-on-Si材料外延生长工艺

纤锌矿型GaN材料具有稳定的六方晶体结构,Si(111)面衬底与GaN(0002)面具有相似的六方结构[1]。在本章中,我们认为GaN-on-Si为Si(111)面上生长的纤锌矿结构的GaN。本章重点介绍主要的GaN外延工艺和相应的挑战。

GaN材料在Si衬底上生长的主要方式为Ga源和N源的化学反应,主要应用的技术有MOCVD[2]和MBE[3]。两者相比而言,MBE生长质量更高但技术复杂、生长速度慢且成本较高,而MOCVD生长技术简单快捷、成本低且生长速度快,便于生长大尺寸器件。因此,MOCVD技术应用更为广泛。目前,MOCVD的主要设备生产商有Aixtron(德国)、Veeco(美国)、中微半导体(中国)等。图1为Aixtron生产的MOCVD设备。

Aixtron MOCVD

尽管目前应用MOCVD进行Si基GaN材料生长的技术已经非常成熟,但是Si基GaN材料的生长仍旧存在有很多的挑战。首先,GaN材料与Si材料之间存在有较大的晶格失配(17%),这会导致在异质外延的过程中引入高密度的位错(10e8~10e10cm-2)[4]。这些位错包括堆垛层错、空位、穿通位错等,这会导致器件电学性能的退化,包括漏电通道增加、击穿电压降低、器件可靠性下降等[5]。其次,GaN和Si之间存在有较大的热失配问题(54%),这可能导致GaN中出现裂纹[6]。这主要是因为在生长工艺中的冷却过程中,由于Si比GaN具有更小的热膨胀系数,因此上层GaN材料会受到较大的张应力,从而导致材料裂纹。另外,在Si衬底尺寸较大(≥150mm)时,GaN-on-Si晶圆会出现明显的翘曲效应[7],这会导致表面粗糙度或掺杂的一致性较差,外延层中的应力也会受到影响。最后,在GaN-on-Si高温外延生长过程中,GaN和Si的界面反应会导致熔化背刻蚀,生成Si-Ga合金从而阻碍GaN成核[8]。其中主要由于反应腔室内气压高于金属Ga蒸汽压,Si衬底上会形成液态金属Ga并与Si发生反应。在早期熔化背蚀刻过程中,GaN外延层表面会形成大量的孔洞和凹坑,阻碍了外延生长过程,导致GaN基器件寄生电导和过早击穿[9]。为了解决上述问题,应力调控结构被引入来限制熔化背刻蚀过程,降低穿通位错密度,并通过平衡外延层张应力来消除裂纹。

Ⅱ应力调控结构

2.1AlN成核层

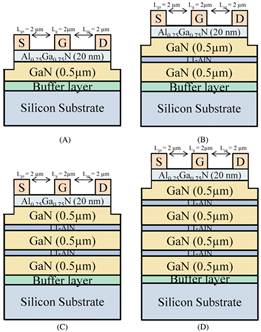

为了避免熔化背刻蚀效应的影响,获得Si衬底上的高质量GaN薄膜,研究人员在GaN和Si衬底之间设计了成核层,其中包括AlN、AlAs、SiNx、SiC和Al2O3等。AlAs中间层具有较高的热稳定性,抑制了Si衬底的氮化,但GaN在生长过程中是部分多晶的[20]。在SiC/Si表面生长的GaN在700℃以下生长速率较低,结晶质量较差[10]。Al2O3到GaN层的应力转变随厚度的变化而变化,目前还在研究中[11]。相比于这些成核层,AlN成核层得到了广泛应用,主要有以下原因。第一,AlN晶格常数(a=0.3112nm)小于GaN晶格常数(a=0.3189nm),AlN和GaN之间的晶格失配为2.6%,引入了一部分压应力[12]来补偿热失配产生的张应力。第二,通过插入薄AlN作为(Al)GaN层生长的成核层,避免了Si和Ga原子之间的熔融背蚀刻过程,从而避免了Ga和Si之间的相互扩散。最后,AlN成核层能够为氮化镓晶体提供成核中心,并促进薄膜的横向生长[13]。因此,AlN成核层的生长对于后续GaN或AlGaN的材料外延都是至关重要的。例如,Lin等人[14]通过引入多层LT-AlN层实现了GaN层内低应力,实现了无裂纹GaN-on-AlN,图2给出了相应的器件结构。然而,AlN层在Si上的生长是非常困难

图2 多层AlN层实现应力调控

的,主要是因为AlN在Si表面的迁移率不足会抑制结构重新排列[15],AlN与Si之间界面反应产生的非晶态氮化硅会诱发大量缺陷。考虑到上述问题,研究人员一般会通过调整生长条件来提高Al原子迁移率,避免Si衬底表面被氮化,从而实现高质量的AlN层。举例而言,较低的Ⅴ/Ⅲ比、调节生长温度、铝源预反应等可实现高质量AlN生长。并且,当生长温度1100℃以上可实现Si衬底上高质量的AlN层生长[16]。然而,当AlN生长温度高于900℃时,会导致反转沟道的产生,即在高漏压时,会导致电子注入成核层,从而导致器件过早击穿[17]。因此,研究人员提出了AlN成核层两步生长法,抑制了成核层导电沟道的产生,提高了AlN层晶体质量。AlN层的生长主要用MOCVD或MBE,低温外延工艺得到进一步探索,主要是因为高温外延会生成非晶层,导致AlN/Si界面处高密度的位错和缺陷。

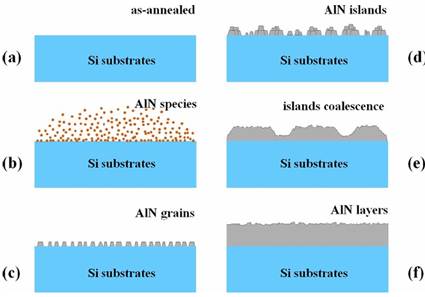

为了解决上述问题,提出了脉冲激光淀积(PLD)技术,它采用高能脉冲激光烧蚀生长靶,使AlN前驱体在衬底上扩散和迁移,从而在相对较低的生长温度下实现氮化物的外延生长[18]。1995年,Vispute等人首次报道了通过脉冲激光烧蚀AlN靶材实现了Si衬底上单晶AlN的生长[19]。2010年,Li等人报道了PLD外延生长高质量AlN薄膜,并分析了靶材与Si衬底之间的距离对外延AlN薄膜质量的影响以及PLD生长机制[20]。图3给出了用PLD在Si衬底上生长AlN薄膜的机理示意图。

图3 PLD生长AlN薄膜机理[21]

2.2 缓冲层

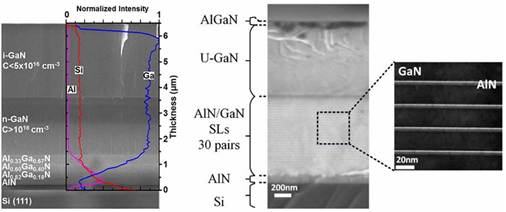

尽管AlN层已经实现在Si衬底上的高质量生长,但是在进行上层GaN材料的外延时,由于生长后冷却时,不同材料之间存在热膨胀系数的差异,往往会导致GaN层中出现裂纹。不同材料之间的晶格失配和热失配使得材料生长过程中会出现应力积累,存在一个材料生长厚度的临界值。当生长厚度大于临界值时,出现应力弛豫,材料破裂。在生长过程中,还会因为各种失配引入了大量的位错和缺陷,如穿通位错、N空位等。这些位错和缺陷的存在使得器件特性退化,缓冲层漏电加剧,器件过早击穿。为了解决这一问题,研究人员们对外延过程中的缓冲层进行了多种结构设计的探索。如AlGaN缓冲层、Al(Ga)N/GaN超晶格缓冲层等。图4分别给出了Al组分阶梯变化的AlGaN缓冲层和AlN/GaN超晶格缓冲层。

图4 Al组分阶梯变化[22]和超晶格型的缓冲层结构[23]的SEM图

理论推算得出10-20nm的LT-AlN层能够平衡0.7-1µm厚GaN的张应力[24],为了生长更厚并且无裂纹的GaN层,提出了周期性插入LT-AlN层来补偿张应力的方法[25]。2011年,Dadgar等人[26]采用多层LT-AlN插入层的方法生长了14.6µm厚的高质量无裂纹GaN层。紧接着,Wosko等人[27]通过调整GaN生长过程中的Ⅴ/Ⅲ比并采用LT-AlN插入曾,实现了AlGaN/GaN异质结,迁移率达到了2057cm2/(V·s),方块电阻Rsh达到了392Ω/sq。虽然此时实现了较好的材料生长,但对于GaN HEMT器件而言,晶体质量还需要进一步提高。AlGaN缓冲层主要包括有Al组分步阶变化和线性变化两种类型,原理为通过实现晶格常数和热膨胀系数的逐渐变化来进行应力补偿,避免出现晶圆翘曲、大量位错和晶圆裂纹,从而减少漏电并提高击穿电压。除此之外,在GaN HEMT器件中,AlGaN缓冲层能够起到背势垒的作用,提高二维电子气的限域性,降低缓冲层漏电,提高器件击穿电压。Cheng等人[28]通过采用低Al成分的单AlGaN缓冲层层,成功地在Si衬底上制造了高质量和均匀的AlGaN/GaN异质结构,表现出2150 cm2 V-1 s-1的高电子迁移率,以及9.3×1012 cm-2的ns,Rsh为313 ± 4 Ω sq-1,变化±1.3%。随后,Li 等[29]提出了阶梯型的AlGaN缓冲层,生长3.0 μm厚的高质量GaN外延层XRD扫描GaN(0002) GaN(1012)半高宽分别为272arcsec和297arcsec。超晶格结构的缓冲层有AlGaN/AlGaN型、AlN/GaN型、AlGaN/AlN型等。2014年,Shen等人[30]报道了MOCVD生长的Si基AlGaN/GaN异质结,并运用了AlN/GaN超晶格结构,电子迁移率和二维电子气浓度分别达到了~1500 cm2 V-1 s-1和1.2×1013 cm-2。在上述这些缓冲层设计当中,渐变AlGaN和超晶格结构被广泛应用于GaN基HEMT器件当中。

参考文献

- Park K, Min J W, Subedi R C, et al. THz behavior originates from different arrangements of coalescent GaN nanorods grown on Si (111) and Si (100) substrates[J]. Applied Surface Science, 2020, 522: 146422.

- Zhang Y, Chen Z, Li W, et al. Probing unintentional Fe impurity incorporation in MOCVD homoepitaxy GaN: Toward GaN vertical power devices[J]. Journal of Applied Physics, 2020, 127(21).

- Borisenko D P, Gusev A S, Kargin N I, et al. Plasma assisted-MBE of GaN and AlN on graphene buffer layers[J]. Japanese Journal of Applied Physics, 2019, 58(SC): SC1046.

- Zhang J et al 2020 Vacancy-engineering-induced dislocation inclination in III-nitrides on Si substrates Phys. Rev. Mater. 4 073402.

- Narita T, Nagasato Y, Kanechika M, et al. Increase of reverse leakage current at homoepitaxial GaN pn junctions induced by continuous forward current stress[J]. Applied Physics Letters, 2021, 118(25).

- Feng M, Liu J, Sun Q, et al. III-nitride semiconductor lasers grown on Si[J]. Progress in Quantum Electronics, 2021, 77: 100323.

- Lee L Y, Frentrup M, Kappers M J, et al. Effect of growth temperature and V/III-ratio on the surface morphology of MOVPE-grown cubic zincblende GaN[J]. Journal of Applied Physics, 2018, 124(10).

- Khoury M, Tottereau O, Feuillet G, et al. Evolution and prevention of meltback etching: Case study of semipolar GaN growth on patterned silicon substrates[J]. Journal of applied physics, 2017, 122(10).

- Mantach R, Vennéguès P, Perez J Z, et al. Semipolar (10-11) GaN growth on silicon-on-insulator substrates: defect reduction and meltback etching suppression[J]. Journal of Applied Physics, 2019, 125(3).

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)