FPAGA学习~问题记录

FPGA常见问题记录

·

1.Error: concurrent assignmentto a non-net'start' is not permitted(错误:不允许并发分配到非网络‘start’)

原因:wire 或reg 类型不匹配引起的,assign与wrie搭配使用,而reg一般在always、initial语句块中进行使用。

解决办法:此处,将reg型变为wire型即可。

2.[Labtools 27-1832] create_wave_config not a supported tcl command in labtools hardware mode. Default wave configurations are automatically created when triggering an ILA core.(在labtools硬件模式下,Create_wave_config不是支持的TCL命令。触发ILA核时自动创建默认波配置。)

原因:开发板断开连接后没有管,直接改程序又仿真

解决办法:重启该项目文件

3.Verilog 2000 keyword else used in incorrect context(Verilog 2000关键字else在不正确的上下文中使用)

原因:多条语句没有begin-end

解决办法:加begin-end

4.part-select direction is opposite from prefix index direction (部分选择方向与前缀索引方向相反)

原因:数组里面的顺序放反了,大在前,小在后

解决办法:将数组顺序更改正确

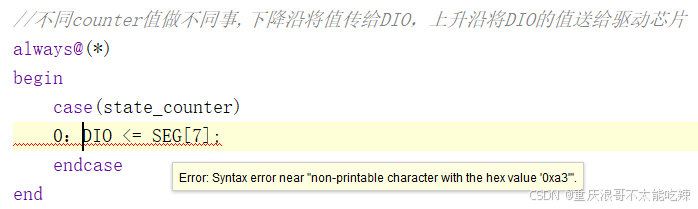

5.Syntax error near "non-printable character with the hex value '0xa3"。(“十六进制值为‘0xa3 ’的不可打印字符”附近的语法错误)

原因:冒号用了中文符号

解决办法:将符号改为英文格式

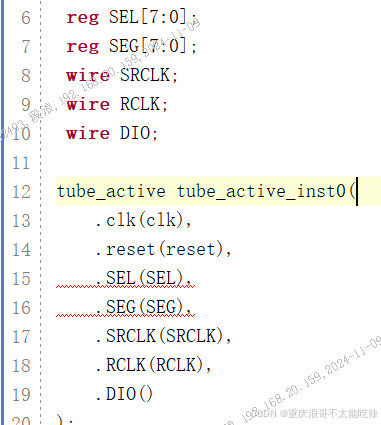

6.Error: cannot access memory'SEL' directly(错误:不能直接访问内存‘ sel ’)

原因:数组位置放错

解决办法:数组[ ]放在端口前。

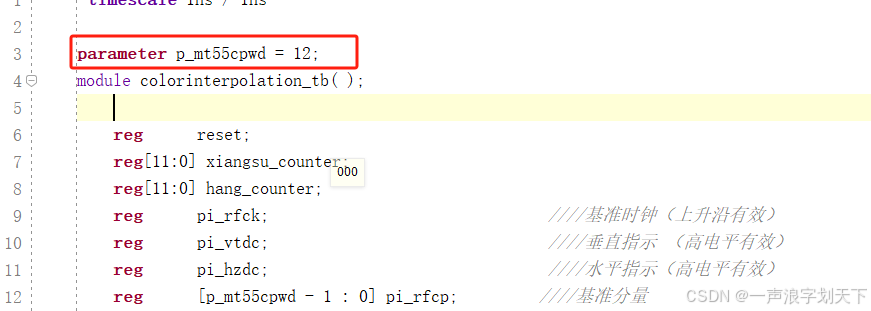

7. [VRFC 10-1342] root scope declaration is not allowed in verilog 95/2K mode [VRFC 10-1342]在verilog 95/2K模式下不允许根作用域声明

原因:在moudule模块外定义了参数

解决办法:将定义参数移至module模块内

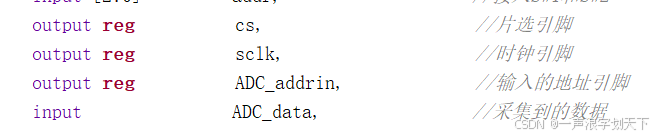

8.[Synth 8-685] variable 'cs' should not be used in output port connection.变量‘cs’不应用于输出端口连接

原因:端口类型不正确,这里的cs只是起到一个连接的作用。

解决办法:删除reg

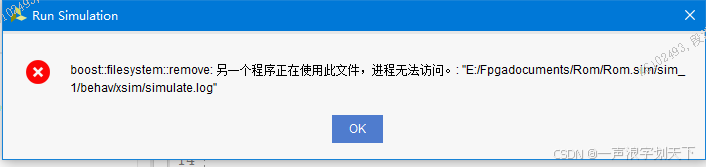

9.boost:filesystem:remove:另一个程序正在使用此文件,进程无法访问。:"E:/Fpgadocuments/Rom/Rom.simisim_024931/behav/xsim/simulate.log'

解决办法:1.关闭工程重启。2.关掉工程源文件与仿真文件以及仿真页面,重新点仿真。

10.FIFO没有writebusy信号

原因:选错了器件或者刚开始创建工程没选器件,器件不同,FIFO之间不通用

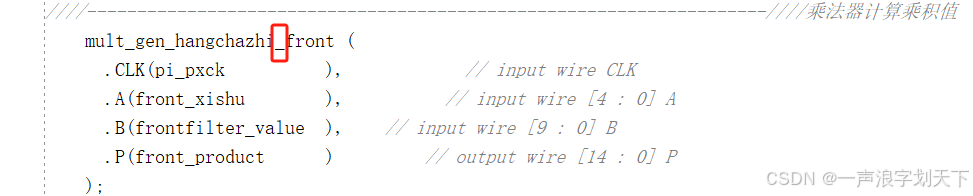

11.ERROR: [VRFC 10-2063] Module <mult_gen_hangchazhi_front> not found while processing module instance <'Undefined'> 错误:[VRFC 10-2063]模块<mult_gen_hangchazhi_front>在处理模块实例<'Undefined'>时未找到

原因:调用fifo取名字时不能有下划线

办法:删去下划线

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)