【FPGA】vivado使用(led流水灯实例,附图,详细)

整理时间:2021-03-08前言:FPGA具备并行处理的特点,在图像处理行业应用很广。对于一个好的图像处理工程师来说,既能看得懂论文,搞得了算法,又能够把自己设计的算法在FPGA平台上实施出来,这很必要。工欲善其事必先利其器。FPGA型号:XC7Z020-CLG400vivado版本:2019.1安装好vivado开发工具,拥有了FPGA开发硬件平台。开搞~本文目录:1.建立工程2.添加文件-2

整理时间:2021-03-08

前言:

FPGA型号:XC7Z020-CLG400

vivado版本:2019.1

安装好vivado开发工具,拥有了FPGA开发硬件平台。

本文目录:

1.建立工程

2.添加文件

-2.1 添加.v文件

-2.2 添加约束xdc文件

3. 综合

4. 烧写

-4.1 烧写bit 文件

-4.2 烧写mcs文件

正文:

本文通过一个简单的“流水灯”案例,旨在了解整个开发流程。

步骤如下:

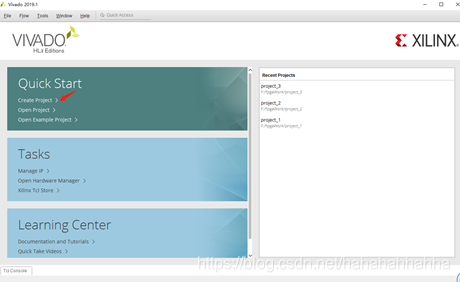

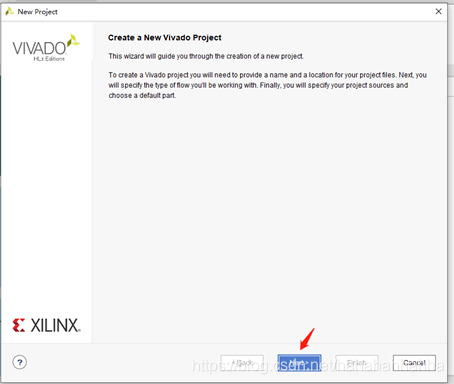

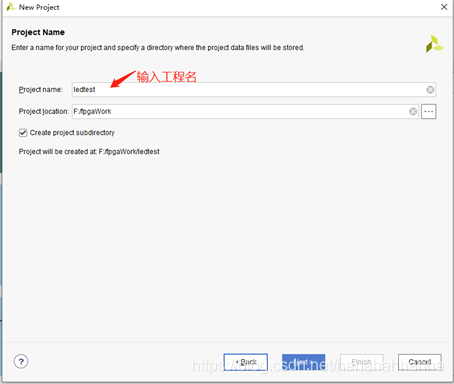

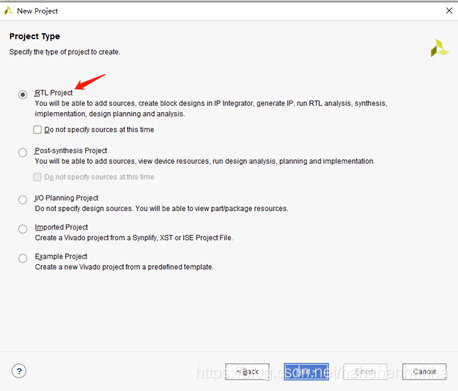

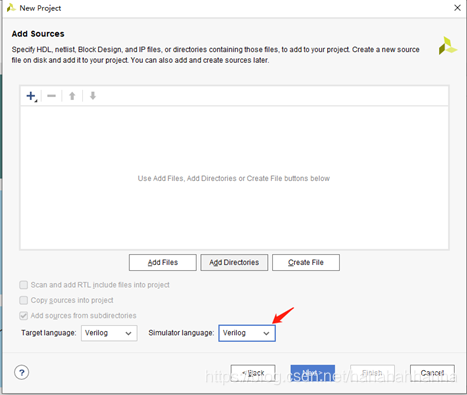

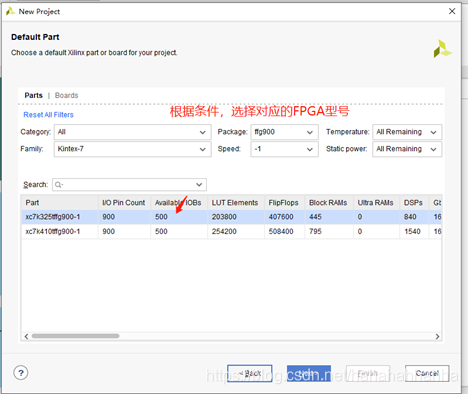

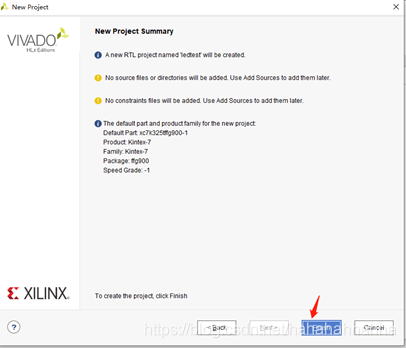

1.建立工程

*

*

*

*

*

*

*

2.添加文件

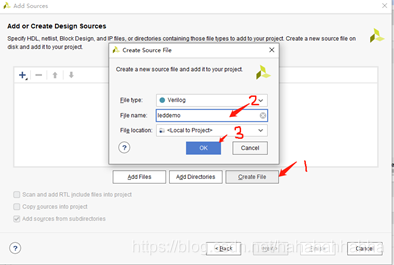

-2.1 添加.v文件

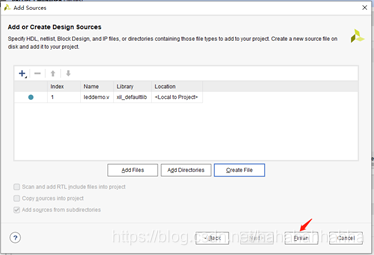

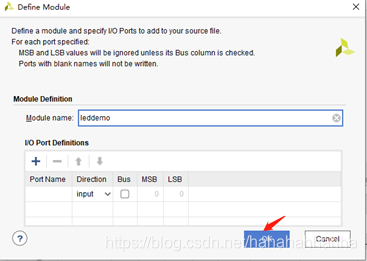

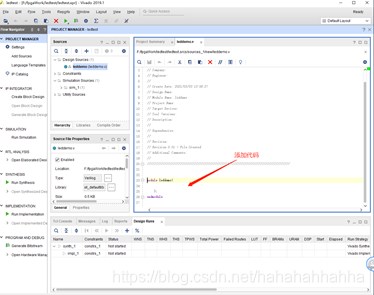

添加source design文件(设计文件)

*

*

*

代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

module run_led(

input CLK_i,

input RSTn_i,

output [3:0]LED_o

);

reg [3:0]LED_o;

reg [31:0]Cnt;

always @(posedge CLK_i )

if (!RSTn_i)//复位

begin

LED_o<=4'b1;

end

else

begin

if (Cnt==32'd5000_000_000)

begin

Cnt<=32'd0;

if(LED_o==4'b1000)

begin

LED_o<=4'b0001;

end

else

begin

LED_o<=LED_o<<1'b1;

end

end

else

begin

LED_o<=LED_o;

end

end

endmodule

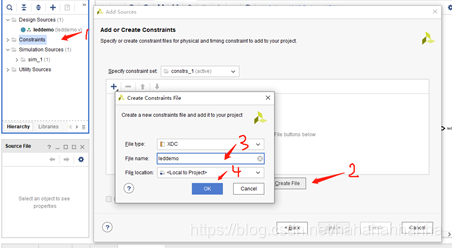

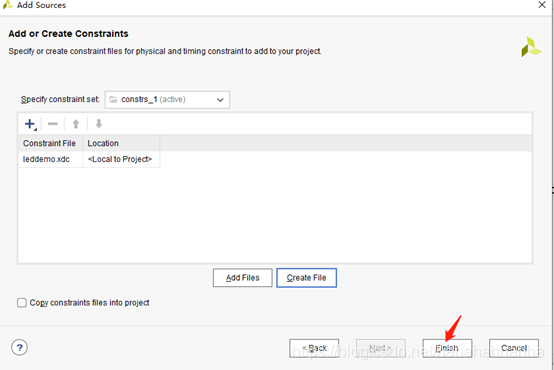

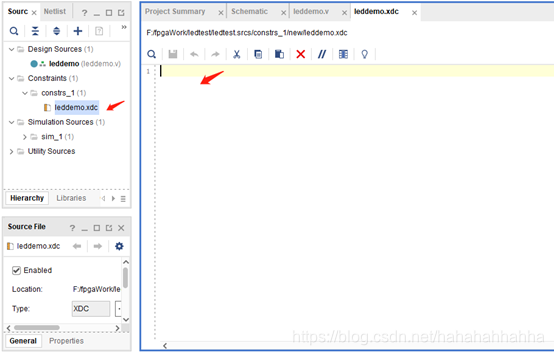

-2.2 添加约束xdc文件

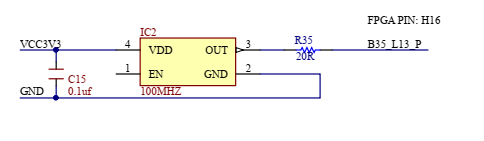

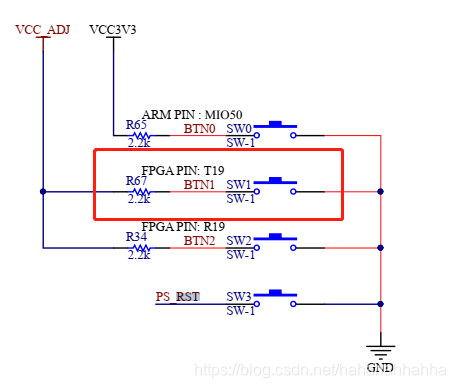

上述代码中,对应FPGA硬件6个管脚。具体对应哪个管脚需要在硬件原理图中确认好。

时钟clk管脚

复位rst_n管脚

随便选择1个复位按键

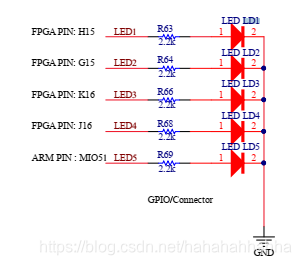

led管脚

*

*

*

约束文件如下:

#vivado管脚约束XDC文件

#FPGA_CLK

set_property PACKAGE_PIN H16 [get_ports CLK_i]

set_property IOSTANDARD LVCMOS33 [get_ports CLK_i]

#rst_n

set_property PACKAGE_PIN T19 [get_ports RSTn_i]

set_property IOSTANDARD LVCMOS33 [get_ports RSTn_i]

#LED_o

set_property PACKAGE_PIN J16 [get_ports {LED_o[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[3]}]

set_property PACKAGE_PIN K16 [get_ports {LED_o[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[2]}]

set_property PACKAGE_PIN G15 [get_ports {LED_o[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[1]}]

set_property PACKAGE_PIN H15 [get_ports {LED_o[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[0]}]

#set_property CONFIG_MODE <configuration_mode> [current_design]

set_property BITSTREAM.CENERAL.COMPRESS TRUE [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

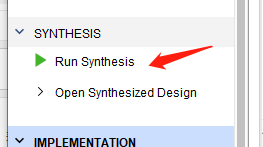

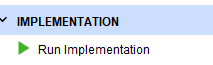

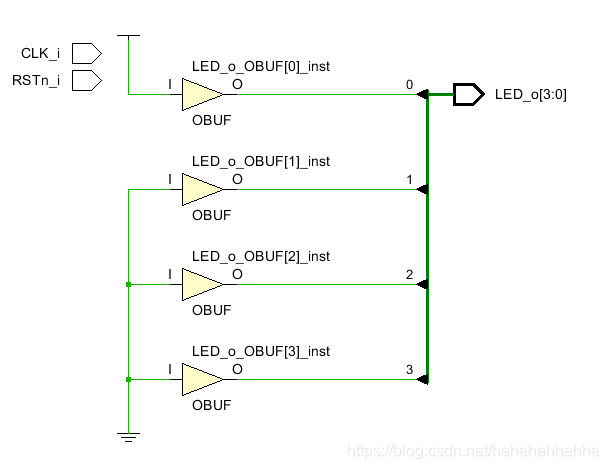

3. 综合与实现

综合:

实现:

一切顺利,结果如下:

4. 烧写至FPGA硬件

- 4.1 烧写bit 文件

bit 文件用于调试,掉电后丢失。

- 4.2 烧写mcs文件

mcs文件用于固化逻辑,将程序烧写至FPGA的配置flash中,掉电后不会丢失。

THE END~

【MATLAB-app】系列教程(含视频)00_csdn上第一套关于matlab appdesigner系列“视频课”来啦~~

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)