RK3568 PCIe调试记录

RK3568 PCIe调试记录

·

文章目录

1、环境介绍

硬件:飞凌ok3568-c开发板

软件:原厂rk356x sdk

2、RK3568 PCIe资源

RK3568有一个PCIe 2.0和一个PCIe 3.0。

- PCIe 2.0仅支持Root Complex模式。

- PCIe 3.0支持Root Complex或Endpoint模式。

- PCIe 3.0 2lane可以拆分为1+1lane。

- PCIe 3.0需要使用外置晶振。

3、飞凌ok3568开发板PCIe原理图

飞凌ok3568开发板有两个PCIe插槽,分别是一个PCIe 2.0 1lane和一个PCIe 3.0 2lane。

下图是PCIe 2.0部分原理图:

下图是PCIe 3.0 2lane部分原理图:

4、配置目标

下面将PCIe 2.0和PCIe 3.0都配置成RC模式。

5、dts配置

5.1、PCIe 2.0 RC模式

/ {

...

vcc3v3_pcie: vcc3v3-pcie {

compatible = "regulator-gpio";

regulator-name = "vcc3v3_pcie";

regulator-min-microvolt = <100000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio0 RK_PA5 GPIO_ACTIVE_HIGH>;

gpios-states = <0x1>;

states = <100000 0x0

3300000 0x1>;

};

...

}

&combphy2_psq {

status = "okay";

};

&pcie2x1 {

reset-gpios = <&gpio0 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie>;

status = "okay";

};

5.2、PCIe 3.0 2lane RC模式

/ {

...

vcc3v3_pcie: vcc3v3-pcie {

compatible = "regulator-gpio";

regulator-name = "vcc3v3_pcie";

regulator-min-microvolt = <100000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio0 RK_PA5 GPIO_ACTIVE_HIGH>;

gpios-states = <0x1>;

states = <100000 0x0

3300000 0x1>;

};

...

}

&pcie30phy {

status = "okay";

};

&pcie3x2 {

reset-gpios = <&gpio0 RK_PC6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie>;

status = "okay";

};

5.3、其它模式配置

其它模式配置可参考下图去配置:

6、验证

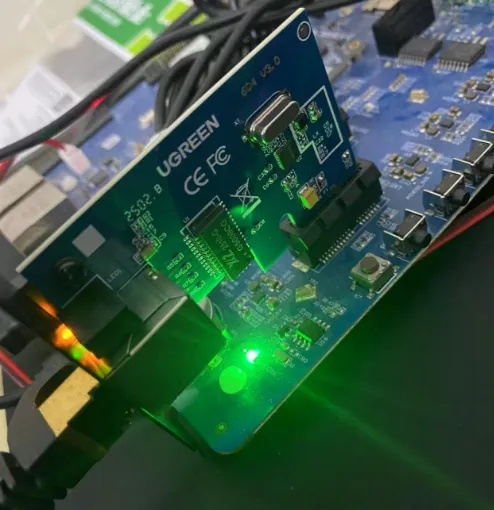

这里使用绿联PCIe有线网卡模块(rtl8168)对板卡的pcie x1接口进行验证:

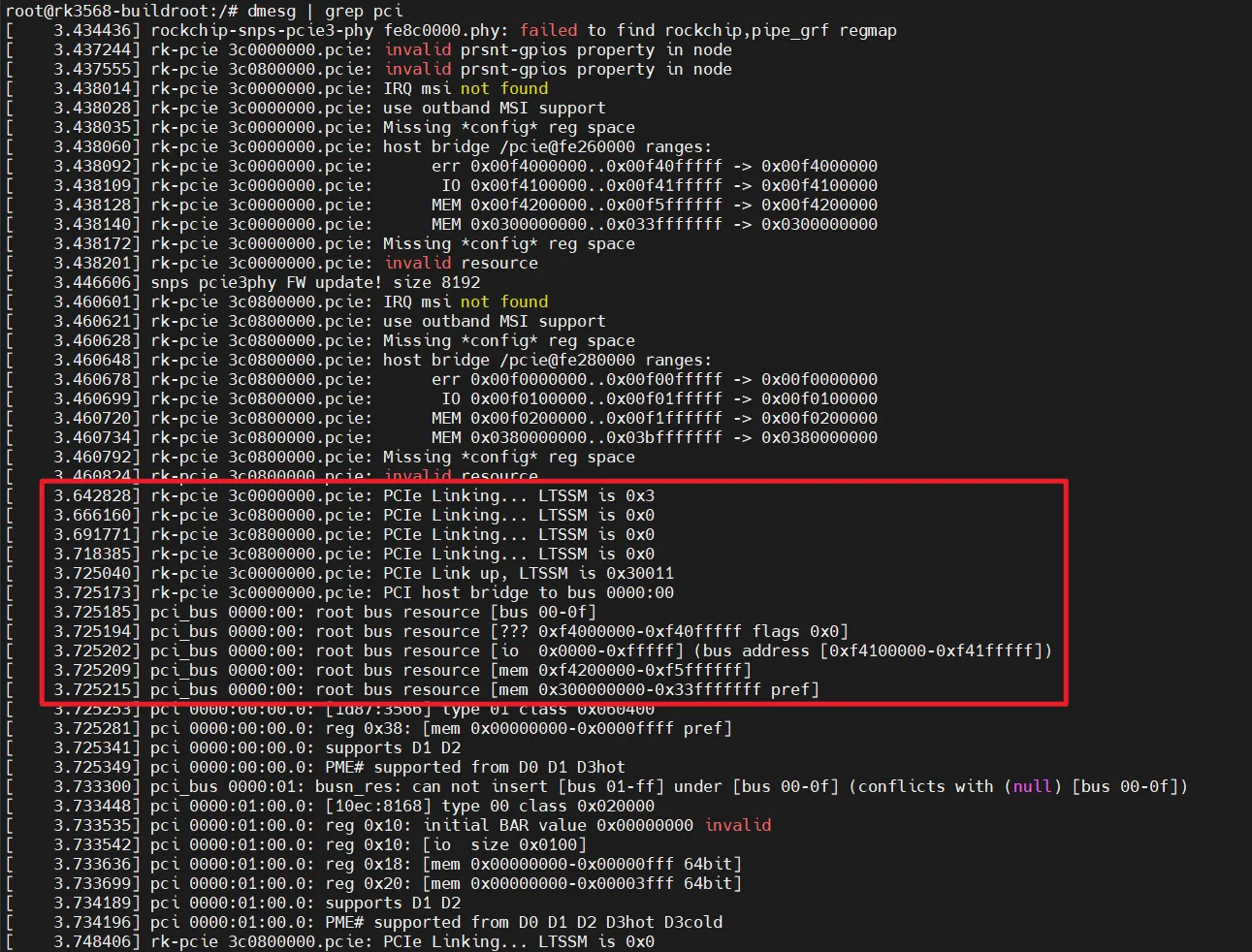

查看枚举信息:

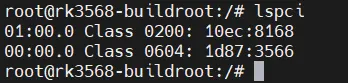

查看pci设备:

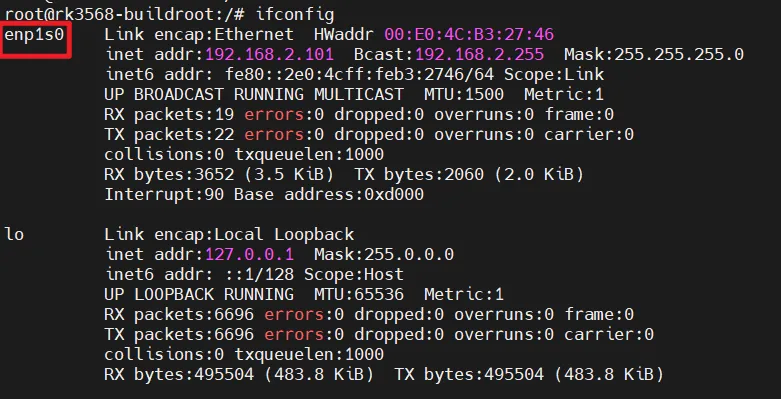

查看网卡节点:

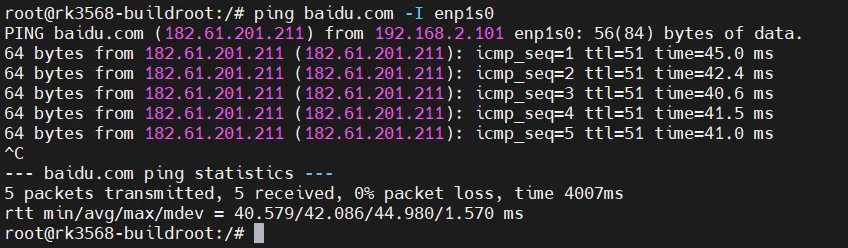

网络测试:

7、总结

嵌入式Linux学习交流群:424571391

参考文章:

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)