EMMC的单BLOCK读写TIMING时序

6.15.1Command and response指令的格式在单数据速率或双数据速率模式下,主机命令和设备响应都随主机时钟上升沿计时。设备识别和设备运行条件定时在开漏模式下处理设备标识(CMD2)和设备操作条件(CMD1)时序。设备对主机命令的响应在NID时钟周期之后开始。分配设备相对地址SET_RCA(CMD 3)也在开漏模式下处理。主机命令和设备响应之间的最小延迟是NCR时钟周期。数据传输模

说明:此文是我从手册中粘贴过来的,便于自己使用。详情参考文件JESD84-B451(eMMC-Spec-V4.5.1)

6.15.1Command and response

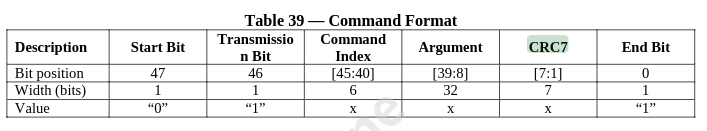

指令的格式

在单数据速率或双数据速率模式下,主机命令和设备响应都随主机时钟上升沿计时。

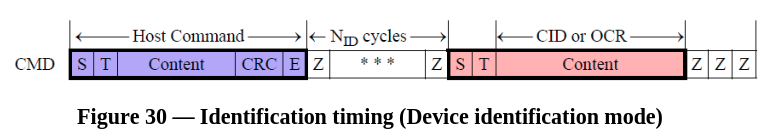

- 设备识别和设备运行条件定时

在开漏模式下处理设备标识(CMD2)和设备操作条件(CMD1)时序。设备对主机命令的响应在NID时钟周期之后开始。

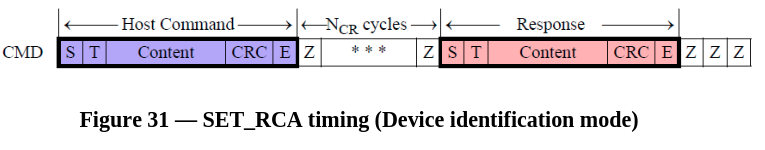

- 分配设备相对地址

SET_RCA(CMD 3)也在开漏模式下处理。主机命令和设备响应之间的最小延迟是NCR时钟周期。

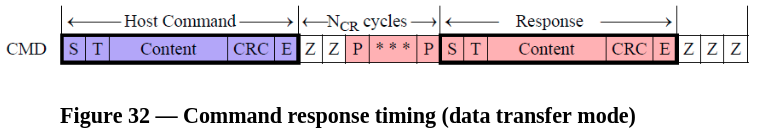

- 数据传输模式

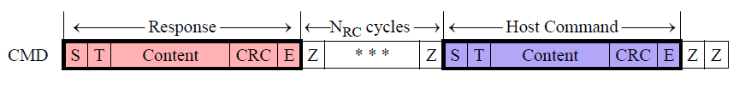

设备接收到RCA后,将切换到数据传输模式。在这种模式下,命令行由push-pull drivers驱动。命令后面是两个Z位的周期(允许在总线上切换方向的时间),然后是由响应设备向上推的P位。此时序图与除CMD1、2和3之外的所有响应的主机命令相关:

- 上次设备响应——下一个主机命令时序

在接收到最后一个设备响应之后,主机可以在至少NRC时钟周期之后开始下一个命令传输。此时序与任何主机命令相关。

6.12 响应

-

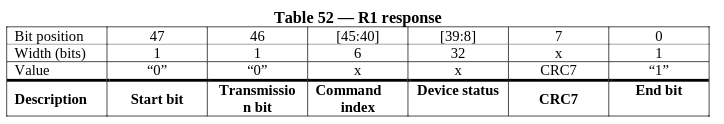

R1(正常响应命令)

code length 48 bit

-

R1b

R1b与R1相同,在数据线DAT0上传输可选的忙信号。基于在命令接收之前的状态,设备在接收到这些命令之后可能变得忙碌。有关详细说明和时序图,请参阅第6.15节。 -

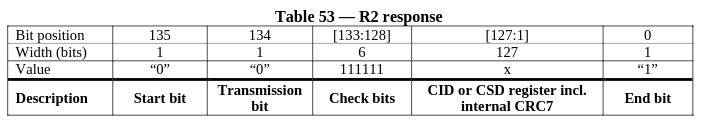

R2(CID, CSD register)

-

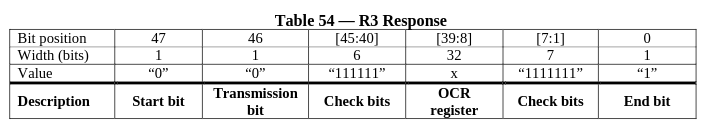

R3(OCR register)

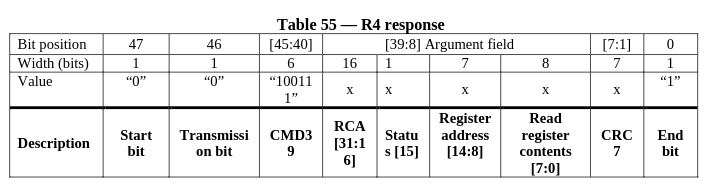

- R4 (Fast I/O)

- R5(Interrupt request)

6.15.3Data write

数据写入可以在单速率模式或双速率模式下进行。

在单数据速率模式下,数据由主机时钟输出,并由具有时钟上升沿的设备采样,每个数据线有一个CRC。在双数据速率模式下,数据通过时钟上升沿和下降沿进行时钟输出,每个数据线附加两个CRC。在这种模式下,块长度始终为512字节,字节以4位或8位宽度配置交替出现。

奇数字节(1,3,5,…,511)应由设备在时钟上升沿取样,

偶数字节(2,4,6,…,512)应由设备在时钟下降沿取样。

主机将为每个有效数据线附加两个CRC16,一个对应于设备将在时钟上升沿上采样的256奇数字节的位,另一个对应于设备将在时钟下降沿上采样的块的256偶数字节的剩余位。

- Single block write

主机通过CMD7选择要执行数据写入操作的设备。

主机通过CMD16设置面向块的数据传输的有效块长度(CMD16仅适用于单数据速率模式)。

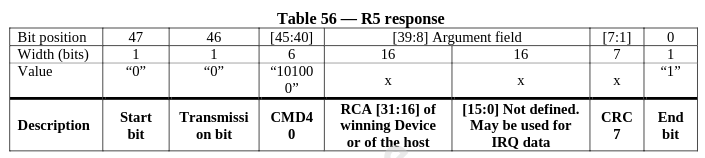

写操作的基本总线定时如图39所示。

序列从单个块写入命令(CMD24)开始,该命令确定(在参数字段中)起始地址。它像往常一样由设备在CMD行上响应。从主机传输的数据在收到设备响应后开始NWR时钟周期。

数据以CRC校验位作为后缀,以允许设备检查其传输错误。设备将CRC检查结果作为DAT0上的CRC状态令牌发回。在传输错误的情况下,发生在任何活动数据线上,设备在DAT0上发送负CRC状态(“101”)。在成功传输的情况下,通过所有活动数据线,设备在DAT0上发送正CRC状态(“010”),并启动数据编程程序。

NCRC是为HS200定义的定时参数。只有HS200设备支持NCRC。NCRC指定从写操作中数据块的结束位到CRC状态的开始位的时钟周期数。NCRC应在2到8个时钟周期之间。当设备正在编程时,它通过拉下Dat0线来指示忙碌。这种忙碌状态与编程状态直接相关。一旦设备完成编程,它就停止拉下Dat0线。

不同模式下的写数据格式

6.15.2Data read

可以在单速率模式或双速率模式下读取数据。

在单数据速率模式下,数据由设备时钟输出,并由主机利用时钟上升沿进行采样,每条数据线有一个CRC。

在双数据速率模式下,数据通过时钟上升沿和下降沿进行时钟输出,每个数据线附加两个CRC。在这种模式下,块长度始终为512字节,字节以4位或8位宽度配置交替出现。奇数字节(1,3,5。。。,511)应在时钟上升沿由主机和偶数字节(2,4,6。。。,512)由主机在时钟的下降沿进行采样。

设备将为每个有效数据线附加两个CRC16,一个对应于主机在时钟上升沿上采样的256奇数字节的位,另一个对应于主机在时钟下降沿上采样的块的256偶数字节的剩余位。

注:只有数据块和两个CRC使用时钟的两个边缘。起始位和结束位仅在时钟上升沿有效。下降沿的值不能保证。由于标准先前版本的模糊性,起始位和结束位可能对上升沿和下降沿都有效,或者只对上升沿有效。为了确保向后兼容性,该标准允许两种解释,并且不强制规定下降沿的值

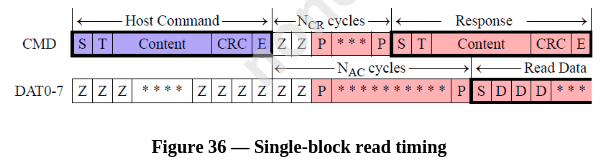

- Single block read

主机通过CMD7选择一个设备进行数据读取操作,并通过CMD16设置面向块的数据传输的有效块长度(CMD16仅适用于单数据速率模式)。

读取操作的基本总线定时如图36所示。序列从单个块读取命令(CMD17)开始,该命令在参数字段中指定起始地址。响应像往常一样在CMD行上发送。

在从读取命令的结束位开始的访问延时NAC之后,从设备开始数据传输。在最后一个数据位之后,CRC校验位加上后缀,以允许主机检查传输错误。

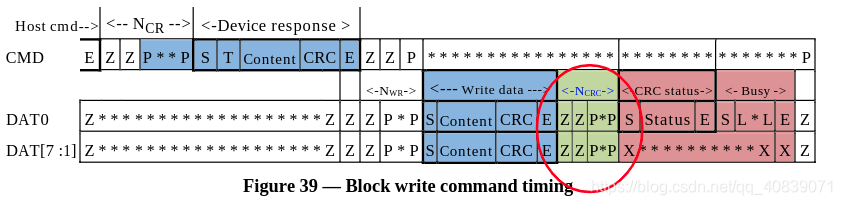

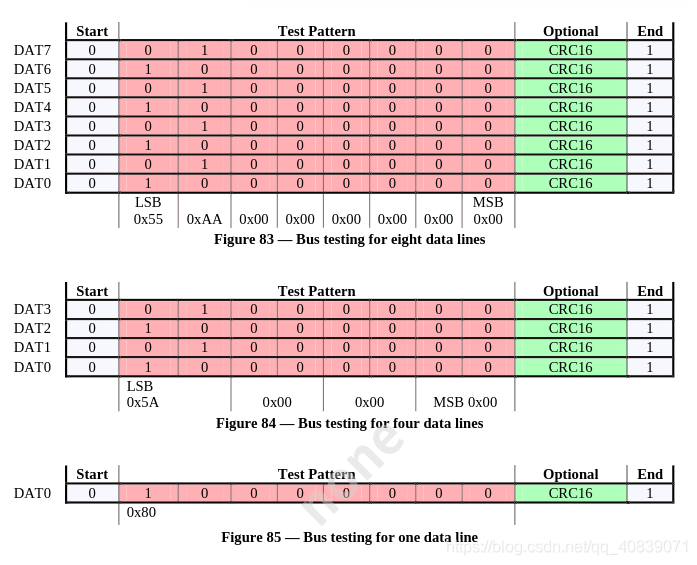

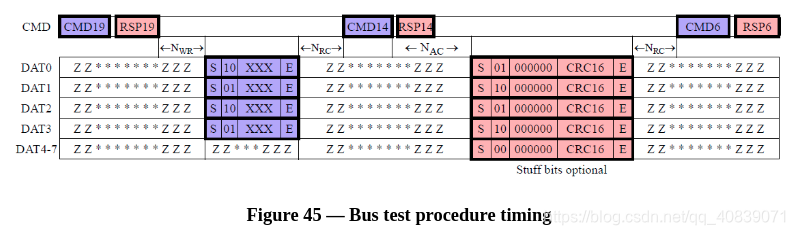

6.15.4总线测试程序时序

在单数据速率模式下达到传输状态后,主机可以启动总线测试程序。

总线测试程序在双数据速率模式下无效。

如果对主机发送的CMD19没有响应,则主机应使用CMD13从设备读取状态。

如果对CMD19没有响应,主机可能会认为设备不支持此功能。 以上时序中的参数值

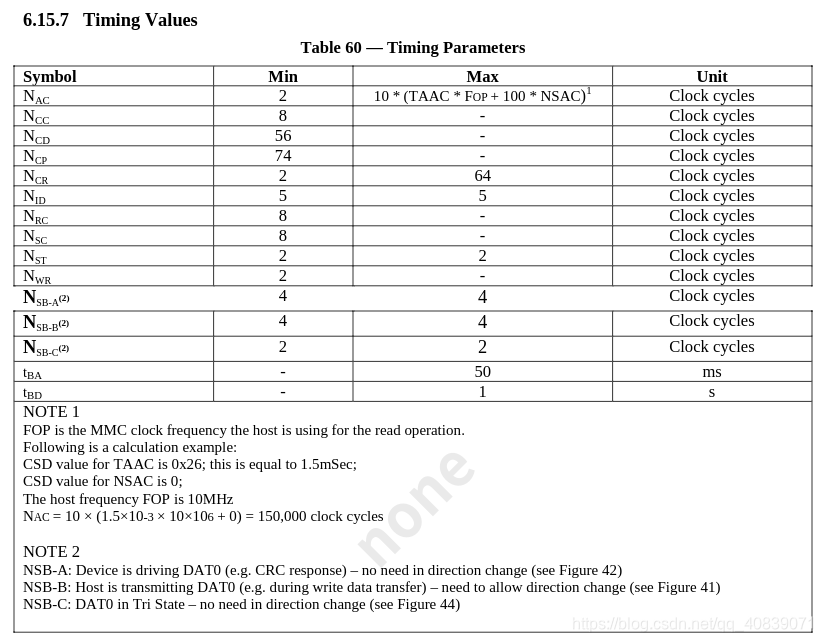

以上时序中的参数值

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)