数字IC设计流程——各环节详细介绍

数字IC设计流程各环节介绍

文章目录

前言

2023.4.4

一、确定项目需求

物理实现:制作工艺、裸片面积、封装

性能指标:功耗、速度(时钟频率)

功能指标:功能描述、接口定义

编写设计硬件设计文档(Hardware Design Specification)

二、系统级设计/架构设计

用高级建模语言(matlab、C等)对各个模块进行描述,对方案可行性进行验证

三、RTL代码编写

使用硬件描述语言对电路进行行为描述

四、功能验证/前仿/动态仿真 Pre-layout Simulation

确定RTL代码在功能上是正确,需要输入激励。没有时序信息。

常用的是VCS、NC-verilog、QuestaSim

缺点:时间长,难以覆盖全面

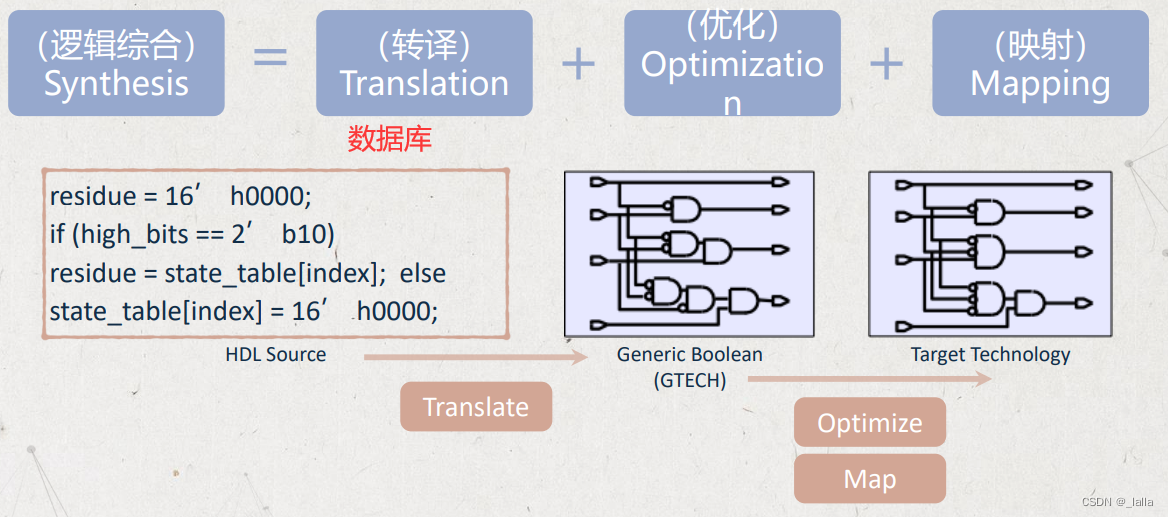

五、逻辑综合 Logic Synthesis

将RTL代码综合成特定工艺库下的网表,满足约束条件(包括时序、面积、功耗的约束)。

门级网表:标准单元的门+连线,层次比RTL要低

三个阶段:转译、优化、映射(非常重要!)

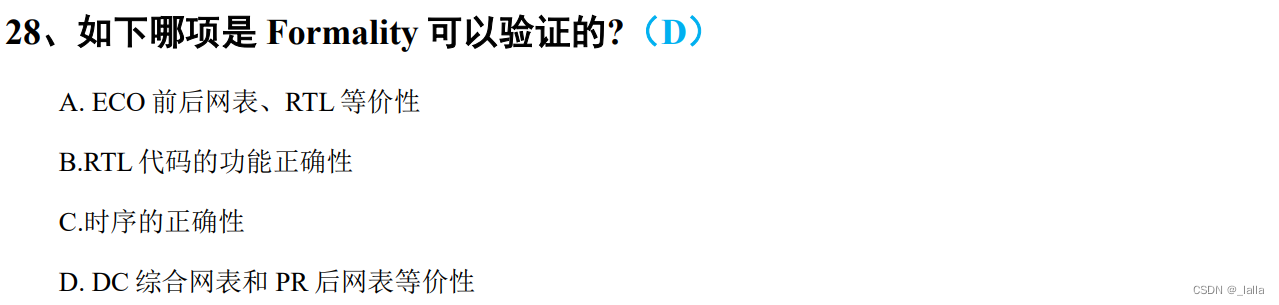

六、形式验证 Formal Verification

目的:验证RTL设计和门级网表在功能上是否一致Reference Design:标准的、逻辑功能符合要求的设计Implement Design:修改后、逻辑功能待验证的设计

一般会将其放入两个分别的container,运行verify命令,对其进行验证

formality验证流程:Guidance > Reference > Implementation > Setup > Match > Verify >Debug

应用场景:RTL代码之间、RTL代码和门级网表之间、门级网表修改前后。如逻辑综合后、布局布线后、时钟树综合(主要是对网表进行修改,就需要验证修改之后的和之前的功能是否一致)

如:使用综合网表和和布局布线后网表进行比较

综合的网表与RTL对比做形式验证。保证综合过程没有逻辑错误。保证综合后的网表正确。

A选项,ECO前的网表已经没有意义了。做ECO的时候,ECO后的网表与ECO后的RTL做形式验证。(ECO当芯片已经流片出去了,工厂只做了一个底层,但金属层还没做可以做metalECO,发现某些容易修的bug后可以利用一些冗余的cell改变某些连线来修掉这个Bug,修改后端网表的同时对RTL也进行相应修改,然后将这两个文件进行LEC比较)

1、相比于动态仿真的优点

- 不需要输入测试变量,根据电路结构来判断两个设计在逻辑功能上是否相同

- 速度比较快

- 覆盖率100%

- 纯逻辑上的验证,不要timing和物理信息

2、缺点

- 由于不考虑timing,所以需要和STA配合

七、静态时序分析 STA

对时序进行分析,穷尽所有路径,找到路径上的延迟,看是否满足建立时间、保持时间的要求。

八、可测性设计 DFT

基本思想:通过插入扫描链,增加电路内部节点的可控性和可观测性,以达到提高测试效率的目的。一般在逻辑综合或物理综合后进行扫描电路的插入和优化,布局布线之前。

九、布局布线 Place and Route

先布普通信号线,再进行时钟树综合(Clock Tree Synthesis,CTS)

十、寄生参数提取 Parasitic Extraction

提取版图上内部互连所产生的寄生电容和寄生电阻值,用于后面做STA和后仿

十一、后仿 Post-layout Simulation

也叫做门级仿真,时序仿真。验证网表在逻辑和功能上是否正确,一般使用SDF(标准延时文件)

十二、版图物理验证

DRC:设计规则检查,检查连线间距、线宽是否满足工艺要求,用来保证良率LVS:版图和逻辑综合之后的网表进行对比验证,确保最后的网表和之前电路结构是一直的ERC:电气规则检查,检查短路和开路等电气规则违例

十三、流片

生成GDSII文件,交给Foundry

ECO

ECO修改,Engineering Change Order,在设计的最后阶段发现时序或逻辑问题,需要对小范围内进行修改和重新布线,不影响芯片其他部分,其他部分的时序信息也没变。

测试题

1、前仿和后仿是什么,有什么区别?

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)