HFSS NFC 13.56MHz 天线仿真(6)- 并联匹配电路

1

·

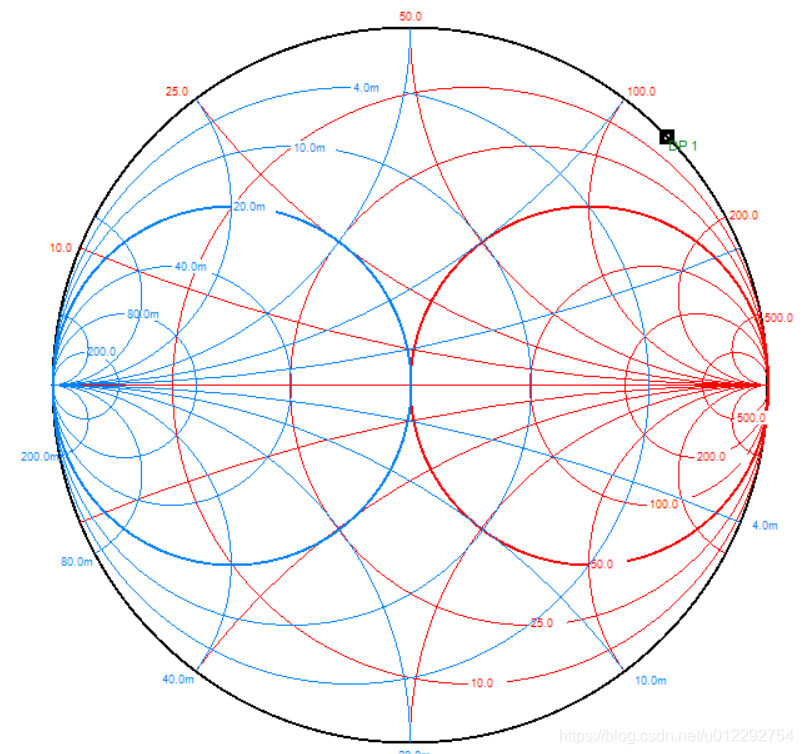

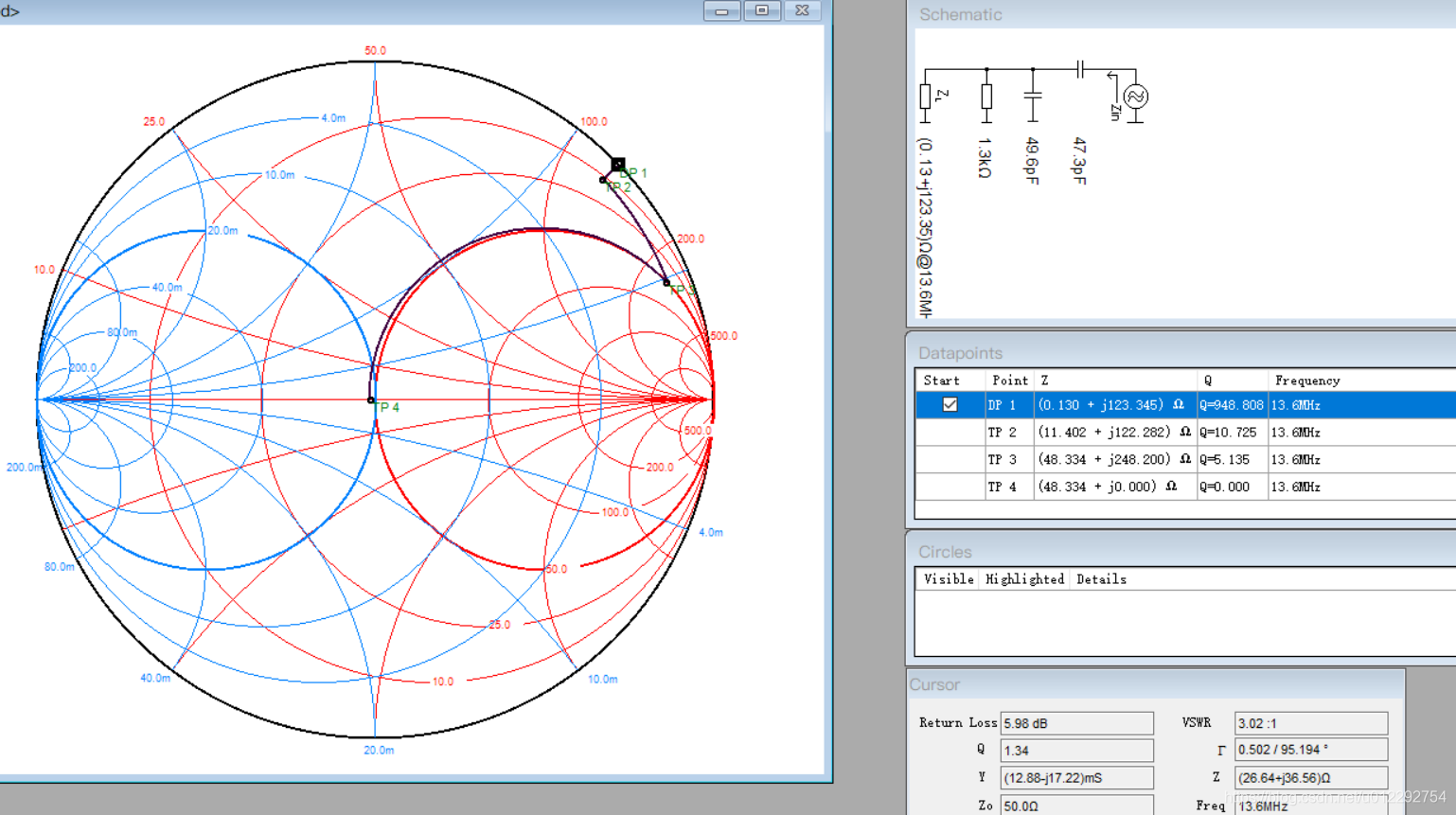

1 并联匹配电路

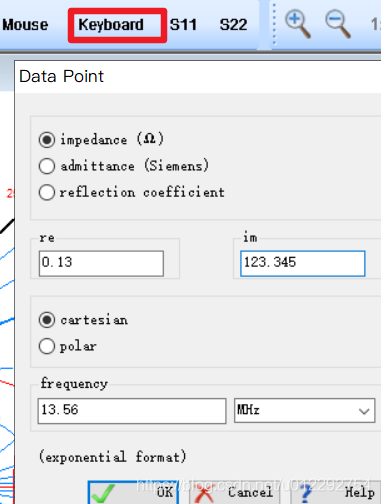

- 13.56 MHz 时, 阻抗

R = 0.13 + 123.345 i

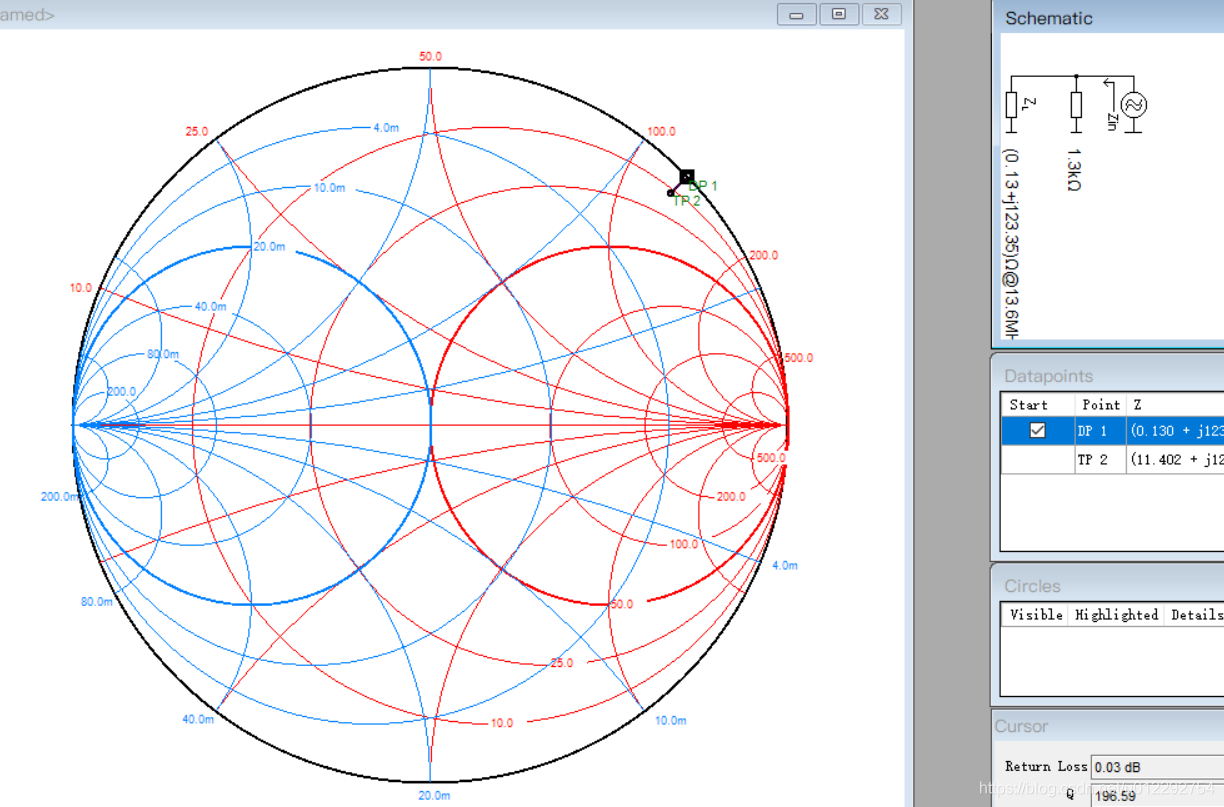

1.1 并联 1.3 k 电阻

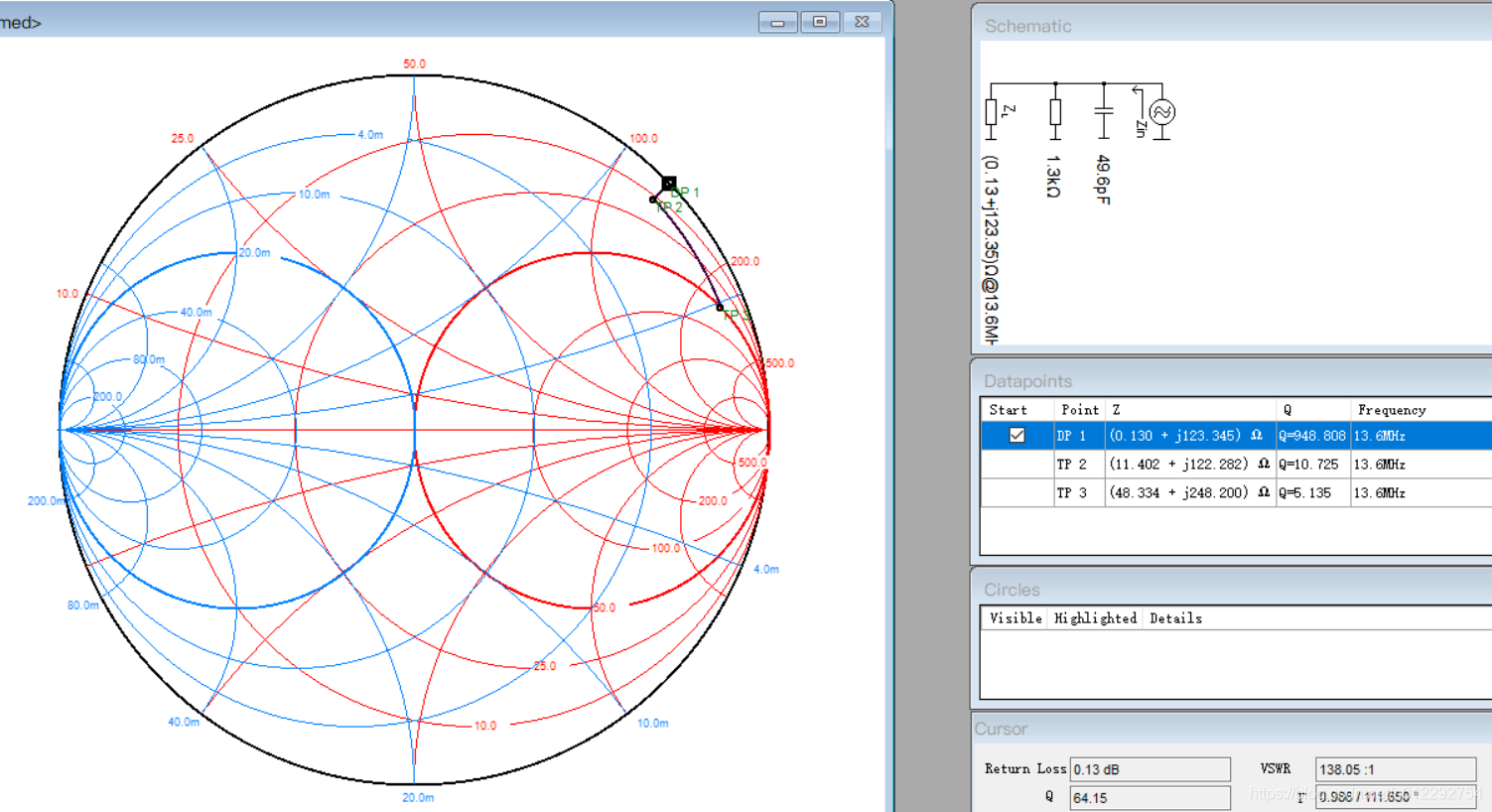

1.2 并联电容

- 把阻抗点移动到 50 欧姆的等电阻圆上

49.6 pF

1.3 串联电容

- 阻抗点移动到 50 欧姆的等电阻圆上

47.3 pF

2 HFSS 仿真并联电阻匹配

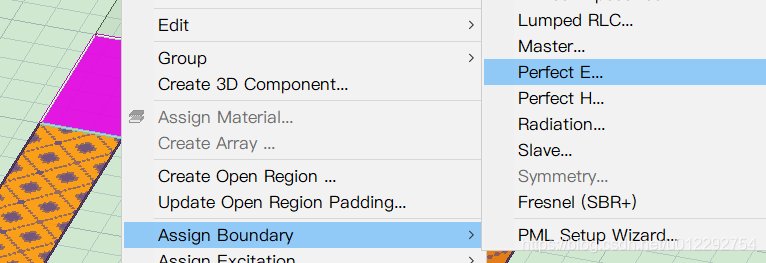

2.1 删除串联电阻边界条件,换成理想导体边界条件

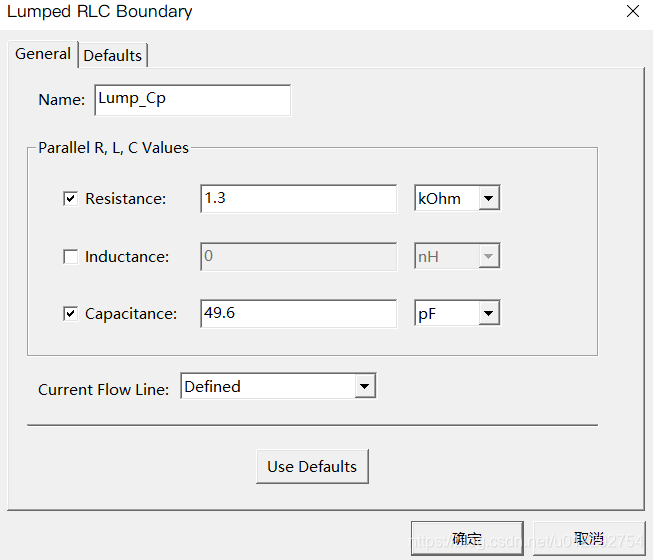

2.2 将原来的并联电阻改为电阻+电容

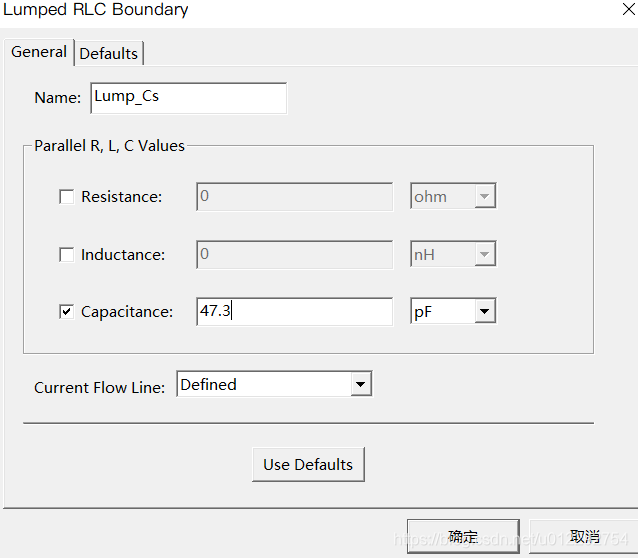

2.3 修改串联电容的容值

3 运行仿真分析

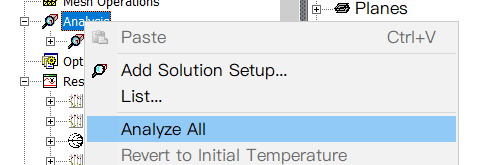

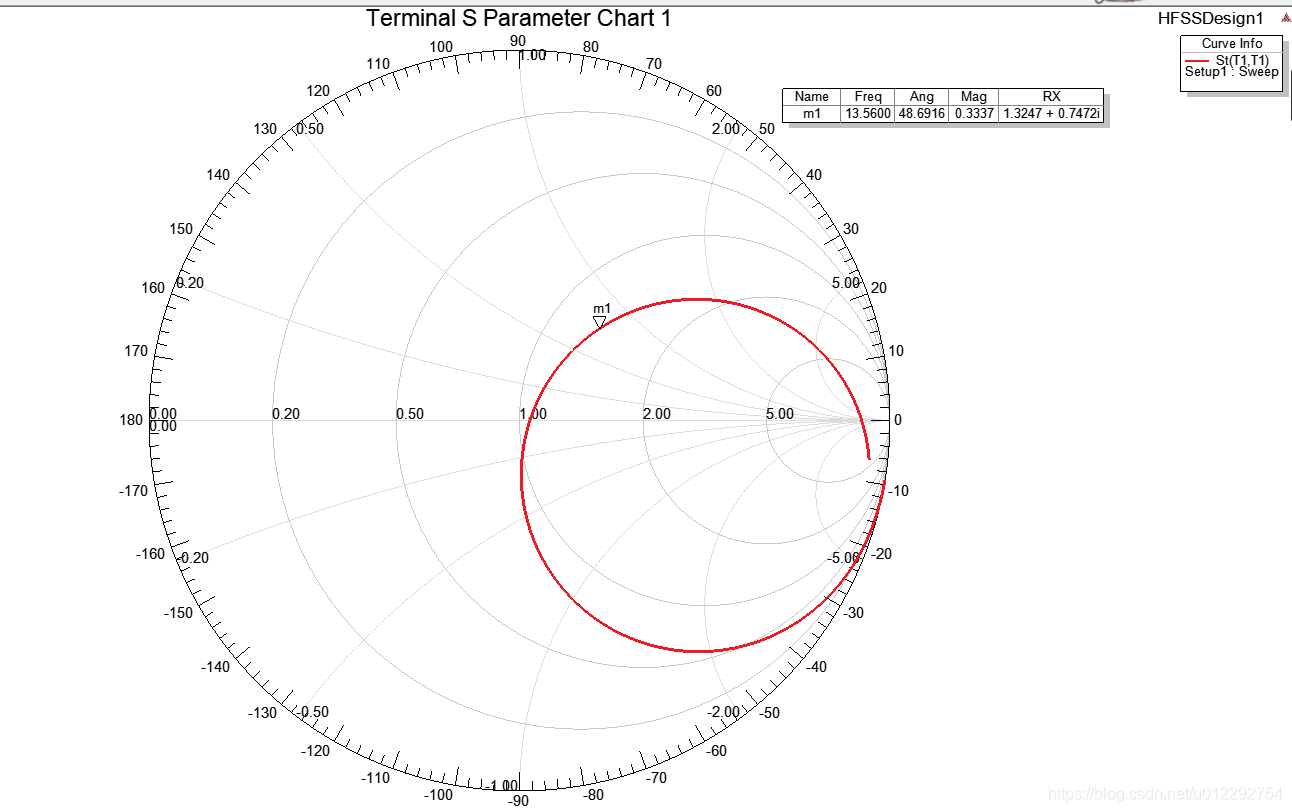

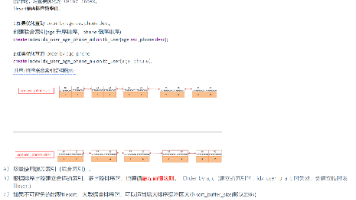

3.1 史密斯圆图

发现阻抗点在 50 欧姆等阻抗圆内部,上侧

-

内部,说明并联电容太大,适当减小并联电容,改为

43.5 pF -

上侧,说明串联电容的容值偏大,适当减小,改为

47 pF

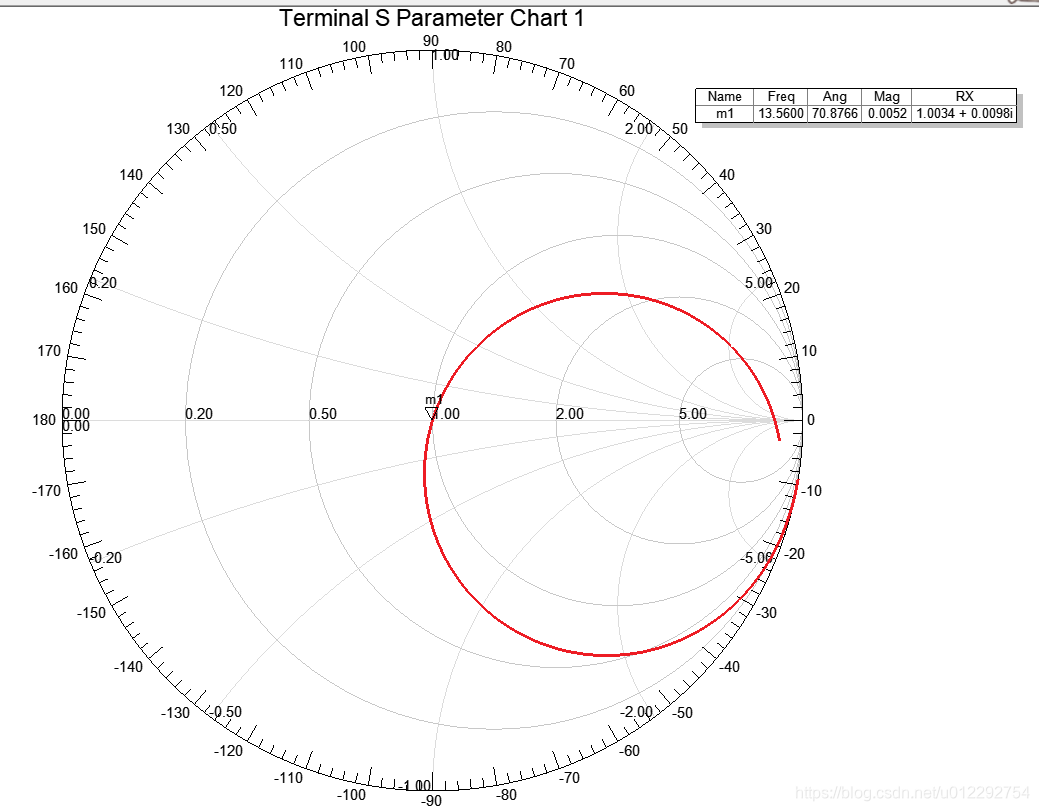

3.2 回波损耗

- 带宽

0.92 MHz

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)