RAM-IP核配置及使用

本篇文章主要介绍RAM-IP核配置及使用,RAM是random access memory的简称,即随机存储器的意思,Ram可以按照所需进行随机读/写。

ROM系列知识分类:

(1)RAM-IP核配置及使用

(2)串口发送+RAM+VGA传图

前言

本篇文章主要介绍RAM-IP核配置及使用。

一、RAM配置介绍

说到 FPGA ,不得不提的是存储器,当我们做相关项目时,经常会遇到存储数据的问题,数据量过大时,我们可以将其存储在 FPGA 芯片的外设存储器上,比如 sdram、ddr sdram、ddr3 sdram等,然而访问外设存储器相对比较麻烦,因此当数据量较小时,我们可以直接使用 FPGA 芯片内部自带的 ram 的 IP 核。

RAM是random access memory的简称,即随机存储器的意思,Ram可以按照所需进行随机读/写。我们可以通过调用FPGA内部的IP核生成一个ram,并通过编写Verilog HDL代码控制该ram。

1.进入工程,选择IP Catalog:

2.在IP Catalog界面搜索框中输入RAM,在Memories & storage Elements选项下有两种IP,一种是DRAM(Distributed Memory Generator),一种是BRAM(Block Memory Generator):

这里的DRAM并不是动态存储器,而是分布式存储器,与BRAM区别在于,DRAM通过FPGA中的查找表拼凑形成,而BRAM是FPGA中整块双口RAM资源。

这里学习BRAM的使用,双击Block Memory Generator。

Interface Type:支持AXI4 和AXI4Lite,默认为Native。

Memory Type:IP核支持生成5种类型的存储:

l Single-port RAM

l Simple Dual-port RAM

l Ture Dual-port RAM

l Single-port ROM

l Dual-port ROM

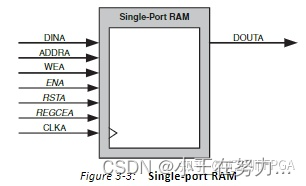

Single-port RAM(单口RAM),通过单组接口读写一块存储空间,接口如下:

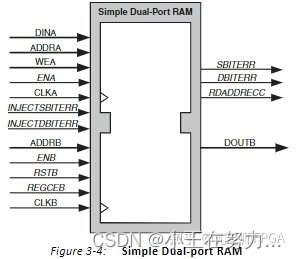

Simple Dual-port RAM(简单双口RAM),有A和B两组接口,其中A接口用来写RAM,B接口用来读RAM,接口如下:

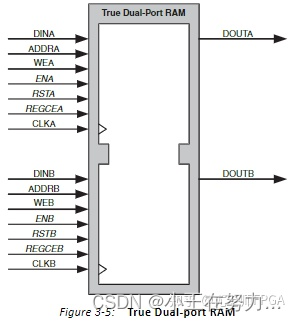

Ture Dual-port RAM(真双口RAM),有A和B两组接口,每一组接口都可以完成读和写操作,接口如下:

ECC Options:只有Simple Dual-port RAM时,该选项才可用,IP核支持内置的汉明纠错功能(Built-in Hamming Error Correction Capability(BuiltIn ECC)),且支持数据位宽小于64位的软汉明纠错(soft ECC)。

Write Enable:设置是否启用字节写入,启用时,字节位宽可选为8位(无奇偶校验位)和9位(有奇偶校验位),此时数据位宽应是字节位宽的倍数,默认情况下不启用。

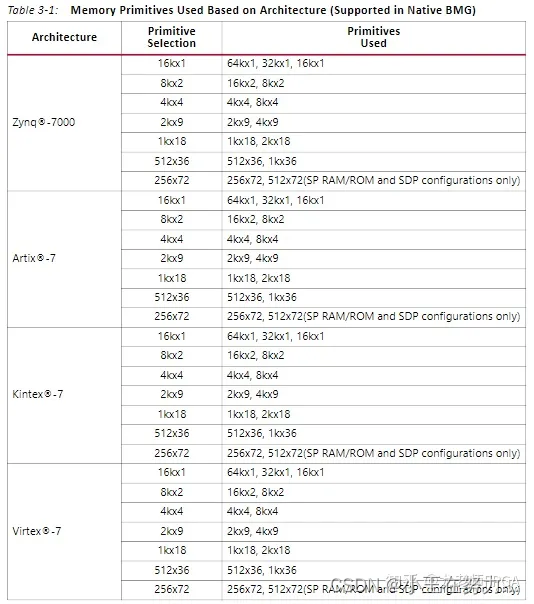

Algorithm Options:选择实现的内存算法。

Minimum Area Algorithm:使用最少数量的原语生成IP核;

Low Power Algorithm:低功耗算法,在读或写操作期间启用最小数量的块RAM原语;

Fixed Primitive Algorithm:固定单元算法,连接一个基本内存单元来生成IP核,在下拉列表中选择要使用的单元类型。

各芯片片内RAM资源如下:

这里选用Simple Dual-port RAM,其余保持默认。

xca35tfgg484-2芯片RAM容量:

由于所选型号为xca35tfgg484-2其提供50个Block RAMs 当选择写入位宽16位时根据Artix-7系列最多位2Kx18x50 = 100Kx18.

配置端口A:

Write Width:写入位宽16(RGB565)

Read Width:读出位宽,读写位宽可以不一致,IP核支持的读写位宽比例有:1:32、1:16、1:8、1:4、1:2、1:1、2:1、4:1、8:1、16:1、32:1。

Write Depth:写入深度65536(显示256x256图像)

Write Width:写入位宽16(RGB565)

配置端口B:

Read Depth:读出深度

Operating Mode:选项有Write First、Read First和No Change三种模式。

Enable Port Type:端口使能控制,可以使用ENA引脚控制,也可以选择always Enabled

Port A Optional Output Rregisters:选择是否在输出端添加寄存器

Port A Output Reset Options:配置复位信号

READ Address Change A:这个功能只在UltraScale设备上使用。

RAM写优先(Write First)时序如下,在ENA信号拉高后,在时钟上升沿检测ADDRA地址为aa,而WEA写使能为低,DOUTA就输出地址aa对应的数据;在第二个时钟上升沿,ENA为高,WEA信号为高,执行写操作,地址为bb,就将DINA上的数据1111写入存储中,并把DINA上的数据送到DOUTA上进行输出;在第三个时钟上升沿依然如此,将DINA数据写入存储同时将数据送到DOUTA上进行输出;第四个上升沿,ENA为高,WEA为低,执行读操作,地址为dd,就读取存储器地址dd中的数据送到DOUTA上进行输出。

RAM读优先时序如下:在ENA和WEA同时为高时,输出的数据是存储器存储的数据,同时,也会把新写入的数据替换掉存储器中的对应地址的数据。

RAM No Change模式:在ENA和WEA同时为高时,只进行写操作,不进行读操作,也就是说DOUTA保持前一拍数据,直到WEA为低。

Pipeline Stages within Mux:输出端Mux流水线级数

Memory Initialization:选择是否使用本地初始化.coe文件初始化存储空间。以及是否使用默认值初始化内存。

Structural/UNISIM Simulation Model Options:选择发生碰撞时由结构仿真模型生成的警告消息和输出的类型。

点击OK生成IP核。

二、RAM测试

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Create Date: 2022/12/12 17:45:28

// Module Name: RAM_TB

// Target Devices:

// Tool Versions: Vivado 2018.3

// Name:小王在努力...

//////////////////////////////////////////////////////////////////////////////////

module RAM_TB( );

reg clka,clkb;

reg ena,enb;

reg [15:0]addra,addrb;

reg [15 : 0] dina;

reg wea;

wire [15:0]doutb;

RAM RAM_LH (

.clka(clka), // input wire clka

.ena(ena), // input wire ena

.wea(wea), // input wire [0 : 0] wea

.addra(addra), // input wire [15 : 0] addra

.dina(dina), // input wire [15 : 0] dina

.clkb(clkb), // input wire clkb

.enb(enb), // input wire enb

.addrb(addrb), // input wire [15 : 0] addrb

.doutb(doutb) // output wire [15 : 0] doutb

);

initial clka = 1;

always #10 clka = ~clka;

initial clkb = 1;

always #15 clkb = ~clkb;

initial begin

ena = 0;

enb = 0;

wea = 0;

addra = 0;

addrb = 0;

dina = 0;

#201;

repeat (65536) begin

ena = 1;

wea = 1;

#20;

addra = addra +1;

dina = dina + 1;

end

ena = 0;

wea = 0;

#301;

addrb = 65536;

repeat (65536) begin

enb = 1;

#30;

addrb = addrb -1;

end

#2000;

$stop;

end

endmodule

三、仿真结果展示

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)