数字锁相环——环路滤波器参数设计

锁相环中环路滤波器参数设计方法。

😣 太难了,好像懂了,又好像没懂,梳理一下。

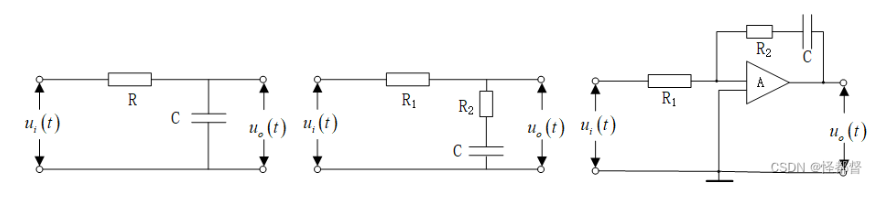

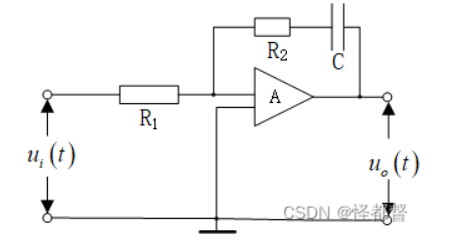

模拟环路滤波器分别有RC积分滤波器、无源比例积分滤波器、有源比例积分滤波器。

上图为有源比例积分滤波器,固有频率ωn\omega_nωn和阻尼系数ξ\xiξ,ωn\omega_nωn为ξ=0\xi=0ξ=0时的振荡频率。

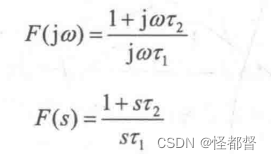

τ1=R1C\tau _1=R_1Cτ1=R1C, τ2=R2C\tau _2=R_2Cτ2=R2C ,则环路滤波器的传输函数为

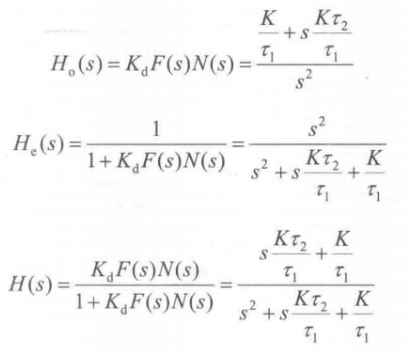

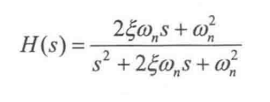

理想二阶锁相环路的传输模型为 ,其中KKK为环路增益。

令

将其带入H(s)H(s)H(s),可得

双线性变换公式为

s=2T1−z−11+z−1s=\frac{2}{T}\frac{1-z^{-1}}{1+z^{-1}}s=T21+z−11−z−1

z=1+T2s1−T2sz=\frac{1+\frac{T}{2}s}{1-\frac{T}{2}s}z=1−2Ts1+2Ts

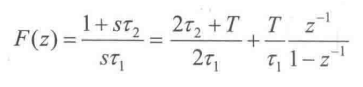

则对于理想环路积分滤波器,其数字化系统函数为

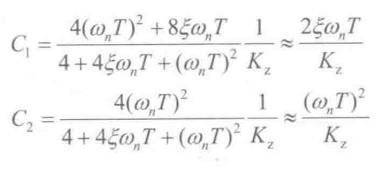

令C1、C2为

C1=2τ2+T2τ1C_1=\frac{2\tau_2+T}{2\tau_1}C1=2τ12τ2+T

C2=Tτ1C_2=\frac{T}{\tau_1}C2=τ1T

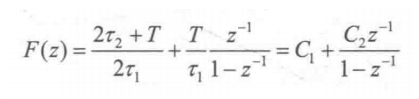

则

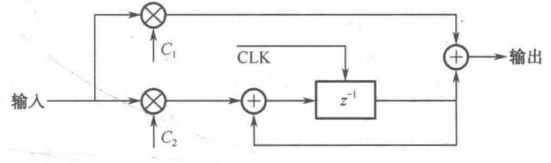

其系统结构为

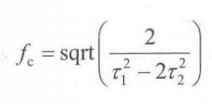

滤波器3dB截止频率与时间参数的关系关系为

模拟设计方法,若已知环路增益KKK、 阻尼系数ξ\xiξ(常取为0.707) ,取定3dB截止频率fcf_cfc,即可计算出C1C_1C1、C2C_2C2。根据C1C_1C1、C2C_2C2的值,在用Verilog实现时,可近似为移位运算。

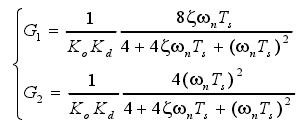

数字设计方法,利用如下公式,其中KzK_zKz为环路相位增益,TTT为系统采样周期。

以DPSK为例,码速率4MHz,采样频率32MHz,载波频率70MHz。

1.根据环路跟踪状态计算ωn\omega_nωn范围

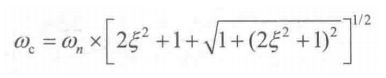

码速率ps=4p_s=4ps=4MHz,滚降系数α=0.8\alpha=0.8α=0.8,则最高频率fm=ps2+α⋅ps2f_m=\frac{p_s}{2}+\alpha \cdot \frac{p_s}{2}fm=2ps+α⋅2psMHz。ωc\omega_cωc需远小于3.6MHz,由

则ωn<<1.75MHz=11Mrad/s\omega_n<<1.75MHz=11Mrad/sωn<<1.75MHz=11Mrad/s

2.根据环路失锁门限计算ωn\omega_nωn范围

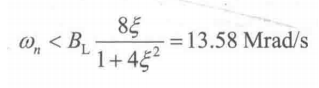

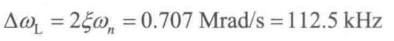

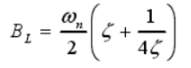

环路带宽BLB_LBL小于7.2MHz,

根据方法1和方法2,ωn\omega_nωn通常至少取最大值的1/10,则环路快捕带为

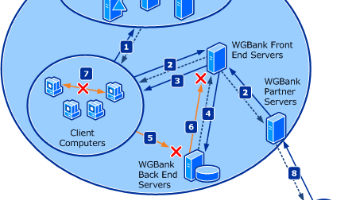

如何计算环路增益Kz=Ko⋅KdK_z=K_o\cdot K_dKz=Ko⋅Kd,其通常设计为接近于1的值,其中KoK_oKo为NCO的增益,Ko=2π2BncoK_o=\frac{2\pi}{2^{B_nco}}Ko=2Bnco2π,BncoB_ncoBnco为NCO的相位累加字位宽,KdK_dKd为下变频、低通滤波、鉴相三部分级联所产生的线性控制增益,本质上是输入到NCO的最大电压值。下变频乘法器的增益为 两路输入信号有符号数据位宽减2(因为有两个符号位),考虑到三角函数相乘产生的12\frac{1}{2}21乘法因子,故增益再除以2;低通滤波器的量化增益为其单位脉冲响应h(n)h(n)h(n)量化后最大值与量化前最大值之比;鉴相乘法器在使用符号判决时,其不贡献增益。另外环路滤波器一般设计成不贡献增益。

参考文献:锁相环技术原理及FPGA实现_杜勇

其他文献中的方法

参考文献:数字化载波同步环路算法的设计与实现_叶准

其中KoK_oKo为NCO的增益,NCO的z域传递函数为N(z)=KoZ−11−Z−1N(z)=\frac{K_oZ^{-1}}{1-Z^{-1}}N(z)=1−Z−1KoZ−1

其中KdK_dKd为数字鉴相器的增益,其为一个增益为KoK_oKo的零阶模块。

设计步骤:

- 选择锁相环的阻尼系数ξ\xiξ,常取0.707

- 根据锁相环跟踪精度以及跟踪范围的需要确定其等效噪声带宽BLB_LBL。

- 根据下式确定自由振动角频率ωn\omega_nωn。

- 由系统中A/D的电压范围、量化阶数以及NCO输出的量化幅度值计算环路增益,确定滤波器的阶数。

- 计算其他指标看是否符合要求,如果符合则设计结束,不符合则回到步骤2,直到符合要求为止。

更多推荐

已为社区贡献9条内容

已为社区贡献9条内容

所有评论(0)