set_clock_uncertainty

注意这三者是可以相互覆盖的,即如果如果一个时钟的时钟不确定度为0.5,但其定义在一个时钟不确定度为0.4端口上,则最终到达触发器的时钟引脚的时钟不确定度则为0.4;如果触发器的时钟引脚定义了一个0.3的时钟不确定度,则不论其他定义如何,这个触发器的时钟不确定度一定是0.3。可以从图中看出,定义了三个对象的时钟不确定度,t_reg/CK可以很明显看出是一个触发器的时钟引脚,而为什么会有两个clk1对

时钟不确定度(uncertainty)

可以通过set_clock_uncertainty约束来定义时钟周期的时序不确定度(uncertainty)。该约束用于建模可能影响有效时钟周期的各种因素,主要包括:

- 时钟抖动(jitter)

- 制造偏差(foundry margin)

- 工具差异(signoff margin)等

要注意的是:

- 时钟抖动仅影响建立时间检查

- 保持时间检查不受时钟抖动影响,因为其数据捕获沿和发起沿使用同一时钟边沿

set_clock_uncertainty

uncertainty [object_list]

//下面两行选项必须成对出现,每条命令最多一对

//****************************************************************************

[-from from_clock | -rise_from rise_from_clock | -fall_from fall_from_clock]

[-to to_clock | -rise_to rise_to_clock | -fall_to fall_to_clock]

//****************************************************************************

[-setup] [-hold]

//注:该命令的uncertainty参数一定要放在object_list参数前(如有) object_list:

如果对象是时钟,则不确定度会直接被指定在时钟上;如果对象是端口,则所有经过该端口的时钟会被指定时钟不确定度;如果对象是引脚,则所有经过该引脚的所有时钟会被指定时钟不确定度。注意这三者是可以相互覆盖的,即如果如果一个时钟的时钟不确定度为0.5,但其定义在一个时钟不确定度为0.4端口上,则最终到达触发器的时钟引脚的时钟不确定度则为0.4;如果触发器的时钟引脚定义了一个0.3的时钟不确定度,则不论其他定义如何,这个触发器的时钟不确定度一定是0.3。

如果指定的对象是一个组合逻辑叶单元的引脚,则该引脚所属的叶单元会被设置size only属性,确保其不会在综合过程中被优化掉(需要注意的是,此时的size_only属性是隐式设置的,这与使用set_size_only命令显式设置不同,无法使用report_attribute命令或get_attribute命令直接查看,而只能使用report_cell命令或report_size_only命令间接查看,隐式size_only属性的优先级高于显式size_only属性),使用list_size_only_types命令可以列出叶单元被设置size_only属性的原因(显式或隐式)。

下面是一些简单的使用示例。

#直接将时钟不确定度定义在时钟上

set_clock_uncertainty 0.2 [get_clocks clk1]

#将时钟不确定度定义在时钟端口上

set_clock_uncertainty 0.3 [get_ports clk1]

#将时钟不确定度定义在时钟引脚上

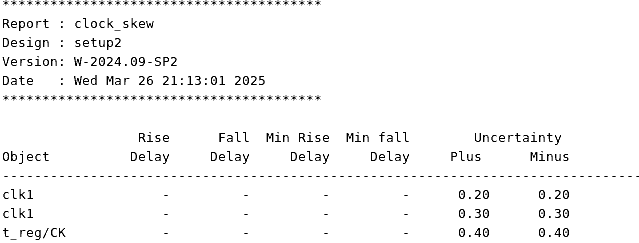

set_clock_uncertainty 0.4 [get_pins t_reg/CK]在定义了时钟不确定度后,我们可以使用report_clock -skew命令查看所有定义了的时钟不确定度,如图1所示。

可以从图中看出,定义了三个对象的时钟不确定度,t_reg/CK可以很明显看出是一个触发器的时钟引脚,而为什么会有两个clk1对象呢?其实答案很简单,这是两个同名的对象,但是其中一个是时钟本身,另一个是时钟端口。

时钟不确定度

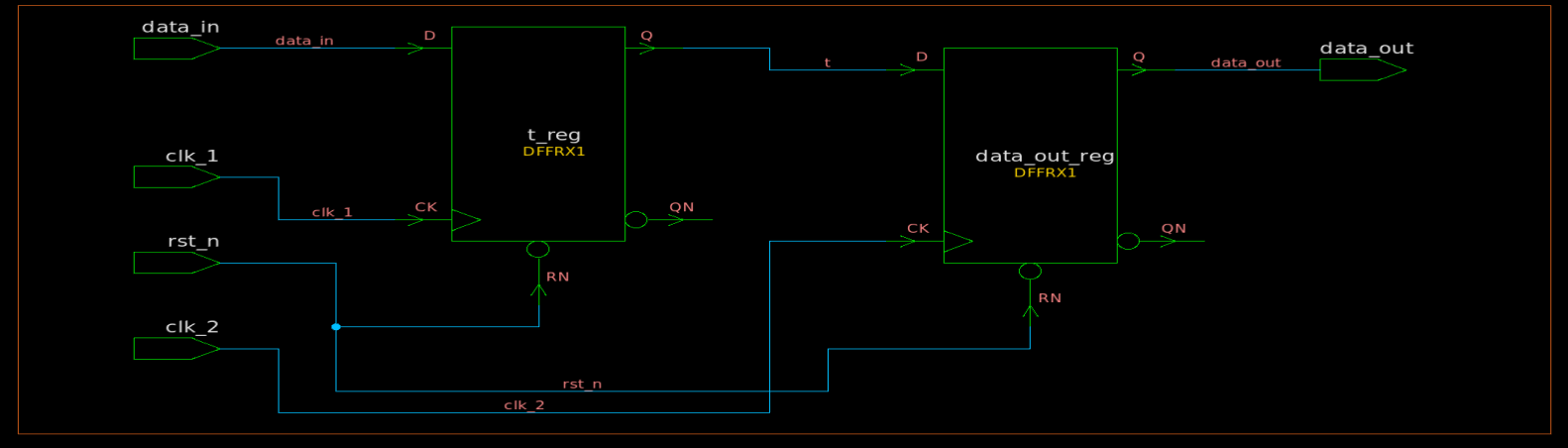

考虑两个触发器组成的简单结构,其中第一个触发器即发射触发器由clk1时钟控制,第二个触发器即捕获触发器由clk2时钟控制,有关发射触发器和捕获触发器的内容,可以看以往的文章静态时序分析:建立时间分析-CSDN博客,具体电路结构如图2所示。

现在我们只研究从t_reg的时钟端到data_out_reg的数据输入端的时序路径。首先使用下面的命令在两个时钟端口上分别创建两个时钟对象。

create_clock -period 10 -waveform {5 10} [get_ports clk1]

create_clock -period 10 -waveform {5 10} [get_ports clk2]

set_clock_uncertainty 0.1 [get_clocks clk1]

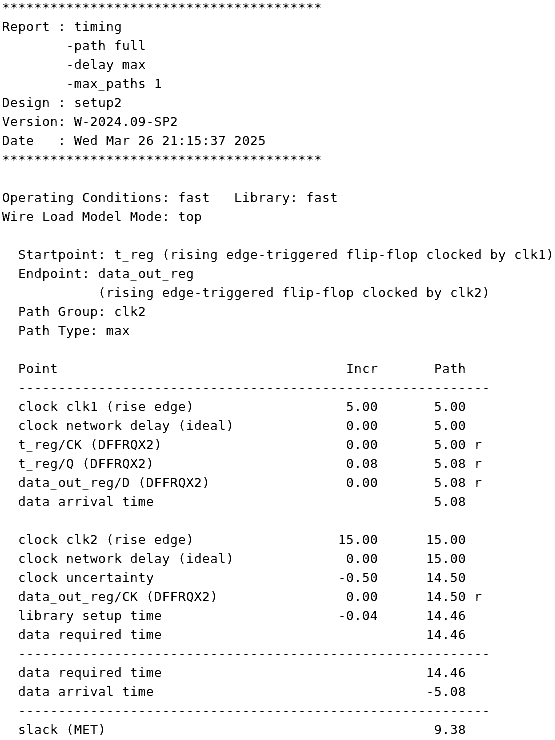

set_clock_uncertainty 0.5 [get_clocks clk2]最后我们使用report_timing命令给出建立时间时序报告,如图3所示。

从图3中可以看出,只有捕获时钟的时钟不确定度会影响相应的时序路径,而发射时钟的时钟不确定度则不会。捕获时钟clk2的时钟不确定度体现在了clock uncertainty这一项中,导致data required time减少了0.5,也就导致了最后的裕度(slack)减少了0.5

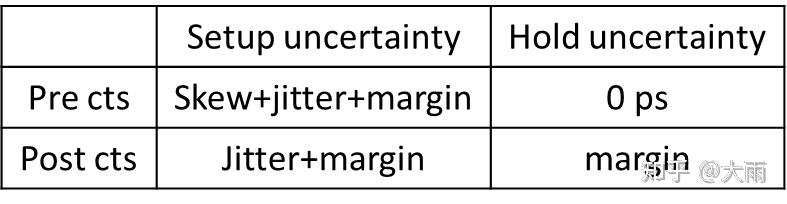

在不同设计阶段,uncertainty包含的内容有所不同:

- 时钟树综合前:工具默认时钟延迟为理想状态,uncertainty需包含时钟偏斜(skew)的影响

- 时钟树综合后:时钟延迟设置为传播(propagated)模式,工具可计算实际时钟延迟,此时uncertainty不再包含skew

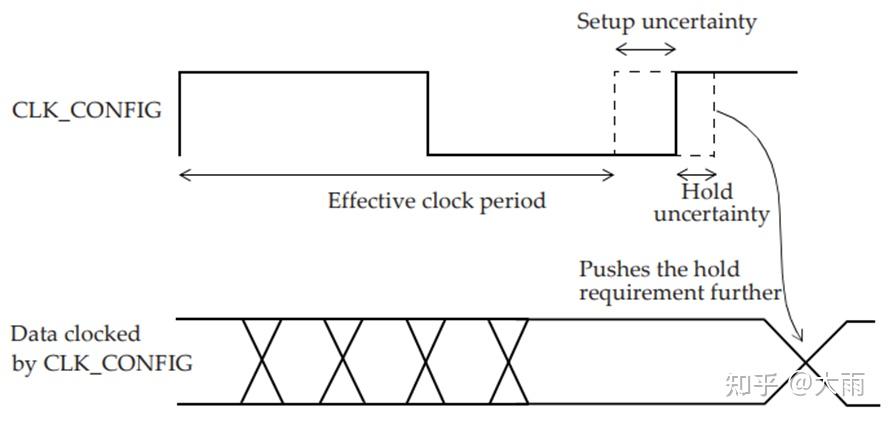

如下图所示波形,可以这么定义不确定度,因为hold不考虑jitter影响,所以-hold后面的参数比-setup后面的参数小。

- set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

- set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

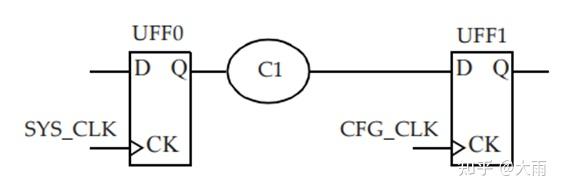

如下图所示两个不同时钟域SYS_CLK和CFG_CLK之间的路径。将100ps用作建立时间检查的不确定度,将50ps用作保持时间检查的不确定度,可以这么设置:

- set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

- set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)